IBM在ASIC设计中的电源网络噪声分析

发布时间:2010-10-11 11:54

发布者:eetech

|

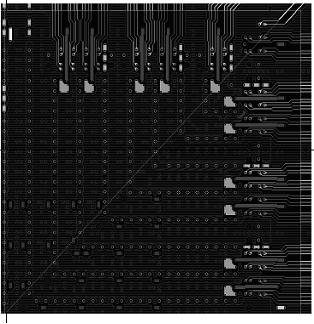

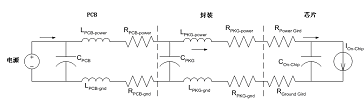

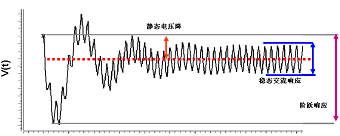

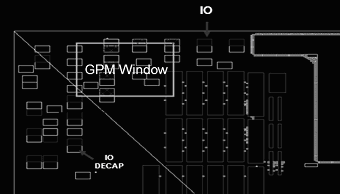

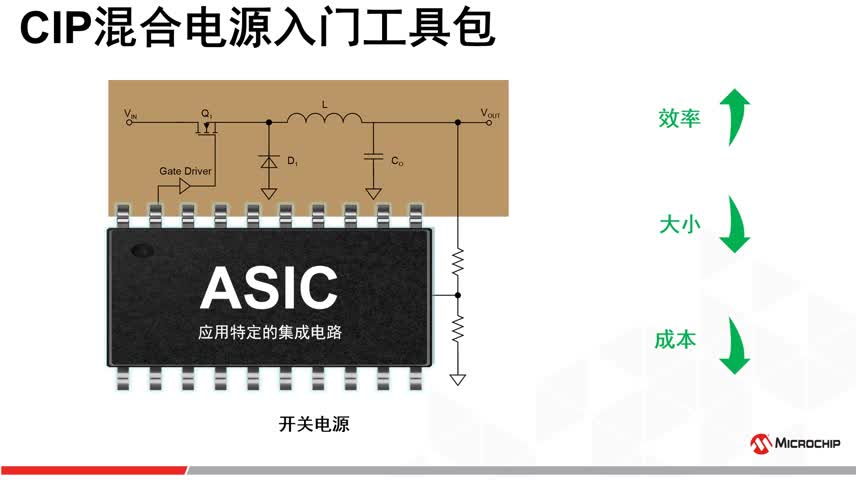

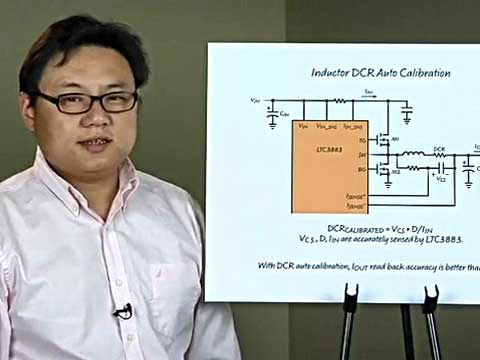

1 前言 IBM在芯片设计方面有着独特并且有效的方式,在其开展的ASIC业务中,不仅提供客户高可靠性的定制化设计方案,而且拥有科学的分析能力,即便现代的芯片开发周期不断缩减,我们还是保持着严谨的作风,提供给每一个客户高质量的产品。 本文将侧重于高速信号传输领域,介绍IBM对于PowerNoise分析的一些基本思路。众所周知,目前的窜行通讯接口一般都工作在10GBps上下,对于发送/接受,时钟频率控制单元有着极其严苛的电气要求,随之而来的就是更近一步的对芯片资源规划(FloorPlan)的要求。这些由电气要求转化而来的物理约束,因各种器件而不同,往往在空间资源比较紧张的项目中互相抵触,令普通开发者进退两难。对客户不利的是,往往会有很多供应商仓促上阵,最终导致产品瑕疵,或者反复设计,验证,延误了宝贵的上市时机。 IBM的确在这方面也遇到了同样的问题,一边是紧迫的交期,一边是如何做出准确的Noise分析,特别是如何全面地进行仿真。对于后者,基于IBM强大的计算机集群,我们很早就可以让每个ASIC项目对所有Net的供电系统,进行逐个验证,而不是抽样分析。但合理的模型,合理的分析方法,的确是我们过去一段时间一直在研究的课题。以下的内容就会对这一部分,进行深入的探讨。 2 电源网络的模型及噪声的基本概念 在ASIC的设计过程中,电源网络的噪声分析是其中非常重要的环节,本节将重点介绍电源网络的模型及电源网络噪声的基本概念。 2.1 IBM芯片的电源网格 IBM的供电网格,如图1,2所示,大致上均保持着正交的排列方式,对于大部分应用模块不需定制。我们可以按不同的芯片尺寸,比较方便的得到它的通用模型。  图13D模型和powerbus格点模型  图2设计图 2.2 IBM芯片的封装模型 封装模型的主要特点集中在层叠结构和Substrate设计上,如图3,4。因为我们对每种Substrate的设计做了严格的限定,如布线风格,TraceWidth(W),CopperThickness(T),层间厚度(H),Power/Signal层别,所以无论芯片功能差异如何,我们都可以得到一个可靠的经验值来反映封装特性,比如阻抗的经验值,我们设定为50欧姆。  图3  图4 2.3 电源网络的总体模型 图5是从板级电源一直到芯片级的完整的电源网络示意图。在这个电路模型中,板级的供电电源被看作是理想电压源,板级走线,封装及芯片上的电源网格均由电阻,电容,电感组成的电路来模拟,芯片上的IP及IO由电流源模拟。 其中板级部分产生低频噪声,封装部分产生中频噪声,芯片级则产生高频噪声。  图5电源网络电路模型 2.4 电源网络噪声的概念 当芯片上的信号开始跳变时,如由0到1,电源网络的阶跃响应会如图6所示。最低电压值由芯片上的静态电容值与翻转电容值的比例决定,跳变后的谐振则为典型的LC谐振,静态电压降则是平均功率的体现,由网络中的寄生电阻导致。稳态的交流响应与工作频率相关,其波动的电压值随着工作频率的增加而减小。  图6电源网络阶跃响应 3 IBM芯片的电源网络噪声分析 3.1 噪声分析的流程 图7为电源瞬态噪声分析的基本流程,列述了各主要阶段的工作重点。  图7噪声分析流程 对于ASIC,抑制噪声有两种主要的方法:合理布局,以及增加去耦电容。 1.对于合理布局,有很多需要遵守的规则,除了IBM应用文档中的基本方法,也要注意不同电路的噪声要求。一般需要考虑到的因素有:噪声源,受害源和翻转率。如图8,对于SRAM阵列,虽然供电网络是相对均匀的结构,但由于等效电阻,背景电容不同,同一个IP在整个芯片摆放的位置不同也会产生不同的噪声。 2.对于增加去耦电容,工具可以自动根据电路的种类,负载,工作频率,确定的去耦电容数目以及摆放位置,也可以手动,根据噪声目标,以一定算法用递归的方式确定去耦电容数量。以SRAM群为例,将会根据其工作频率,翻转率,以及端口所在的位置分配去耦电容。 这种方法的缺点是过多的去藕电容会导致芯片内布线困难。  图8布局示意图 供电网路噪声分析不仅包含工具分析的过程,也包含着前期的预防。在预防过程中,除了工程师自身的经验,IBM也应用了审查表格这一形式,集成了诸多经验和注意事项,进一步确保设计的顺利进行,如PINT和NTFR。 1.PINT会议:项目的早期,芯片的布局的过程中,会面临噪声抑制和性能折衷的问题。PINT会议就以审查表格的形式,对基本的ASIC内容,噪声影响,应用方式,布局进行讨论。审查过程中,将会强调某些可能会影响布局的特定的区域或者敏感IP,提供如何摆放去耦电容的建议,以及定位一些需要引起注意的噪声受害者和攻击者。这些具体设计前的评估,使得芯片设计工程师在早期布局的时候就能提高对噪声问题的关注,对于即将产生的设计风险提前采取措施。 2.NTFR会议:项目的中期,基本布局确定并进行了初步噪声分析后,NTFR会议将会关注更为细节的部分,特别对于高速接口电路的摆放位置,时序分析,噪声分析,将会有更加严格的要求。 布局,摆放去耦电容,噪声分析,再调整布局和去耦电容数是一个递归过程,需要根据噪声分析的结果不断调整。在IBM的各个设计阶段,由于网表的完备性不同,也都会针对每次布局或者供电网络的变化进行噪声分析。以下是我们的一些分析方法。 1.通用封装模型(GPM/WBGPM):局部的IO分析和模拟IP电路的variation确认。能够分析局部IO噪声,进行信号完整性以及时序分析,确认模拟电路供电网络噪声是否达到要求。这个仿真比较灵活,可以在设计的各个阶段进行,比如,在布局初期,可以结合客户板级要求,确定局部IO以及IO周围的敏感电路的分布,在后期,与客户的板级设计相连,完成全系统的验证。 2.Alsim_TA:是一个用于芯片的全局分析工具,引入了3维的概念,可以同时基于时间轴和空间进行噪声分析。通过它,我们可以观测到芯片的整体噪声分布,特别是可以准确捕捉到一些强噪声点,观察电源的谐振,确保元器件和去耦电容的合理放置。 运行Alsim_TA,取得准确结果的前提是Floorplan和PowerRouting必须完成。 3.频域分析(可选):作为IBMASIC噪声分析的一种方法,有助于分析并消除来自于邻近内核的噪声。 4.其它:除了上述3种方法之外,IBM还可以提供多种关于噪声分析的其它方案。例如,生成针对于系统级仿真的芯片电源模型(见图5),基于GPM的信号完整性分析,电源网络谐振分析和高频发射信号分析等。 3.2电源暂态噪声分析的主要工具-Alsim_TA ALSIM_TA主要工作在两种模式下。 1.Floorplan 可以在设计的早期来运行,为设计的布局提供指导,有效地减少Iteration. 2.FinalAnalysis 当设计已基本成型时,基于规划好的电源网络,封装的寄生参数,准确的电流波形和频率信息,这时ALSIM_TA就可以进行更为精确的噪声分析。 ALSIM_TA的分析流程可以简单归纳为以下几个步骤: 1.建立电流模型; 2.建立电源网络分布模型并简化; 3.将各模型和封装参数结合,进行暂态仿真分析。 仿真完成的输出结果可以反映动态的电源噪声,如图9所示。  图9ALSIM_TA仿真结果示意图 3.3 基于Hspice的电源噪声分析工具—GPM GPM是基于Hspice的电源噪声分析工具,相对于ALSIM_TA侧重于对整个芯片进行全局仿真,GPM更着重于分析芯片的局部噪声情况,如图10所示。   图10GPM示意图 GPM的模型可以包含封装的寄生参数,IO,去耦电容,存储器阵列还有部分逻辑。 GPM的分析流程可以简单总结为以下几个步骤: 1使用AutoGPM在芯片上自动找到IO最密集的区域,然后生成Hspice的网表。 2在网表中填入仿真所需要的参数。 3分析仿真结果,可调整电容数量来满足动态压降的要求。 4 噪声分析的实例 下面是噪声分析的实例。该项目芯片封装形式为FCBGA,最大功耗约为9.2W。主要包含的模块:串并并串转换电路(最高速率11Gps),静态存储器(最高频率155MHz),高精度频率发生器,以及各种高速IO接口电路。 图11是Alsim_TA的分析结果,针对于全局,分为VoltageCompression和Variation两部分。合理的布局和去耦电容的放置确保了每个IP的噪声容限都在相应的范围内。  图11Alsim_TA电压compression和variation图 图12为ALSIM_TA提供的具体波形图,每种IP都分别有电流和电压两种波形图。  图12ALSIM_TA中各个模块的电流电压波形图 GPM分析主要针对于局部,如图13,其仿真范围局限于GPM窗口内的多个IO,标准是尽可能对IO最密集的区域进行分析,考虑其对周边IP的最大影响,得到整个项目的WorstCase。  图13IOGPM窗口 5 总结 目前,所有IBM的ASIC客户都已经体验到了这种分析所带来的好处,确定器件规划的周期大大缩短,一些大胆的设计也可以放心尝试,尽可能的将PCB和芯片布局整合起来,实实在在的做出按自己意愿定制的芯片。 IBM作为一个国际化的公司,一直致力于帮助中国企业的发展。在AISC领域,我们已于多家国内知名企业展开了有效而长期的合作。同样,希望我们的论文能给中国的ASIC发展做出微薄的贡献。 |

网友评论