FPGA 综合工具比较

发布时间:2010-9-25 23:24

发布者:eetech

|

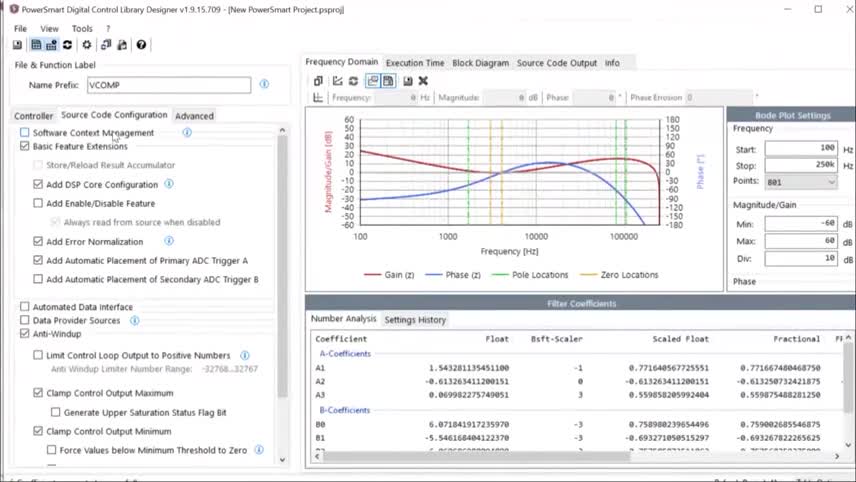

在使用FPGA做数字电路设计的流程中,综合是其中非常重要的一个步骤。同样的设计源代码,无论是VHDL或Verilog HDL,采用不同的综合工具综合会产生不同的结果。 通过使用LeonardoSpectrum Level 3,Synplify 6.0 以及 Synopsys Express 3.4三种综合工具对大小两类设计进行综合,并将综合得的网表送Quartus布局布线,分析两个步骤的结果后得到如下结论: 1.针对较小的设计(1000 LCs以下),三者综合后的结果是最高频率差别较大,但经过Quartus布局布线后的结果差别并不太大; 2.针对较大的设计(1000 LCs 以上),三者综合后的结果是最高频率差别较大,经过Quartus布局布线后的结果差别较大。 下表为结果数据:  根据上述的分析,无论对较大的或是较小的设计,采用LeonardoSpectrum Level 3综合的结果最好,相应进行布局布线的结果也最好。 另,使用LeonardoSpectrum Level 3时,某些选项的设置需要注意: 1.在选择综合策略时,选择Hierachy会提高综合后的速度; 2.在指定好器件后,在窗口Technology?Technology Setting?Wire中选择apex20e_lab_default会得到最好的综合结果; 3.在窗口Optimize?Advanced Settings中,不可选择 “Do not use wire delay during delay calculations”和 “Break combinational loops statically during timing analysis”两项。 |

网友评论