如何提高抗随机图形设计的故障覆盖率

发布时间:2016-3-30 14:41

发布者:看门狗

|

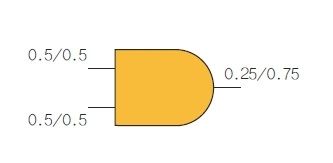

作者: AbhishekMahajan 因LBIST向量的随机本性,采用LogicBIST设计会表现出抗随机模型的趋向,从而导致低的故障覆盖范围。为解决该问题,我们借助抗随机故障分析(RRFA)方法,插入测试点。对用LBIST设计的故障检测能力的计算借助故障模拟的帮助完成,它给出了“测试质量”的估计。我们将在下面就此进行更详细的讨论,同时介绍可用来增加LBIST设计中故障检测能力的技术。 采用LogicBIST设计的故障定位 通过LBIST的测试是伪随机测试,不同于更确定性的生产扫描测试。LBIST测试中的扫描向量是由伪随机图形发生器(PRPG)生成的,PRPG用于产生伪随机序列。而在生产扫描测试中,扫描向量由自动测试设备(ATE)确定性地馈送至扫描输入。 由于LBIST测试的随机特性,因没有对哪些扫描输入在设计中被传递进行直接控制,所以并不总能测试出特定故障。当将LBIST用于在寄存器之间具有高密度组合或大的组合路径的设计时,会出现问题。这些设计可能变得对随机图形测试有抵触,在假定随机的和概率相同的输入被馈送到设计这一条件下,这意味着控制某些节点随机性地为0或1值的概率、或在一个扫描寄存器观察到某些节点的概率会降低。 以图1中的与门为例,我们计算控制该门的输出为“1”的概率。下图显示了每一个节点得到“1”或“0”值的概率。格式P(1)/ P(0)。

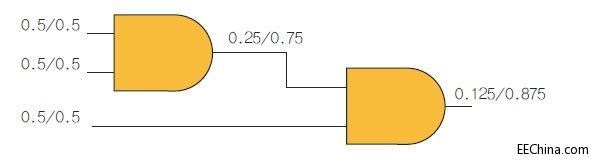

图1:2个输入和门的可控性 图2表示的是,当组合深度+1时,在不同节点得到“0”或“1”值的概率。在本组合块的输出得到“1”的概率为1/8。然而,这仍然是一个非常简单的组合块,在实际设计中,我们会看到复杂的块。因此,随着组合深度的增加,控制节点为特定值的能力在减弱。

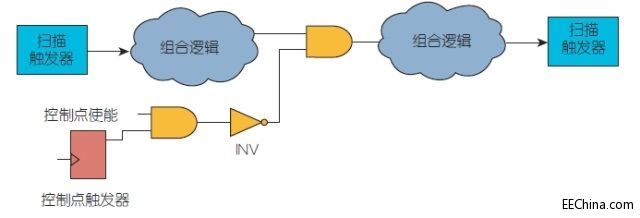

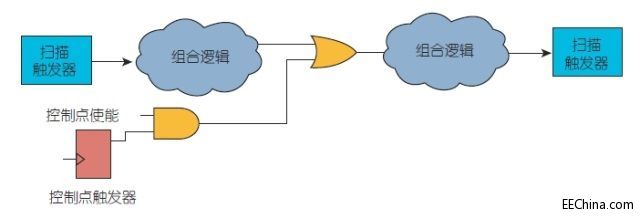

图2: 2级深度组合逻辑的可控性 当用LBIST测试时,这样的设计对随机图形表现出抵触性,并可能导致低故障覆盖率。为处理这些问题,我们经常插入点以提升设计的可测性。测试点可分为两类:控制点和观察点。 控制点增加了将某一特定节点控制为“0”或“1”值的概率。图3和图4显示了这两类控制点:其中与(AND)类控制点增加了将结点控制为“0”值的概率;而或(OR)类控制点增加了将结点控制为“1”值的概率。

图3:AND类控制点增加了为“0”值的可控性

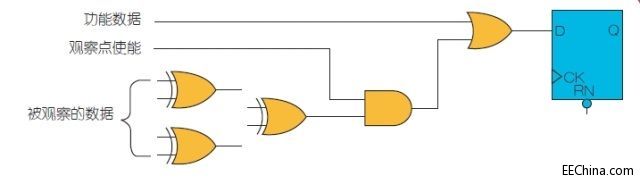

图4:OR类控制点增加了为“1”值的可控性 观察点使设计中难以观察的节点便于被某些扫描触发器观察到。当要观察设计中的多个节点时,将这些节点进行异或(XOR)处理,并馈送到扫描触发器。图5是处理这种观察点的一个示例实现。

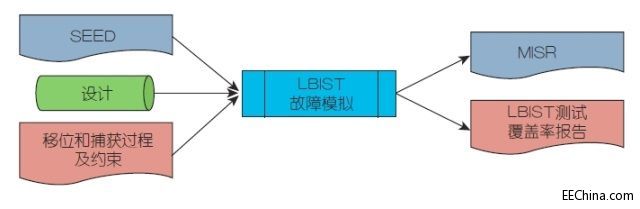

图5:观察点 测试点的鉴证采用抗随机故障分析(RRFA)方法。通过收集对小数目的随机测试图形进行故障模拟时的统计数据实现这一鉴证。电路中每个信号的可控性和可观测性的测度,由概率模型通过测量增量覆盖增益来计算并给出权重。基于对故障仿真RRFA表列出数据的分析,得出可能的候选插入测试点、并将其分为控制0/1两类,或作为观察点。 LogicBIST故障模拟 从故障检测的角度,故障模拟是一种分析电路的重要工具/方法。故障模拟仿真设计中节点的故障,以确定一组给定的测试向量可检测出哪些故障。如前所述,借助随机激励或测试向量,RRFA通过分析节点的可控性和可观测性来确定测试点插入的合适“人选”。 类似,当对设计进行LBIST插入时,我们对设计的传递和捕获流程进行故障模拟,以确定LBIST向量可覆盖哪些故障。该工作的输出是故障覆盖率报告和最终LBIST签名(MISR),它被用作设计的预期响应。可修改该故障模拟进程,以得到不同的故障覆盖率和签名。 图6显示了故障模拟流程,它指定了系统输入,给出了系统输出。改变输入的影响以及如何使用输出,前已讨论。

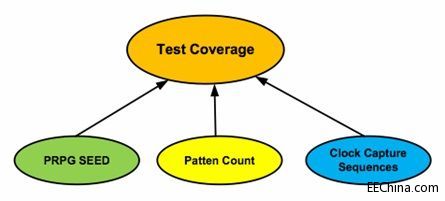

图6:故障仿真流程:输入和输出 从输入开始到故障模拟系统,我们将讨论这些输入如何对系统输出产生影响。 首先,设计应符合LBIST规约,这意味着它应该是扫描密合(scan stitched)的,并对设计中的所有X源进行标记。 X源是状态不定、不为故障模拟系统所知的逻辑。X源包括:LBIST化逻辑的非驱动输入、模拟模块输出、三态总线、时序异常等。应采用合适的X闭锁机制对这些X源进行封禁(blocked)。 系统的第二个输入是PRPG SEED(种子)值。种子值决定将以怎样的序列将移位数据馈送至设计。为找到能产生最大覆盖的最优种子值,可能要经过多次故障模拟或故障模拟引擎自身会计算最优的种子。 系统的第三个输入是限制因素和移位捕捉序列。MISR和故障检测还取决于:LBIST图形数、设计的移位长度、静态限制、施加捕获脉冲的顺序等。

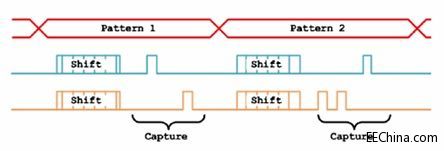

图7:影响故障覆盖率的因素 在LBIST测试期间,运行的图形越多,则检测到的故障也越多。通常,图形的数量取决于应用的用法。例如在生产测试时,在图形数量方面,我们可能没有任何硬性限制;但在现场自检时,要求器件应在一定时间内给出响应,所以应按照在最短时间达到最大覆盖率这一宗旨,对图形数进行优化。 为运行LBIST图形,故障仿真引擎需要在约束环境对设计进行设置。这些约束被送到故障模拟引擎作为某一特定的测试设置,这些设置既可是静态的、也可因模型而异。这些特定测试设置加之移位-捕获时钟序列有助于故障模拟引擎仿真设计周期并计算最终MISR。 移位和捕获序列时钟既可是硬连线的、也可是作为LBIST控制器特性可编程的。这决定了不同时钟域的脉控方式。该序列对故障检测有重要影响,因此,对其实施优化是重要的。对最大时钟域,应尝试施加最多数量的图形。增加捕捉深度的相续深度,也将增大覆盖率并有助于减少图形数。

图8:时钟移位和捕获顺序 结论 对用于军事和汽车等关键应用的器件来说,现场的LBIST测试必不可少。为在尽可能短的时间内达到最大的故障覆盖率,测试目标应严格选取。如前所述,LBIST控制器的故障检测能力决定测试质量和所需时间,它取决于诸如时钟测序、用于PRPG的种子的智能选择、添加的控制和观测点的数量等参数。为得到最大覆盖率,应对设计进行正确的分析和优化,并采用本文介绍的技术,上述应成为LBIST测试的指导原则。 参考 A new built-in TPG method for circuits with random pattern resistant faults, Kavousianos, X.; Bakalis, D.; Nikolos, D.; Tragoudas, S. ? 《一种用于抗随机模型故障电路的新型内置TPG方法》 作者:Kavousianos,X、Bakalis,D‘Nikolos,D、Tragoudas,S. -------------------------------------- M. F. Alshaibi and C. R. Kime, “MFBIST: A BIST method for random pattern resistant circuits,” in Proc. Int. Test Conf. , 1996, pp. 176–185 《MFBIST:抗随机模型电路的BIST方法》 作者:M. F. Alshaibi和C. R. Kime -------------------------------------- VLSI Test Principles and Architectures: Design for Testability Xiaoqing Wen, Laung-Terng Wang, Cheng-Wen Wu 《VLSI测试原理和体系结构:可测性设计》 作者:Xiaoqing Wen、Laung-Terng Wang、Cheng-Wen Wu -------------------------------------- Method and apparatus for programmable LBIST channel weighting Patent US6671838 《可编程LBIST通道加权的方法和设备》 美国专利US6671838 |

网友评论