复旦大学周鹏-刘春森团队实现纳秒编程闪存规模集成和8纳米极限微缩

发布时间:2024-8-14 09:55

发布者:eechina

|

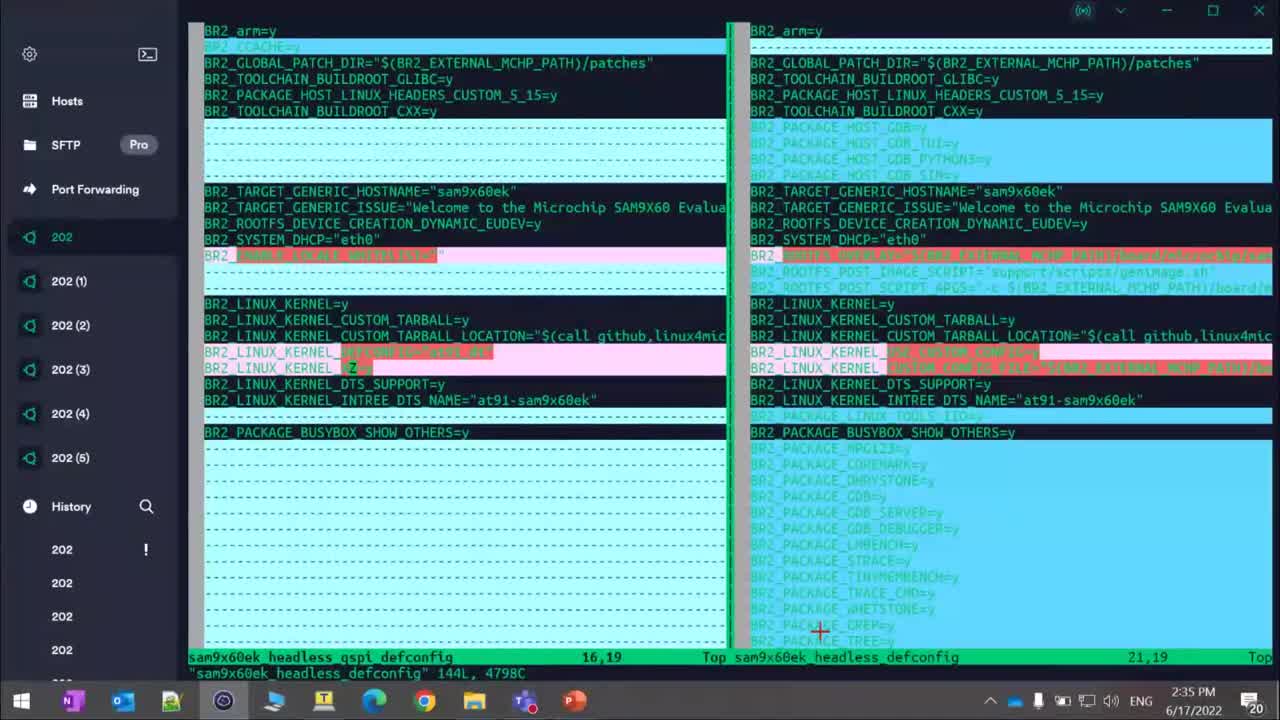

来源:复旦大学 人工智能的飞速发展迫切需要高速非易失存储技术。当前主流非易失闪存的编程速度普遍在百微秒级,无法支撑应用需求。复旦大学周鹏-刘春森团队前期研究表明二维半导体结构能够将其速度提升一千倍以上,实现颠覆性的纳秒级超快存储闪存技术。然而,如何实现规模集成、走向真正实际应用仍极具挑战。 从界面工程出发,团队在国际上首次实现了最大规模1Kb 纳秒超快闪存阵列集成验证,并证明了其超快特性可延伸至亚10纳米。北京时间8月12日下午5点,相关成果以《二维超快闪存的规模集成工艺》(“A scalable integration process for ultrafast two-dimensional flash memory”)为题发表于国际顶尖期刊《自然-电子学》(Nature Electronics)。 团队开发了超界面工程技术,在规模化二维闪存中实现了具备原子级平整度的异质界面,结合高精度的表征技术,显示集成工艺显著优于国际水平。通过严格的直流存储窗口、交流脉冲存储性能测试,证实了二维新机制闪存在1Kb存储规模中,纳秒级非易失编程速度下良率高达98%,这一良率已高于国际半导体技术路线图(International Technology Roadmap for Semiconductors)对闪存制造89.5%的良率要求。 同时,研究团队研发了不依赖先进光刻设备的自对准工艺,结合原始创新的超快存储叠层电场设计理论,成功实现了沟道长度为8纳米的超快闪存器件,是当前国际最短沟道闪存器件,并突破了硅基闪存物理尺寸极限(约15纳米)。在原子级薄层沟道支持下,这一超小尺寸器件具备20纳秒超快编程、10年非易失、十万次循环寿命和多态存储性能。本工作将极大推动超快颠覆性闪存技术的产业化应用。 复旦大学集成芯片与系统全国重点实验室、芯片与系统前沿技术研究院刘春森研究员和微电子学院周鹏教授为论文通讯作者,刘春森研究员和博士生江勇波、曹振远为论文第一作者。研究工作得到了科技部重点研发计划、基金委重要领军人才计划、上海市基础研究特区计划、上海市启明星等项目的资助,以及教育部创新平台的支持。

超快闪存集成工艺和统计性能 |

网友评论