最理想的MCU+FPGA架构

发布时间:2011-7-11 15:42

发布者:绝对好文

|

作者:特权同学 软核虽然很灵活,也很便利,但是毕竟在FPGA中有很多受限之处。性价比低是其一,性能上也不敢与同等水平的处理器相媲美。因此,各大FPGA制造商在继续降低晶圆工艺的同时,纷纷找来合作伙伴力求在嵌入硬核方面有所作为。曾经闹得沸沸扬扬的ARM联手xilinx、INTEL联手altera……只不过,这些都不是咱们这群芯片级小喽啰们正真关心的。管他什么Cortex-M0又 MIPS的,我们所关心的是到底哪个架构最实用最便利,还要“物廉价美”。 这种内嵌硬核的FPGA其实就是单片系统解决方案的最终归宿,但是话说回来,到底FPGA中潜入了什么样的硬核才算是真正的SOPC?altera一直在主推他们的软核,从号称全世界最通用的处理器NIOS II到目前正在炒作的MP32处理器;Xilinx也有软核MicroBlaze针锋相对,此外很早就有潜入IBM硬核PowerPC,现在又推出功能强大的Zynq-7000 可扩展式处理平台。但是,这些都能够满足大家的需求吗?基本上很难。在中低端应用上,北京政府力挺的国产FPGA京微雅格也适时的推出了自己的原创作品 Astro系列CSOC也曾让特权同学眼前一亮,虽然内嵌的51也能够跑到100M,只可惜其0.13us的工艺制程决定了FPGA逻辑难有大作为。

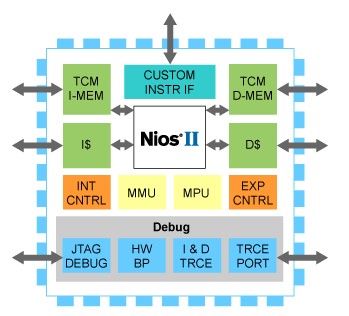

图1 NIOS II架构

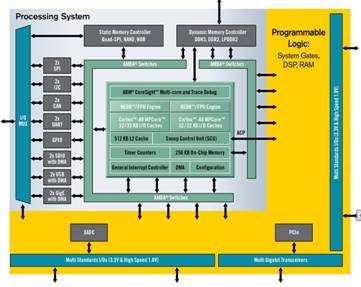

图2 Zynq-7000架构

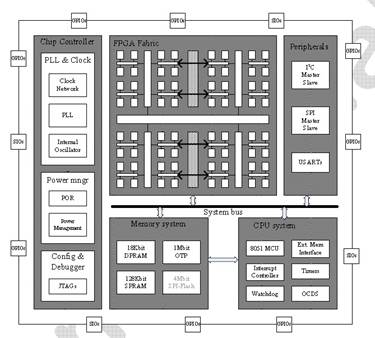

图3 Astro架构 其实,单从灵活性上来看,NIOS II绝对占上风,只可惜从某些方面比他还是拼不过硬核。性能是一方面,如果不外扩存储器,则非常受限于所应用器件的片内存储器资源。而后面二者,灵活性是有,缺什么外设直接用逻辑搭出来往总线上挂,但问题也和通用的MCU一样,集成那么些外设在大多数时候是有些浪费了,也许集成10个外设充其量只用了3、 5个,那么剩下的就是多余的,当今节约型社会这叫“浪费”。 因此,特权同学期望的架构如图4所示。不需要太丰富的外设,毕竟FPGA内嵌硬核的最大利好就是灵活性,因此我们势必可以将所谓的灵活性发挥到极致。也许这个架构简单到只要一个能够跑软件的“裸核”和必须的调试接口即可,其他所有的外设(包括最小系统运行必须的存储器接口等姑且都称作外设)都根据客户的需求自主架构。说白了,其实这成了一个“CPU+FPGA”的架构了,哈哈,这只是个人的一厢情愿,也许只是个人觉得这样的架构最适合目前手中的一揽子项目。欢迎大家一起探讨……

图4 更实用的架构 |

网友评论