由与非门构成的555定时器触发锁存电路

发布时间:2010-10-26 10:02

发布者:analog_tech

|

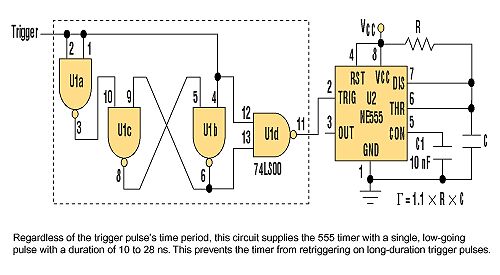

当工作在单稳态时,包括NE/SE555在内的商用集成定时器的应用有很多限制。这是因为它们不能在任一种触发脉冲条件下都可正常工作。只要输入脉冲小于设定时间周期,这些定时器就能很好工作并产生准确输出。但当输入脉冲大于定时器周期时,输出脉冲宽度就取决于输入脉冲延迟。因为某些实际应用要求定时器产生与触发输入无关的精确输出脉冲,所以定时器这种输出与输入相关的特性并满足需要。 可采用图中电路保证定时器在所有触发脉冲条件下都能正常工作。它利用逻辑器件固有的建立延迟,为555定时器提供输入触发锁存功能。对任何宽度大于10ns的输入脉冲来说,它确保定时器仅被触发一次。 该电路包括一个由与非门U1a到U1c组成的分立D型触发器。LS系列门的建立延迟约为10ns。在不考虑连接延迟的情况下,D型触发器的建立时间约为28ns。U1d利用该延迟产生单一的宽度为10到28 ns的下降沿脉冲。该脉冲对触发一次555定时器来说足够长。这样,这种方法保证同一个输入脉冲仅触发定时器一次。 请注意:该电路仅在触发输入的上升沿工作。如要求该电路提供下降沿触发,则要在触发输入端加一个反相器。

该触发锁存电路在需要将长脉冲转换为固定脉宽短脉冲的应用中有用武之地。将555定时器的输出与该电路配合使用,还能用于单刀单掷开关阵列的反跳电路。虽然该电路最初是为NE/SE555定时器设计的,它也能同工作于TTL电平的其它定时器一起使用。另外,如果用CMOS(CD4011)电路替代功能相同的TTL集成电路,该电路也能同CMOS定时器一起使用。 |

网友评论