TIP41C低频大功率平面晶体管芯片设计

发布时间:2010-7-20 23:31

发布者:conniede

|

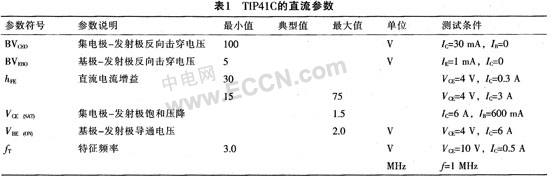

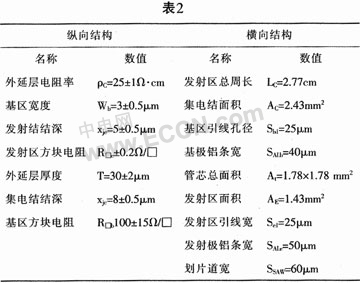

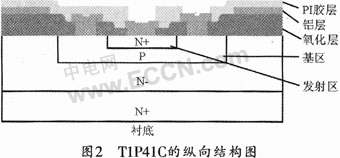

引言 TIP41C是一种中压低频大功率线性开关晶体管。该器件设计的重点是它的极限参数。设计反压较高的大功率晶体管时,首先是如何提高晶体管的反压,降低集电区杂质浓度NC。但由于电阻率ρC的增大,集电区体电阻上的电压降会增大,从而使饱和压降增大到不允许的程度。而减小NC又会使空间电荷限制效应发生,从而造成大电流β的急剧下降。为解决上述矛盾,设计时一般采用外延结构。 事实上,TIP41C低频大功率平面晶体管在设计上应采用深扩散、厚基区、大面积宽电极等结构,管芯的纵向尺寸应比较厚,横向尺寸应比较宽。控制管芯面积在2×2 mm2左右时,可采用覆盖式结构设计光刻版图,这样就能尽可能增加发射区周长,满足电流要求,也能使电流分布更均匀。为此,本文给出了一种开发T1P41/2C低频大功率平面晶体管的设计方法。 1 TIP41C芯片的参数要求 TIP41C晶体管极限参数要求如下: PC:集电极功率耗散(Tc=25℃)为65 W BVCEO:集电极-发射极电压为100 V BVEBO:发射极-基极电压为5 V IC:集电极电流为6A TlP41C的直流电参数如表1所列。 2 TIP41C的设计计算 对于以上设计要求,可通过理论计算来确定TIP41C晶体管各部分的杂质浓度及结构尺寸。 2.1 集电结的结深和外延层电阻率的确定 若选取集电结结深xjc等于8μm,那么,根据BVCEO≥100 V,且 2.2 基区宽度Wb和发射结结深xje的确定 低频大功率晶体管的Wb、xje主要根据击穿电压和安全工作的需要来选定。图1是集电结附近的杂质分布和势垒情况,其中x1和x2分别是集电结在基区部分和集电区部分的势垒宽度,它们的总势垒宽度是δ=x1+x2。这样,在NC为2×1014cm-3、NSB为1018 cm-3、V为280 V的条件下,查表可得δ=35μm,x1/δ=0.07,此时x1为2.45μm。  为了保证击穿电压的要求,应尽可能的提高二次击穿耐压量,晶体管的基区宽度应大于2.45μm,但又不能太大,否则基区输运系数η会减小。从而使电流放大系数减小,因此应选择基区宽度Wb=3μm。由于集电结结深xjc=Wb+xje=8μm,因此,一般来说,发射结xje应等于基区宽度的1.0~2.5倍。综合以上考虑,可确定基区宽度Wb为3μm,发射结结深xje为5μm。 2.3 外延层厚度T的确定 外延层厚度T至少应等于集电区厚度WC、集电结结深xje、反扩散层三部分之和。为了能达到BVCBO指标,集电区高阻层厚度WC应大于为集电结雪崩击穿时对应的空间电荷宽度XmB。 从改善雪崩注入二次击穿的角度考虑,希望集电区厚度WC≥BVCBO/EM,其中EM为最大电场强度。 南于TIP41C晶体管的BVCBO要求为280 V,因此,对于电阻率ρc为25 Ω·cm的硅晶体管,集电区厚度WC≈20μm。假设使用掺As衬底材料,反扩散层厚为2μm,则外延层厚度T应等于30μm。所以,可取材料外延层厚度为30+2μm。  2.4 基区硼扩散浓度的确定 为改善晶体管的大电流特性,基区硼扩散浓度应高一些,但基区杂质浓度太高又会降低BVEBO,所以,应在保证BYEBO≥5 V的前提下尽量提高基区浓度。基区杂质沉积可采用离子注人工艺,当基区再分布后,可认为基区受主杂质的再分布是高斯函数分布。若试用表面浓度NSB等于1018cm-3来分析,则: 式中:N(x,t)为硅片中任意一点x处的杂质浓度: 因此有: 这样,有: 查高斯函数表得: 而在发射结xje为5μm处有: 再查高斯函数表得: 即有: 由此发射结处质浓度可查表得 考虑到边缘击穿,击穿电压有一定的下降,但也能满足BVEBO≥5 V。而用NC=2×1014cm-3NSB=1018cm-3,xje=8μm便可查曲线得出基区的方块电阻R□b为100 Ω/口。 2.5 发射区磷扩散浓度的确定 为了保证有足够的放大系数,要求发射区的磷扩散表面浓度约为1021cm-3。这在xje=5μm,NSB=1018cm-3的条件下,可查曲线估算出发射区方块电阻R□e为1 Ω/口,但在实际工作中,一般R□e以满足放大系数hEE为前提。因此,为了保证TIP41C发射区扩散有足够高的杂质浓度,发射区扩散采用三氯氧磷液态源工艺。 3 TIP41C晶体管的设计参数 TIP41C的纵向和横向结构参数如表2所列。该芯片的工艺流程如下:  N型外延片→一次氧化→一次光刻→干氧氧化→B离子注入→深基区扩散→二次光刻→磷预淀积→发射区扩散→特性光刻→特性hFE测试→P吸杂(PSG)→PLTO(低温氧化)→H2处理→三次光刻→QC检测(hFE、BVCBO、BVCEO)→蒸铝→四次光刻→铝合金→QC检测VBESAT→五次光刻→PI胶钝化→中测抽检电参数→背面减薄(220μm)→蒸银→中测测试电参数→入库 图2所示是TIP41C的纵向结构图。  由于作者所在单位的生产车间设计比较简单,车间环境净化程度不高,因此,在一次氧化、基区扩散工艺中采用TCA工艺来对一次氧化、二次氧化过程中Na+的污染进行有效控制,发射区扩散采用P-吸杂工艺来控制三次氧化过程中Na+的产生,表面钝化则采用PI胶工艺来保证外界环境不影响芯片表面,同时进一步吸收、稳定氧化层正电中心的移动,从而使芯片ICEO漏电大大减少,目前,TIP41C的电参数达到国际先进水平。 4 结束语 大量生产数据表明,我司设计的TIP41C晶体管芯片生产成本低,芯片尺寸1.78×1.78 mm2(为目前市场最小),生产原材料完全采用国产材料,目前,该芯片的关键电参数(大电流特性和饱和压降)已达到国际先进水平,因而具有极强的市场竞争力。 |

网友评论