英特尔3D三栅极晶体管设计获年度科技创新奖

发布时间:2011-10-21 14:39

发布者:1046235000

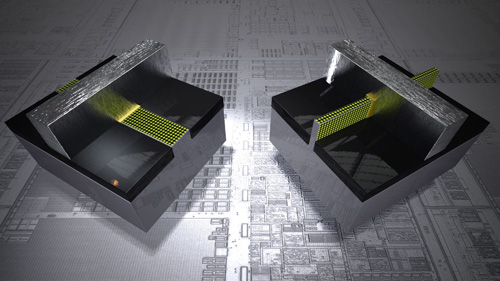

《华尔街日报》近日公布2011年“科技创新奖”,英特尔的3-D三栅极晶体管设计获得半导体类别创新大奖。英特尔的3-D三栅极晶体管结构代表着从2-D平面晶体管结构的根本性转变。这项革命性成果,其关键在于英特尔能够把全新的3-D三栅极晶体管设计投入批量生产,开启了摩尔定律的又一个新时代,并且为各种类型的设备的下一代创新打开了大门。

《华尔街日报》在2011年科技创新奖的报告中,如此评价这项技术:“英特尔凭借3-D三栅极晶体管设计在半导体类别中拔得头筹。3-D三栅极晶体管使得制造更小的半导体成为可能,在提高性能的同时降低了能耗。这家位于加州圣克拉拉的芯片巨头预期将在年末投产采用这项新技术的处理器,首次将3-D三栅极晶体管设计投入大规模制造。这项技术将用于英特尔下一代产品Ivy Bridge中,而采用这款芯片的设备预计将在明年上市。” 3-D三栅极晶体管实现了晶体管的革命性突破。传统“扁平的”2-D平面栅极被超级纤薄的、从硅基体垂直竖起的3-D硅鳍状物所代替。电流控制是通过在鳍状物三面的每一面安装一个栅极而实现的(两侧和顶部各有一个栅极),而不是像2-D平面晶体管那样,只在顶部有一个栅极。更多控制可以使晶体管在“开”的状态下让尽可能多的电流通过(高性能),而在“关”的状态下尽可能让电流接近零(低能耗),同时还能在两种状态之间迅速切换(这也是为了达到高性能)。与之前的32纳米平面晶体管相比,22纳米3-D三栅极晶体管在低电压下将性能提高了37%,而全新的晶体管只需消耗不到一半的电量,就能达到与32纳米芯片中2-D平面晶体管一样的性能。 3-D三栅极晶体管将在英特尔下一代22纳米制程技术中采用。 |

网友评论