风暴前夕:Intel/IBM 22/15nm制程关键制造技术前瞻

发布时间:2010-1-11 13:22

发布者:phoenixmy

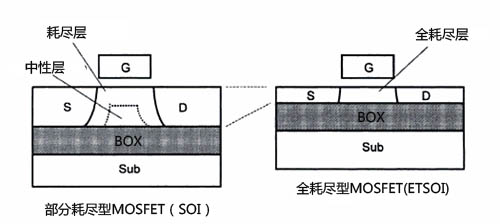

半导体特征尺寸正在向22/15nm的等级不断缩小,传统的平面型晶体管还能满足要求吗?有关这个问题,业界已经讨论了很久。现在,决定半导体制造技术发展方向的历史拐点即将到来,尽管IBM和Intel两大阵营在发展方式上会有各自不同的风格和路线,但双方均已表态称在15nm级别制程启用全耗尽型晶体管(FD:Fully Depleted)技术几乎已成定局,同时他们也都已经在认真考虑下一步要不要将垂直型晶体管制造技术如三门晶体管,finFET等投入实用。

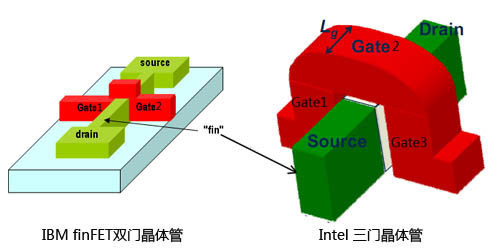

据Intel的制程技术经理Mark Bohr表示,Intel 对部分耗尽型(PD  artliy Depleted)CMOS技术能否继续沿用到15nm制程节点感到“非常悲观”。但他同时表示,虽然只有SOI技术才可以在保留传统平面晶体管结构的条件下应用FD技术;但是体硅制程也并非无可救药,采用三门或者FinFET等立体晶体管结构技术,便可以在体硅或者SOI上满足关键尺寸进一步缩小的需求,一样也可以制造出FD MOSFET。 artliy Depleted)CMOS技术能否继续沿用到15nm制程节点感到“非常悲观”。但他同时表示,虽然只有SOI技术才可以在保留传统平面晶体管结构的条件下应用FD技术;但是体硅制程也并非无可救药,采用三门或者FinFET等立体晶体管结构技术,便可以在体硅或者SOI上满足关键尺寸进一步缩小的需求,一样也可以制造出FD MOSFET。

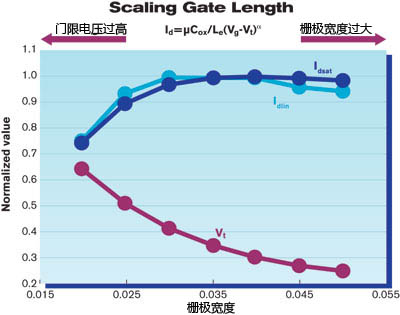

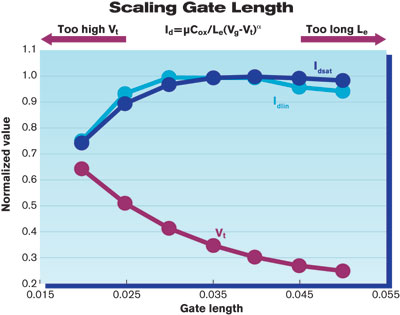

Gartner的分析师Dean Freeman则表示,目前半导体业界所面临的情况与1980年代非常类似,当时业界为了摆脱面临的发展瓶颈,开始逐步采用CMOS技术来制造内存和逻辑芯片,从而开创了半导体业界的新纪元。 栅极宽度不断减小所带来的负面效应越来越明显。首先,为了消除短通道效应,人们不得不向沟道中掺杂磷,硼等杂质元素,这便导致管子门限电压Vt的上升,同时还降低了沟道中电子流动的速度,造成管子速度的下降。而且用来向沟道中掺杂杂质的离子注入工艺也存在很难控制的问题,很容易造成管子门限电压过大等不良结果。

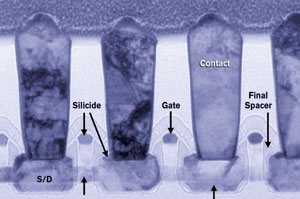

其次,传统的SiGe PMOS硅应变技术也开始面临瓶颈,在32nm制程节点中,漏源两极中掺杂的锗元素含量已经占到了40%左右,很难再为沟道原子提供更高级别的应变. 其三,栅极氧化物的厚度方面也将出现发展瓶颈问题.IBM研发中心的高管Bruce Doris表示,栅极氧化物厚度减薄的速度已经跟不上栅极宽度缩小的步伐. 其它一些平面型晶体管所面临的问题也将越来越难解决.工作电压的不断升高,使芯片的功耗控制变得越来越困难;而且关键尺寸的缩小还会导致漏/源极电阻的不断增大. 那么业界有什么策略来应对这些挑战呢? Intel的战略:22nm仍采用传统技术,15nm可能转向三门结构 据Intel表示,在下一代22nm制程产品中,他们仍将继续采用传统基于体硅的平面型晶体管结构(此前曾有传言称 Intel会在22nm制程中转向立体结构的三门晶体管技术),他们计划于2011年底正式推出22nm制程技术。而在今年的9月份,Intel已经展示过一款采用22nm制程技术制造的SRAM芯片,这种芯片的存储密度为364Mb,内含29亿个晶体管,并且采用了Intel第三代gate-last HKMG制程技术,门极绝缘层和金属栅极的主要部分在制造工序的最后几个工步制造成型,避开前面的高温退火工步(45/32nm中使用的前代技术则只有金属栅极才在最后几个工步制造成型)。 至于15nm制程节点,Bohr表示,Intel目前正在考虑在15nm制程节点上要采用哪些新的制程技术以满足要求,他认为:“全耗尽技术对降低芯片的功耗非常有效。”不过 Intel目前也在考虑除此之外的多种可行性方案,比如是转向三门晶体管技术(三门技术其实与IBM的双门finFET同属finFET型晶体管,但由于对手将其双门技术命名为finFET,因此Intel便根据自己的finFET技术特点将其命名为三门技术),或者是转向全耗尽+平面型晶体管技术等等。据Bohr表示,Intel会在六个月之内就15nm制程节点将采用哪一种新技术做出决定。 此前据Intel前技术经理Scott Thompson预计,Intel最终会选择采用三门结构晶体管制程,而其它的厂商则会因为FinFET结构的制程工艺复杂性而对FinFET望而却步。Scott Thompson现在的职位是在佛罗里达大学任教。 按Intel的脾气,他们一向对SOI工艺保持抗拒的态度。不过Bohr表示:“我们要找的是一种性价比最高的方案,不管是SOI或者其它的什么技术,只要某种技术能够带来额外的性能提升或较低的功耗,那么我们就会采用这些技术。” IBM阵营的战略:22nm有可能转向FD-ETSOI,15nm可能启用finFET结构 IBM阵营方面,与Intel不同,尽管有可能后延到15nm制程节点时间段,但IBM公司已经开始考虑要在22nm制程节点便开始使用FD-SOI技术。IBM公司12月份曾经展示了一种基于ETSOI(extremely thin SOI:超薄SOI)的FD-ETSOI工艺。这种工艺仍然基于传统的平面型晶体管结构,不过这种工艺的SOI层厚度则非常薄,这样便可以采用全耗尽工艺,能够显著减小短通道效应(SCE)的影响。

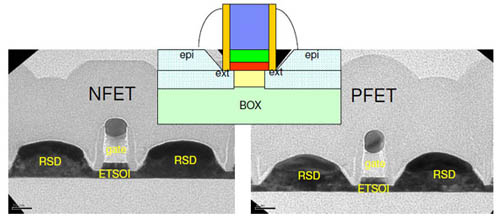

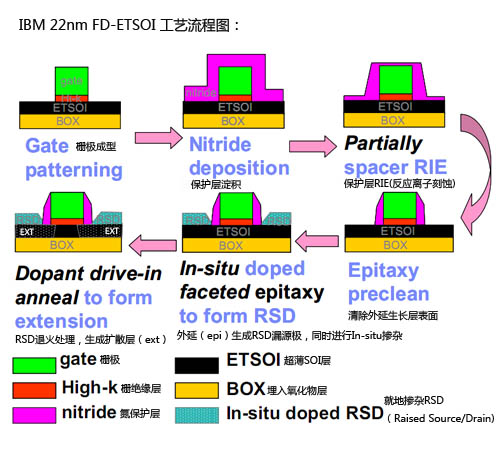

ETSOI技术能将SOI层的厚度缩小到极低的水平,使用这种技术之后,22nm制程中的SOI层的厚度仅有6.3nm,而传统的SOI层厚度通常在 20nm以上,发展到15nm制程,SOI层的厚度还可以进一步被缩小到5nm左右。据IBM表示,尽管由Soitec公司提供,能用于制造ETSOI产品的SOI晶圆数量仍十分有限,但他们已经可以把这种SOI层的厚度误差控制在±5 ?左右. 不过ETSOI技术也有其难点,由于SOI层的厚度极薄,因此很容易受到损坏。而且为了避免对SOI层造成损坏,在制造漏/源极时不能采用传统破坏性较强的离子注入技术,必须采用就地掺杂技术(in-situ doping)。“我们采用的是不会损害ETSOI层的就地掺杂技术。我们首先生成栅极隔离层,然后在漏源区用外延技术沉积生长出漏/源极,形成外延层(图中的epi)并在漏/源极的生长过程中同时就地掺杂所需的杂质元素,然后我们会对晶体管进行加热处理,令漏源极中的掺杂原子向沟道方向扩散,形成扩散层(图中的ext)。而加热处理过程中我们使用的尖峰退火技术(spike anneal )则不会对ETSOI层的结构造成不必要的损害。” 隶属IBM技术同盟的GobalFoundries的技术开发经理John Pellerin也表示这种FD-ETSOI技术很快便会付诸实用,不过他表示:“但是我们现在很难说具体什么时候会转向这种技术。”Pellerin表示,FD-SOI技术从应用结构上看与现有的PD-SOI技术非常相近,“我们只需要把SOI层的厚度变薄,并想办法解决ETSOI带来的一些问题即可,其它的部分则和传统的制造工艺基本相同。”当然ETSOI技术仍有许多其他的问题需要解决,比如如何减小器件的寄生电阻等等。 IBM的下一步:finFET 另据Pellerin表示,在ETSOI技术发展的下一步很可能会开始启用finFET立体型晶体管结构,两者的关系就像过去我们从部分掺杂型SOI(PD-SOI)技术过渡到FD-SOI那样。“我看不出来ETSOI和finFET两种技术之间存在什么矛盾之处,而且采用平面型结构ETSOI技术所能达到的晶体管密度总会出现发展瓶颈,而finFET则可以解决这种问题。” 2009年,IBM公司增加了用于实验finFET效能的晶圆样片数量,据他们表示,finFET技术所带来的性能提升“令人非常满意。”不过 finFET与平面型晶体管之间各有优劣。“平面型晶体管结构并不需要对传统的工艺进行太多改进,过去30年来人们所使用的很多技术都可以应用在平面型结构的ETSOI里,而要进一步升级为finFET结构,所需要的制造工艺则复杂得多,这种技术对光刻和蚀刻技术提出了很高的要求。” ETSOI辅助技术:SiC硅应变技术 在22nm节点,看起来至少1家以上的大型厂商会采用向NMOS管的漏源区掺杂碳原子的方法来为沟道施加拉伸应力,以形成应变硅。IBM在描述自己的 FD-ETSOI工艺时曾经提到,他们会在沉积NMOS管的漏源极时向极内掺杂碳杂质。而且另外一家IBM工艺技术联盟的成员Applied Materials公司也分别在去年的IEDM和今年的Semicon会展上两次强调了这种SiC硅应变技术的可行性。 那么外界对SiC 技术的评价如何呢?据GlobalFoundries公司的Pellerin表示:“我们正在关注SiC硅应变技术,并且正在考虑在我们的22nm及更高级别制程中使用这项技术。”在目前的工艺尺寸条件情况下,要想很好地控制漏源区的离子注入过程将是一项非常复杂的任务,而在IBM的FD-ETSOI工艺中,NMOS中使用的SiC硅应变技术则与PMOS中的SiGe硅应变技术一样是采用外延沉积实现的,不必再为如何控制离子注入而担忧。他并表示:“如何在NMOS管中应用硅应变技术将是另外一个改善晶体管性能的关键技术。” 相比之下,Intel的Bohr则完全改变了他对SiC硅应变技术的态度,他过去曾经表示 Intel更倾向于使用SiC硅应变技术,不过最近他在IEDM2009会议中接受采访时则表示他不愿意就Intel在SiC硅应变技术方面取得的进展发表任何评论。而会上代表Intel做有关Intel 32nm制程技术演讲的Paul Packan则在演讲后回答记者提问的环节没有理会一位记者提出的有关SiC硅应变技术在32nm制程NMOS结构中应用状况的问题。 小结:Intel与IBM:你走你的阳光道,我过我的独木桥 Gartner 的分析师Freeman表示,他认为Intel和AMD会继续走自己的老路,Intel不太可能会使用SOI技术,而IBM则会继续将SOI发扬光大。他认为Intel如果采用三门晶体管技术,“便可以绕开SOI,因此Intel未必会转向SOI。”他并表示:“Intel会尽可能地延长体硅制程的寿命,而IBM则会尽快转向全耗尽型SOI技术。”他还认为将来Soitec和信越化学公司(SEH, Tokyo)将具备向IBM提供符合对方需要的ETSOI晶圆的能力(目前IBM需要在厂内对ETSOI硅层进行处理)。 其它关键技术:

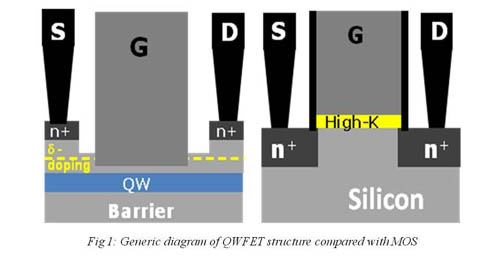

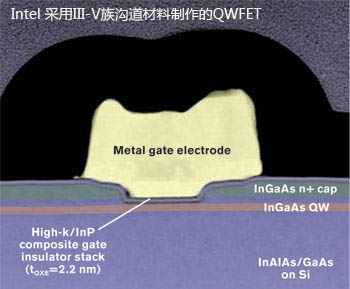

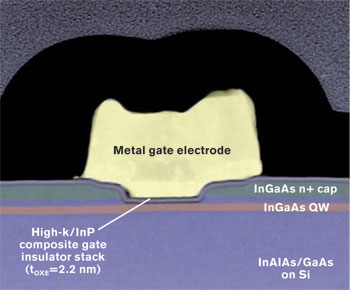

除了以上所述的即将投入使用的技术之外,用于制造场效应管沟道的半导体材料下一步也有可能会发生变化。在去年的IEDM会议上,斯坦福大学的教授 Krishna Saraswat曾表示,当沟道宽度降至10nm左右时,必须采用新材料来制造沟道。据他估计,业界将首先开发出NMOS管使用III-V族元素构建沟道,PMOS管使用锗元素构建沟道的技术,然后再向PMOS/NMOS统一采用III- V族元素制造沟道的方向发展。转向使用III-V族元素将大大减小器件的工作电压和管子的能耗,可将工作电压减小至0.5V。不久之前,Intel便介绍了他们在使用这种技术制造的QWFET场效应管方面取得的新进展,当时他们向这种晶体管结构中引入了High-K栅极氧化物层。 除此之外,IBM则在TSV硅通孔互连技术和3D堆叠封装技术方面取得了较大的进展。 CNBeta编译 原文:semiconductor |

网友评论