在PLD开发中提高VHDL的综合质量

发布时间:2010-9-18 20:13

发布者:conniede

|

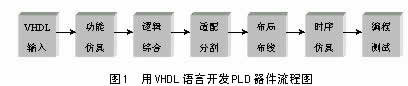

引 言 随着计算机与微电子技术的发展,电子设计自动化EDA(Electronic Design Automation)和可编程逻辑器件PLD(Programmable Logic Device)的发展都非常迅速,熟练地利用EDA软件进行PLD器件开发已成为电子工程师必须掌握的基本技能。先进的EDA工具已经从传统的自下而上的设计方法改变为自顶向下的设计方法,以硬件描述语言HDL(Hardware Description Language)来描述系统级设计,并支持系统仿真和高层综合。ASIC(Application Specific Integrated Circuit)的设计与制造,电子工程师在实验室就可以完成,这都得益于PLD器件的出现及功能强大的EDA软件的支持。现在应用最广泛的高密度PLD器件主要是现场可编程门阵列FPGA(Field Programmable Gate Array)和复杂可编程逻辑器件CPLD(Complex Programmable Logic Device)。 EDA软件方面,大体可以分为两类: ① PLD器件厂商提供的EDA工具。较著名的如:Altera公司的 Max+plus II和Quartus II、Xilinx公司的Foundation Series、Latice-Vantis公司的ispEXERT System。 ② 第三方专业软件公司提供的EDA工具。常用的综合工具软件有:Synopsys公司的FPGA Compiler II、Exemplar Logic公司的LeonardoSpectrum、Synplicity公司的Synplify。第三方工具软件是对CPLD/FPGA生产厂家开发软件的补充和优化,如通常认为Max+plus II和Quartus II对VHDL/Verilog HDL逻辑综合能力不强,如果采用专用的HDL工具进行逻辑综合,会有效地提高综合质量。 1 PLD器件的开发 CPLD/FPGA设计越来越复杂,使用硬件描述语言设计可编程逻辑电路已经成为大势所趋,目前最主要的硬件描述语言是:VHDL(Very High Speed Integrated Circuit HDL)和Verilog HDL。两种语言都已被确定为IEEE标准。 用VHDL/Verilog HDL语言开发可编程逻辑电路的完整流程为: ① 文本编辑。用任何文本编辑器都可以,但通常在专用的HDL编辑环境中进行。因为专业的集成开发环境通常提供各种结构模板,并且可以自定义各种要素(例如关键字、字符串、注释等)的色彩显示,提高可读性,提高输入效率。 ② 功能仿真。将文件调入HDL仿真软件进行功能仿真,检查逻辑功能是否正确。 ③ 逻辑优化与综合。将源文件调入逻辑综合软件进行逻辑分析处理,即将高层次描述(行为或数据流级描述)转化为低层次的网表输出(寄存器与门级描述),逻辑综合软件会生成EDIF(Electronic Design Interchange Format)格式的EDA工业标准文件。这步在PLD开发过程中最为关键,影响综合质量的因素有两个,即代码质量和综合软件性能。 ④ 适配与分割。如果整个设计超出器件的宏单元或I/O单元资源,可以将设计划分到多片同系列的器件中。 ⑤ 装配或布局布线。将EDIF文件调入PLD厂家提供的软件中进行装配(对于CPLD)或布局布线(对于FPGA),即将设计好的逻辑写入CPLD/FPGA器件中。 ⑥ 时序仿真。即延时仿真,由于不同器件、不同布局布线,给延时造成的影响不同,因此对系统进行时序仿真,检验设计性能,消除竞争冒险是必不可少的步骤。 利用VHDL语言进行PLD设计开发的基本流程如图1所示。如果选用Altera公司CPLD器件作为目标器件,上述过程可以在Altera公司提供的 Max+plus II或Quartus II集成开发环境中完成,但如果选用专用的EDA综合工具作为补充,完成逻辑优化与综合,设计质量会更好。第三方综合软件的主要功能就是对HDL语言的源文件进行逻辑综合,生成.edf的EDA工业标准文件,然后在PLD厂家提供的开发软件中调入.edf文件,进行编译、仿真、器件编程等过程,最终完成整个设计。针对Altera公司CPLD器件,我们选用Quartus II + LeonardoSpectrum的EDA组合开发方式,更重要的是,广大学习爱好者可以在www.altera.com网站免费获得。下面对两款软件作简要介绍。  2 Quartus II软件的应用 Quartus II是Altera公司的第四代可编程逻辑器件集成开发环境,提供从设计输入到器件编程的全部功能。 Quartus II可以产生并识别EDIF网表文件、VHDL网表文件和Verilog HDL网表文件,为其它EDA工具提供了方便的接口;可以在Quartus II集成环境中自动运行其它EDA工具。 利用Quartus II软件的开发流程可概括为以下几步:设计输入、设计编译、设计定时分析、设计仿真和器件编程。 (1)设计输入 Quartus II软件在File菜单中提供“New Project Wizard…”向导,引导设计者完成项目的创建。当设计者需要向项目中添加新的VHDL文件时,可以通过“New”选项选择添加。 (2)设计编译 Quartus II编译器完成的功能有:检查设计错误、对逻辑进行综合、提取定时信息、在指定的Altera系列器件中进行适配分割,产生的输出文件将用于设计仿真、定时分析及器件编程。 ① 首先确定软件处于Compile Mode,可以通过Processing菜单进行选择。 ② 在Processing菜单中选择Compiler Settings项,如图2所示。可以进行器件选择、模式设定、综合和适配选项设定及设计验证等。 ③ 单击Processing菜单下的“Start Compilation” 项,开始编译过程。 ④ 查看编译结果。如图3所示,我们可以得到详细的编译报告。 (3)设计定时分析 单击Project菜单下的“Timing Settings…”选项,可以方便地完成时间参数的设定。Quartus II软件的定时分析功能在编译过程结束之后自动运行,并在编译报告的Timing Analyses文件夹中显示,如图3所示。其中我们可以得到最高频率fmax、输入寄存器的建立时间tSU、引脚到引脚延迟tPD、输出寄存器时钟到输出的延迟tCO和输入保持时间tH等时间参数的详细报告,从中可以清楚地判定是否达到系统的定时要求。 (4)设计仿真 Quartus II软件允许设计者使用基于文本的向量文件(.vec)作为仿真器的激励,也可以在Quartus II软件的波形编辑器中产生向量波形文件(.vwf)作为仿真器的激励。波形编辑方式与MAX+PLUS II软件的操作相似。在Processing菜单下选择“Simulate Mode”选项进入仿真模式,选择“Simulator Settings…”对话框进行仿真设置。在这里可以选择激励文件、仿真模式(功能仿真或时序仿真)等,单击“Run Simulator ”即开始仿真过程。 (5)器件编程 设计者可以将配置数据通过MasterBlaster或ByteBlasterMV通信电缆下载到器件当中,通过被动串行配置模式或JTAG模式对器件进行配置编程,还可以在JTAG模式下给多个器件进行编程。利用Quartus II软件给器件编程或配置时,首先需要打开编程器(在New菜单选项中选择打开Chain Description File),在编程器中可以进行编程模式设置(Mode下拉框)、硬件配置(Programming Hardware对话框)及编程文件选择(Add File…按钮),将以上配置存盘产生.cdf文件,其中存储了器件的名称、器件的设计及硬件设置等编程信息。当以上过程正确无误后,单击Start按钮即可开始对器件进行编程配置。 3 LeonardoSpectrum软件的应用 LeonardoSpectrum是Mentor Graphics的子公司Exemplar Logic的专业VHDL/Verilog HDL综合软件,简单易用,可控性较强,可以在LeonardoSpectrum中综合优化并产生EDIF文件,作为QuartusII的编译输入。该软件有三种逻辑综合方式:Synthesis Wizard(综合向导)、Quick Setup(快速完成)、Advanced FlowTabs(详细流程)方式。三种方式完成的功能基本相同。Synthesis Wizard方式最简单,Advanced FlowTabs方式则最全面,该方式有六个选项单,如图4所示,分别完成以下功能:器件选择、设计文件输入、约束条件指定、优化选择、输出网表文件设置及选择调用布局布线工具。以上每步操作都提供相应的帮助,简单明了。需要注意的是,在输入设计文件时要正确排列文件的次序,将底层文件放在前面,顶层文件放到后面,这样LeonardoSpectrum软件才能正确地建立数据信息库。综合完成后,可以将输出网表文件 (.EDF)作为 MAX+PLUS II或Quartus II的设计输入文件,再完成编译、仿真、定时分析和器件编程等步骤,完成整个系统的设计过程。 4 VHDL编码方式对综合质量的影响 VHDL语言支持全部的仿真功能,但并不是全部可综合的。VHDL程序的许多硬件描述和仿真结构没有对应的数字电路来实现,还有些描述在理论上可以映射为对应的数字电路,但是却不能保证其精确性,比如延时模型。随着综合算法技术水平的提高,针对某些寄存器传输级RTL(Register Transfer Level)电路描述可以进行有效的优化,但是对于更普遍的电路描述这还不够,因此综合结果是否满足给定的时间约束条件和面积约束条件,还取决于VHDL编码方式。下面给出几点经验,相信对提高综合质量有所帮助与启发。 (1)资源共享 例如下面的两段代码中,(A)需要2个加法器,而完成同样的功能,略做修改;(B)只需要1个加法器,有效地减少了使用面积。适当地利用圆括号进行重新组合,有时也可以实现资源的共享。如下面两段代码(C)和(D),(D)中输入信号b和c即可实现加法器的共享。  (2)使用带范围限制的整数 在VHDL中无约束整数的范围是-2147483647~+2147483647。这意味着至少需要32位来表示,但通常这会造成资源的浪费,有些综合软件会自动优化,但所消耗的时间是相当可观的。因此,如果不需要全范围的整型数据,最好指定范围,例如:signal small_int : integer range 255 downto 0 ;small_int在本例中只需要8位,而不是32位,有效地节约了器件面积。 (3)使用宏模块 当在VHDL中使用算术逻辑、关系逻辑等通用逻辑结构时,多数EDA开发软件及专用综合工具通常包含针对特定工艺的优化宏模块供我们选择,从功能上可分为时序电路宏模块、运算电路宏模块和存储器宏模块,具有很高的执行效率,使得综合结果面积更小、频率更高、所需编译时间更短。当然,它们是针对特定工艺的,这将使VHDL程序依赖于具体的器件系列,影响移植性。 (4)高级设计优化 上述几种方法是在没有改变其功能性的情况下进行综合优化的,有时候我们可以在不妨碍设计规格约束的前提下,稍微改变其功能,来提高综合效率,参考下面两个例子(E)和(F)。 在(E)中,综合工具建立递增计数器和完整的比较器; 在(F)中,综合工具建立递减计数器和对于常数零的比较器。由于和常数作比较更易于实现,且占用逻辑单元更少,因此(F)程序更高效。  另外,由于综合工具只能支持VHDL的子集,为保证在综合前后的仿真保持相同,以下语句在综合中应该避免使用: ◇ 避免使用 wait for xx ns,这种语句不会被综合为实际的电路元件; ◇ 避免使用after xx ns,在综合工具进行综合时,会忽略after语句; ◇ 避免在信号和变量声明时赋初值,因为大部分综合工具会忽略初始化语句,如果使用初始化语句,那么综合的结果和仿真的结果将会产生差异。 5 结 语 功能强大的EDA开发软件和专业的综合工具的不断发展,使PLD设计或ASIC 设计过程更简单、更快捷;但是,要提高设计质量,编程方式仍然起着至关重要的作用,需要我们在实践中不断摸索,积累经验,提高设计水平。 |

网友评论