详解Gate- first与Gate-last工艺之争

发布时间:2010-3-20 08:45

发布者:老郭

|

前些天,经常看到到某公司采用Gate-first工艺、某公司采用Gate-last工艺的新闻。究竟这两种工艺是怎么回事,本人确实不清楚,新闻里也没有给个交代。今天终于看到这篇文章。先转过来慢慢看。 --------------------------- 随着晶体管尺寸的不断缩小,HKMG(high-k绝缘层+金属栅极)技术几乎已经成为45nm以下级别制程的必备技术。不过在制作HKMG结构晶体管的 工艺方面,业内却存在两大各自固执己见的不同阵营,分别是以IBM为代表的Gate-first工艺流派和以Intel为代表的 Gate-last工艺流派,尽管两大阵营均自称只有自己的工艺才是最适合制作HKMG晶体管的技术,但一般来说使用Gate- first工艺实现HKMG结构的难点在于如何控制 PMOS管的Vt电压(门限电压);而Gate-last工艺的难点则在于工艺较复杂,芯片的管芯密度同等条件下要比Gate-first工艺低,需要设 计方积极配合修改电路设计才可以达到与Gate-first工艺相同的管芯密度级别。

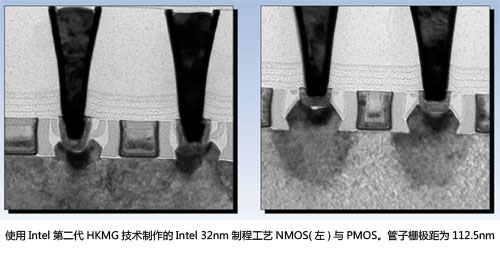

HKMG实现工艺的两大流派: Gate-last阵营:目前已经表态支持Gate-last工艺的除了Intel公司之外(从45nm制程开始,Intel便一直在制作HKMG晶体管时使用Gate-last工艺),主要还有芯片代工业的最大巨头台积电,后者是最近才决定在今年推出的28nm HKMG制程产品中启用Gate-last工艺。 Gate-first阵营:Gate-first工艺方面,支持者主要是以IBM为首的芯片制造技术联盟 Fishkill Alliance的所属成员,包括IBM、英飞凌、NEC、GlobalFoundries、三星、意法半导体以及东芝等公司。尽管该联盟目前还没有正式推出基于HKMG技术的芯片产品,但这些公司计划至少在32/28nm HKMG级别制程中会继续使用Gate-first工艺。不过最近有消息传来称联盟中的成员三星则已经在秘密研制Gate-last工艺。另外,台湾联电公司的HKMG工艺方案则较为特殊,在制作NMOS管的HKMG结构时,他们使用Gate-first工艺,而制作PMOS管时,他们则会使用Gate-last工艺。 HKMG的优势和缺点: 优势:不管使用Gate-first和Gate-last哪一种工艺,制造出的high-k绝缘层对提升晶体管的性能均有重大的意义。high-k技术不仅能够大幅减小栅极的漏电量,而且由于high-k绝缘层的等效氧化物厚度(EOT:equivalent oxide thickness)较薄,因此还能有效降低栅极电容。这样晶体管的关键尺寸便能得到进一步的缩小,而管子的驱动能力也能得到有效的改善。 缺点:不过采用high-k绝缘层的晶体管与采用硅氧化物绝缘层的晶体管相比,在改善沟道载流子迁移率方面稍有不利。 Gatefirst/Gatelast的优缺点差别分析与未来应用状况: 不过,采用Gate-first工艺制作HKMG结构时却有一些难题需要解决。一些专家认为,如果采用Gate-first工艺制作HKMG,那么由于用来制作high-k绝缘层和制作金属栅极的材料必须经受漏源极退火工步的高温,因此会导致PMOS管Vt门限电压的上升,这样便影响了管子的性能。而持不同观点的专家,包括GlobalFoundries公司的技术总监John Pellerin等人则强调,Gate-first工艺不需要电路设计方在电路设计上做太多更改,而且性能上也完全能够满足32/28nm节点制程的要求。 Pellerin 强调:“我们肯定会在28nm节点制程上使用Gate-first工艺。其原因是我们的客户希望在转换到HKMG结构时能够尽量避免过多的设计变更。” 而台积电的技术高管蒋尚义则表示,类似的难题业界在20年前便曾经经历过:“当时业界同样曾经发现N+掺杂的PMOS栅极材料会造成Vt电压较高,这样业内一些公司便开始向沟道中掺杂杂质以压低Vt,结果却带来了很多副作用,比如造成短通道效应更为明显等等。”而目前使用Gate-first工艺制作 HKMG晶体管的方案的情况则与此非常类似,尽管人们可以采用加入上覆层等方式来改善Gate-first工艺容易造成Vt过高的问题,但是加入上覆层的工艺却非常复杂和难于掌握。因此台积电干脆选择转向Gate-last工艺,不过Gate-last工艺实施时如果想保持与Gate-first工艺产品的管芯密度近似,需要设计方对电路Layout进行重新设计。 专家意见: Gartner公司的半导体产业分析师Dean Freeman表示:“台积电转向Gate-last,说明这种工艺在性能方面还是存在一定的优越性的。虽然Gate-first工艺制成的产品在管芯密度方面较有优势,但继续应用这种工艺一定存在一些台积电无法克服的难题。” 欧洲校际微电子中心组织IMEC负责high-k技术研发的主管Thomas Hoffmann曾经在IEDM2009大会上指出了Gate-first工艺在性能方面存在的不足,不过在会后的一次访谈中,他表示尽管Gate-first存在一些性能方面的缺点,但是对一部分对性能并不十分敏感的第功耗器件还是能够满足要求的。 他表示:“对瑞萨等开发低功耗器件的公司而言,也许Gate-first工艺是目前较好的选择。这类器件一般对Vt值和管子的性能并没有太高的要求。不过当产品的制程节点发展到28nm以上级别时,这些公司便需要转向Gate-last。”不过”对以追求性能为主的厂商而言,Gate-last则是必然之选。IBM的产品显然属于这种类型,所以我认为如果他们不使用Gate-last的话,就必须在如何降低Vt的问题上想出好办法。当然这种方案的复杂性会更大,而且还有可能会影响到产品的良率。而最终他们也有可能会倒向Gate-last工艺,这就是IBM Fishkill生产技术联盟中的伙伴感到担心的地方。“ Gate-first工艺控制管子门限电压的方案和难点所在:上覆层(Cap layer): 据Hoffmann介绍,尽管在Gate-last工艺中,制造商在蚀刻和化学抛光(CMP)工步会遇到一些难题,但是Gate-first工艺也并非省油的灯。如前所述,目前Gate-first工艺虽然不好控制Vt,但也不是完全没有办法,其主要的手段是通过设置 一定厚度的high-k绝缘体上覆层(cap layer)来实现,这种方案需要在high-k层的上下位置沉积氧化物薄层。比如在NMOS管中,便需要在high-k层的上部沉积一层厚度小于1nm 的 La2O3薄层,以达到调整Vt电压的目的;而在PMOS管中,则需要通过蚀刻工步将这一层薄层去掉,换成 Al2O3材质的薄层,这样便需要复杂的工艺来控制如何在PMOS管中将这一薄层去掉而不影响到NMOS的上覆层。

他表示:“NMOS管的上覆层需要采用La2O3材料制作,而PMOS管则需要用Al2O3来制作上覆层,这样就需要在NMOS管的上覆层上覆盖一层光阻胶,然后再用显影+蚀刻方式去掉沉积在PMOS管中的La2O3,不过处理完成之后要除去覆盖在厚度小于1nm的La2O3 上覆层上的光阻胶时,由于上覆层的厚度极薄,因此如果不能小心控制就会对上覆层造成一定的损坏,这就要求厂商具备非常高超精密的去胶工艺。” Gate-last的优势:可自由设置和调配栅电极材料的功函数值,充分控制Vt电压 ASM公司的外延产品和ALD(原子层淀积)业务部经理Glen Wilk则表示,业内已经就gate-first与gate-last之间在性能、复杂程度和成本方面的优劣对比争执了许久,“不过我认为随着产品制程尺寸的进一步缩小,gate-last工艺的优越性开始逐步体现,由于这种工艺的栅极不必经受高温工步,因此厂商可以更加自由地设置和调配栅电极材料的功函数值,并很好地控制住管子的Vt电压。” Wilk表示,随着制程尺寸的进一步缩小,采用 gate-first工艺的厂商会发现“PMOS管的特性越来越难控制,实施Gate-first工艺的难度也悦来越大,因此我认为未来业界对gate- last工艺的关注程度会越来越广泛。”Wilk认为,由于gate-last工艺可以很好地控制栅极材料的功函数,而且还能为PMOS管的沟道提供有利改善沟道载流子流动性的硅应变力,因此gate-last工艺将非常适合低功耗、高性能产品使用。他表示:“不过我认为内存芯片厂商可能在转向gate-last工艺时的步伐可能会稍慢一些。他们可能会在未来一段时间内继续使用gate- first工艺,不过gate-last工艺显然有助于提升产品的性能和降低产品的待机功耗。” 而 Applied Materials公司的CTO Hans Stork则表示,gate-first工艺需要小心对待用来控制Vt电压的上覆层的蚀刻工步,而gate-last工艺则需要在金属淀积和化学抛光工步加以注意。“长远地看,我认为Gate-last工艺的前景更好一些。”他表示,芯片厂商目前都非常关注Intel 公司的32nm制程SOC芯片工艺,在这种工艺中,high-k绝缘层的等效氧化物厚度(EOT)为0.95nm。他说:“Intel将其32nm gate-last制程SOC芯片产品的应用范围从高性能应用市场进一步拓展到了低漏电/低电压应用领域,而手机芯片则正好需要具备这些特性。”客户们对 gate-last和gate-first工艺在工函数控制,成本,产能,良品率等方面的实际对比数据非常关注。以至于已经有部分手机芯片厂商如高通等已经开始要求代工商能为他们提供“能与Intel的产品性能相近”的产品。

在IEDM2009 会议上,高通公司的高管曾表示他们很支持台积电去年七月份宣布将启用Gate-last工艺的决定。而今年1月份,高通则宣布已经与 GlobalFoundries公司签订了28nm制程产品的代工协议。这样,届时人们便有机会可以实际对比一下分别来自台积电和 GlobalFoundries两家公司,分别使用gate-last与gate-first两种工艺制作出的手机芯片产品在性能方面究竟有多大的区别。目前,高通公司的40nm制程手机用处理器类属与高性能芯片,其运行频率达到了1GHz,不过其功耗也控制得相当好,在谷歌Android智能手机中有使用这种处理器产品。 Intel公司的制程技术高管Mark Bohr则表示Intel公司的Atom SOC芯片还需要一年左右的时间才会启用32nm制程工艺。当被问及应用gate-last工艺以后为什么芯片的核心尺寸会有所增大,是不是由于 gate-last本身的限制,导致更改后的电路设计方案管芯密度有所下降的问题时,Bohr表示Intel公司45nm gate-last HKMG制程产品上电路设计方案的变动并不是由于应用了gate-last所导致,而是与当时Intel在45nm制程产品上还在继续使用干式光刻技术有关。他表示“当时之所以会采用那种核心面积较大的设计规则,其目的并不是为了满足Gate-last HKMG工艺的要求,而是要满足使用干式光刻技术的要求。”(Intel在45nm制程节点仍然在使用干式光刻技术,直到32nm才开始使用沉浸式光刻技术。) HKMG技术未来一段时间内的发展趋势: High-k绝缘层的材料选择方面,包括Intel公司的Bohr在内,大家似乎都同意HfO2将在未来一段时间内继续被用作High-K层的材料,业界近期将继续在改良HfO2材料上做文章,部分厂商可能还会考虑往HfO2层中添加一些特殊的材料,但他们近期不会把主要的精力放在开发介电常数更高的材料方面。

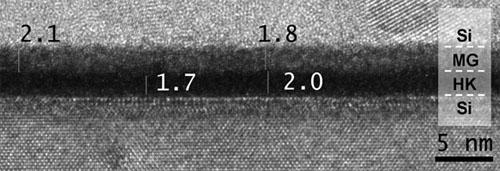

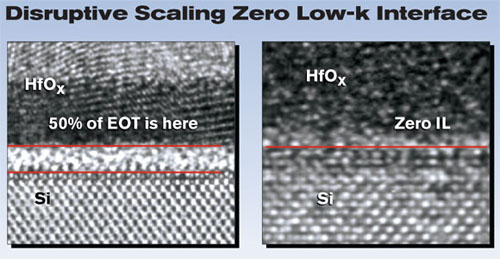

另外,有部分厂商的主要精力则会放在如何减小High-k层下面的SiO2界面层(IL)的厚度方面,其目标是在 High-k绝缘层的等效氧化物厚度为10埃时能把这种界面层的厚度降低到5埃左右。Sematech公司负责High-k项目研究的高管Paul Kirsch表示:“业内现在考虑较多的主要是如何进一步优化HfO2材料,而不是再花上五年去开发一种新的High-k材料。从开发时间要求和有效性要求方面考虑,目前最有意义的思路是考虑如何消除SiO2界面层和改善High-K绝缘层的介电常数值。” Gatefirst在如何有效消除SiO2界面层(ZIL)方面的优势及各方评述: 消除SiO2界面层方面,在去年12月份举办的IEDM会议上,科学家们发布了多篇有关如何消除SiO2界面层的文章(ZIL:zero interface layer),其中IBM的Fishkill技术联盟也公布了自己的方案,并宣称这种方案将在自己的gate-first 32/28nm制程中使用。 耶鲁大学的T.P. Ma教授表示,ZIL技术虽然非常吸引人,但通常需要使用高温工步来消除SiO2界面层,而gate-first工艺制作的栅极则正好能够承受这种高温,所以这项技术对采用gate-first工艺的厂商比较有利。他认为,按照他的理解,ZIL技术的实现需要使用“高温化学反应”来有效地去除栅极结构中残留的SiO2界面层,这样这项工艺对使用gate-first工艺的厂家而言实现起来难度更小一些,而使用gate-last工艺的厂商则会尽量避免使用高温工步。他还表示,IBM和Sematech公司所制出的ZIL结构已经能够在5埃的等效氧化层厚度条件下达到较好的防漏电性能。

不过据Sematech公司的材料与新兴科技研发副总裁Raj Jammy表示,尽管Sematech公司早期的ZIL结构确实是在gatefirst工艺的基础上制造出来的,但是“要制出ZIL未必需要依靠高温处理工步,而主要是要去掉界面层中的氧离子。”他还强调不同的情况需要采用不同的热处理方式来进行处理,才能得到较好的管子参数。 而另外一篇IMEC的研究报告则指出,“我们制作ZIF的方法是需要进行高温热处理的,不过要生成理想的无界面层栅极结构的方法有很多种,因此未必说 gatelast工艺就不利于ZIL的制作。”他还表示应该可以找到一种方案来兼顾ZIL与gatelast工艺的优点。 另外,在被问及对ZIL技术的看法时,Intel高管Bohr回答称:“在我的印象中这种技术并不是很有效,这主要是由于ZIL结构对沟道的载流子迁移率有一定的不良影响,而如果我们能够很好地控制界面层的材料和厚度,管子的性能一样也可以达到要求”,他还表示“相比之下,我认为我们应该努力去改善 High-K绝缘层的材料,并想办法减小金属电极的电容。” Gartner 市调公司的Freeman则表示,从28nm制程节点开始,台积电公司与GlobalFoundries之间的HKMG产品由于所用的工艺不同,因此将存在比较明显的区别。按照这样的差别趋势发展下去,一种最终的可能就是IBM和GlobalFoundries会在22nm制程节点马上转向gate- last工艺,而另外一种可能就是由于gatefirst在ZIL方面的优势被实际的应用证明,而将慢慢处于领先的位置。Freeman还表示:“在 16nm制程节点,如何控制好管子的界面层,将是至关重要的。” CNBeta编译 |

网友评论