造就每秒20亿次访问速度的串行存储器:设计、工艺和测试技术

发布时间:2012-7-10 11:16

发布者:李宽

关键词:

存储器

|

MoSys公司最新推出的串行存储器Bandwidth Engine IC,利用高效的10G串行接口和创新架构达到了每秒20亿次以上的存储器访问速度。这种访问速度是支持100GE(千兆位以太网)和100Gbps汇聚线卡要求的数据速度所必需的。Bandwidth Engine IC的ALU和存储器架构具有一定的智能,能够加速诸如统计等网络操作,设计用于高数据速度、10年期望寿命、政府强制要求降低功耗等具有严格限制规范的应用。 Bandwidth Engine有别于传统网络器件的关键在于快速、智能访问方面,因此能够在数据包分级应用中发挥很好的作用。这要求MoSys采用高度合作的设计方法。为了达到这个访问速率,Bandwidth Engine IC运用了严格的产品定义、设计严谨的RTL代码、高速和低延时的串化解串器(SerDes)、MoSys开发的1T-SRAM核心技术以及创新的版图与封装设计,最终形成了一款利用高速串行接口减轻SoC封装和系统设计挑战的器件。通过将传统存储器件的块(bank)合并到一个Bandwidth Engine,不仅提高了总体系统性能,而且降低了功耗和成本。 Bandwidth Engine使用了MoSys公司最初的技术创新成果--1T-SRAM。这是一种接近SRAM速度的嵌入式DRAM存储器,其关键技术是采用了带小容量内存块的eDRAM阵列架构,因而减少了位线上的电容和电阻负载,具有更低的延时。 另外,1T-SRAM接口隐藏了DRAM刷新和预充周期,内存块能以3.9ns的周期实现“像SRAM一样快的”读写速度。嵌入式存储器被组织成4个独立的分区,每个分区又被分成64(32Kb×72)个内存块,因此总存储容量为576Mb。每个分区有一个写端口和两个读端口,并以循环TDM方式提供访问。这种阵列架构单元的组合允许在每个3.9ns周期内实现高达12次的在线操作。因此在10G工作模式下,每1ns就能发出三条指令。 Bandwidth Engine的核心存储器阵列架构增加了效率高达90%的创新型低延时接口,而该接口又是运行在1到16条与CEI-11或XFI兼容的差分串行链路之上。另外还针对高访问速率器件优化了Gigachip接口(GCI),数据包长为80位,其中72位是净负荷,8位用于CRC校验。GCI串行接口是专为芯片到芯片通信设计的,而不是为普通的网络串化解串器应用所设计,包含有一个自动的差错恢复机制,可保证目标企业和运营商市场所要求的可靠数据传输。 MoSys选用了平均同步接口来最大限度地减少与传统串化解串器有关的时延。数据通过控制模块形成管线,然后以位流形式馈送给4个1T-SRAM分区。在发送侧,随着每个分区的依次激活(1ns一个),最多可以读出2个数据字,并返回到GCI接口,再传送给主机。 Bandwidth Engine的另一个创新特性是一个分区一个的片载ALU,可以用来通过内部“读-修改-写”指令操作数据。ALU的使用能够卸载主处理器工作量,并释放出接口资源用于其它操作,从而实现更高的性能和能效。由于ALU与每个分区是关联的,因此工作在10G接口速率时每1ns就能发送一条指令。为了确保通过ALU操作的数据完整性,需要对72位字的ECC特征位进行检查,并在必要时进行纠正和重新计算。 在硅片方面,MoSys选择了台积电(TSMC)作为制造代工厂。器件采用了台积电的嵌入式DRAM工艺,这种工艺基于的是位线下电容技术,如图1所示。通过整合台积电的稳定工艺和公司自己的创新芯片设计,MoSys开发出了成功的器件。与位线连接的检测放大器利用了逻辑兼容的台积电工艺中所有可用的金属层。共使用了三级复用式检测放大器。第一级位线在金属层1中长有20微米,用于将内存单元连接到第一级检测放大器。第二级检测放大器复用了两个第一级检测放大器的输出,在金属层4中经过750微米位线到达第二级检测放大器。最后,8个第二级输出端使用金属层6的750微米位线复用到第三级检测放大器。

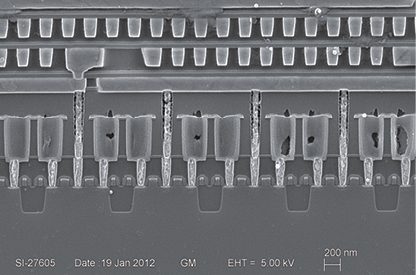

图1:Bandwidth Engine的SEM横断面。 Bandwidth Engine的版图设计也考虑到了主要设计目标--高访问速率和低时延。传统的串化/解串(SerDes)器件将I/O放在芯片的边缘,而Bandwidth Engine改变了这一传统做法,将I/O、Gigachip接口和时钟电路放在裸片的中心。这样做有两大好处:时延可以减少2-3ns,而且延时均衡。将GCI接口和SerDes通道放置在芯片中心还能减少接收器/收发器(Rx/Tx)串扰,允许未来新一代Bandwidth Engine具有相同的引脚输出。这种方法面临的设计挑战是在内存、内核和芯片SerDes之间要保持足够的噪声隔离度。 裸片版图示于图2。在SerDes模块的中心位置有两个可以看到的电感。这两个电感用于组成两个LC振荡器,这两个振荡器则用于两个锁相环(PLL)中的压控振荡器(VCO)。用两个PLL的目的是为了覆盖芯片使用的6-10GHz频率范围。LC振荡器用来创建低抖动PLL。

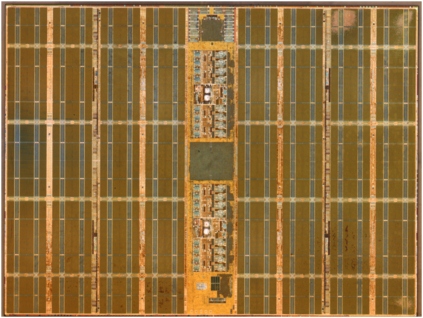

图2:Bandwidth Engine的平面图。注意裸片中间支持电路的放置。 封装是与芯片协同设计的。封装使用了8个金属层,允许设计师灵活地精确调谐封装引线的串联电感。封装电感设计用于补偿寄生焊盘电容。这样可以得到更加清晰的眼图,从而提高反射损耗,降低数据误码率。 为了降低测试成本(当测试仪器必须连接到Bandwidth Engine上的15个通道时测试成本是很高的),芯片上集成了一个专门设计用于测试的处理器。该处理器可以在芯片的制造过程中进行重新编程,因此当从测试期间发现的弱比特特征了解更多信息后允许产品工程师修改测试算法,从而确保达到支持10年寿命目标的企业级与运营级质量和可靠性。未来还可能减少甚至消除这部分程序的下载烧录时间。 总之,这是架构、设计、版图、工艺、测试和制造小组之间一次成功的团队合作,允许Bandwidth Engine达到企业用户要求的每秒20亿次数据访问速率和10年寿命。覆盖Bandwidth Engine设计的专利在一年半以前就提出申请了,目前正在专利申请受理阶段。MoSys在与一级网络伙伴的合作中赢得了多项设计。设计本身是可扩展的,MoSys认为还能进一步改进并用于400GE。下一代产品将有50%的性能提高。 |

网友评论