台积电首提 1nm A10 工艺,计划到 2030 年实现 1 万亿晶体管的单个芯片封装

发布时间:2023-12-28 14:23

发布者:eechina

|

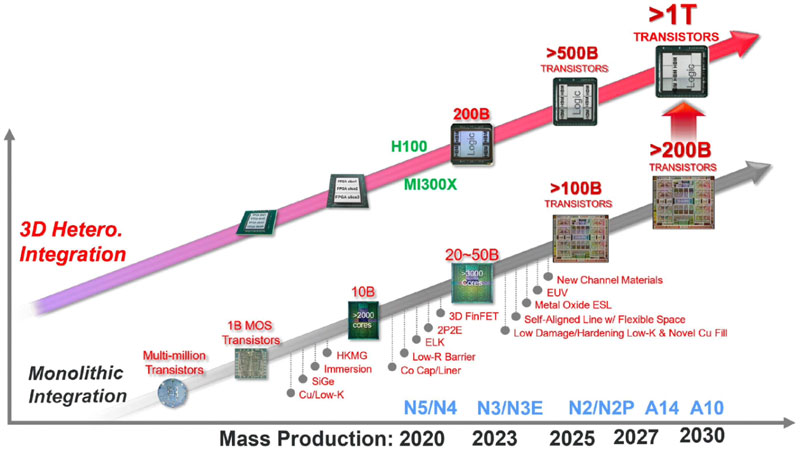

来源:IT之家 据 Tom's Hardware 报道,在本月举行的 IEDM 2023 会议上,台积电制定了提供包含 1 万亿个晶体管的芯片封装路线,这一计划与英特尔去年透露的规划类似。 当然,1 万亿晶体管是来自单个芯片封装上的 3D 封装小芯片集合,但台积电也在致力于开发单个芯片 2000 亿晶体管。 为了实现这一目标,该公司重申正在致力于 2nm 级 N2 和 N2P 生产节点,以及 1.4nm 级 A14 和 1nm 级 A10 制造工艺,预计将于 2030 年完成。

▲ 图源 Tom's Hardware 获取到的台积电 PPT 此外,台积电预计封装技术(CoWoS、InFO、SoIC 等)将不断取得进步,使其能够在 2030 年左右构建封装超过 1 万亿个晶体管的大规模多芯片解决方案。 据IT之家此前报道,台积电在会议上还透露,其 1.4nm 级工艺制程研发已经全面展开。同时,台积电重申,2nm 级制程将按计划于 2025 年开始量产。 |

网友评论