AMEYA360:佰维发布CXL 2.0 DRAM,赋能高性能计算

发布时间:2023-12-27 16:20

发布者:AMEYA360皇华

|

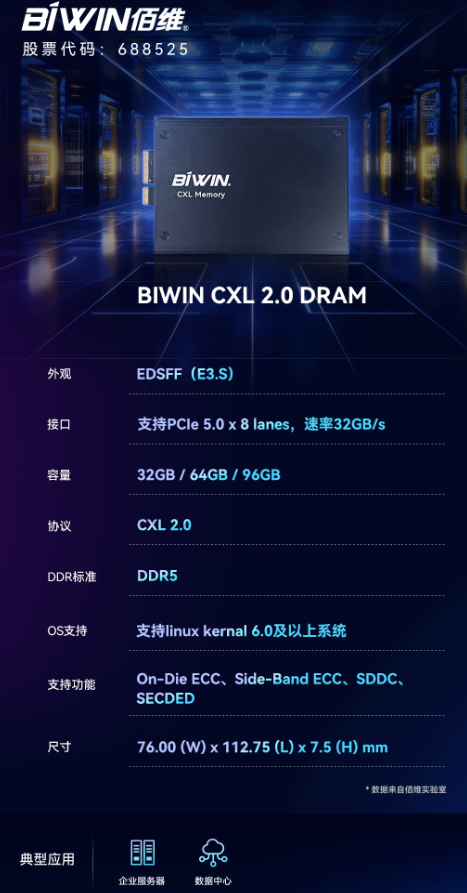

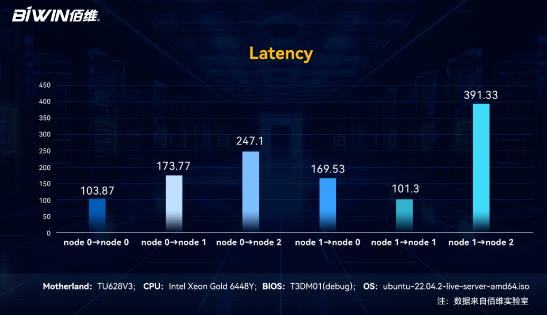

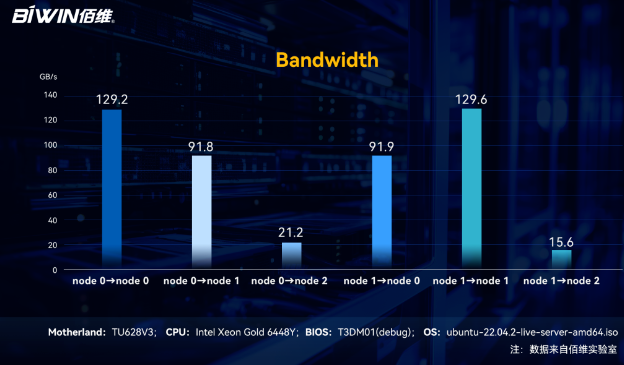

导语:CXL是一种开放式全新互联技术标准,可在主机处理器与加速器、内存缓冲区、智能I/O设备等设备之间提供高带宽、低延迟连接,从而满足高性能异构计算的要求,并且其维护CPU/GPU内存空间和连接设备内存之间的一致性,突破内存墙瓶颈,缩减整体响应时间。此外,CXL支持部署新的内存层,可以弥合主内存和SSD存储之间的延迟差距。 随着AI应用爆发,“内存墙”成为制约计算系统性能的主要因素之一。CXL建立在PCIe的物理和电气接口之上,CXL内存扩展功能可在服务器中的直连DIMM插槽之外实现额外的内存容量和带宽,支持内存池化和共享,满足高性能CPU/GPU的算力需求。 近日,佰维成功研发并发布了支持CXL 2.0规范的CXL DRAM内存扩展模块。佰维CXL 2.0 DRAM采用EDSFF(E3.S)外形规格,内存容量高达96GB,同时支持PCIe 5.0×8接口,理论带宽高达32GB/s,可与支持CXL规范及E3.S接口的背板和服务器主板直连,扩展服务器内存容量和带宽。同时,佰维可针对无E3.S接口的服务器背板提供CXL AIC转接卡。  佰维CXL 2.0 DRAM的特点和优势 1搭载高性能内存扩展控制器,遵循CXL2.0 Type3标准,支持PCIe5.0x8接口,理论带宽高达32GB/s。 2严选优质DDR5内存颗粒,容量高达96GB。 3支持On-Die ECC、Side-Band ECC、SDDC、SECDED等功能。 4允许多达16台主机同时访问内存的不同部分,支持内存池化共享。 5同步开源发布CXL DRAM软件工具包,以确保用户无障碍部署CXL扩展内存。工具包特点:可提供CXL的显示,隐式API,客户可根据不同应用场景进行使用;可提供应用层级的CXL的numa工具使用方法,建立应用层级对CXL的直观感受。 Latency性能方面,在实际测试中,佰维CXL 2.0 DRAM挂载于node 2节点,与挂载于node 0节点的CPU存取Latency为247.1ns,带宽超过21GB/s,Latency性能优异,赋能数据高速处理。   人工智能(AI)和机器学习(ML)对高速数据处理的需求持续增长,佰维CXL 2.0 DRAM兼具支持内存容量和带宽扩展、内存池化共享、高带宽、低延迟、高可靠性等特点,赋能AI高性能计算。目前,佰维可为客户和合作伙伴提供32GB~96GB CXL 2.0 DRAM的功能样机,进行联合评估和测试。未来,佰维将持续关注CXL技术,赋能高性能计算需求。 延伸:AIC转接卡 针对无E3.S接口的服务器背板,佰维可提供AIC转接卡,助力服务器实现CXL RDIMM内存扩展。文章来源:http://www.ameya360.com/hangye/111071.html |

网友评论