为什么FPGA在原型验证中越来越重要?

发布时间:2022-3-10 10:59

发布者:eechina

|

当前,智能手机AP(应用处理器)的迭代周期已经缩短到每年一次。事实上现在消费电子很多SoC(片上系统)都是每年更新一代产品,甚至是一些定制性的ASIC(专用集成电路)也在以12-18个月的周期进行升级。与此同时,随着芯片制造工艺越来越先进,芯片设计的复杂度呈指数级增长。这种近乎矛盾的发展趋势让芯片设计公司面临着巨大的创新压力,同时先进工艺高昂的量产成本进一步增加了企业的经营风险。 在这样的大背景下,芯片设计公司对基于FPGA的原型验证更加重视,越来越多的芯片选择用FPGA进行设计评估,包括功能验证和时序验证等,以确保所设计的芯片和需求相匹配,应对资金和时间带来的巨大挑战。本文将为大家介绍FPGA原型验证的魅力,以及贸泽电子在售的极具市场竞争力的FPGA产品和相关的开发套件。 FPGA原型验证的魅力 FPGA是一种应用广泛的芯片,在通信、计算、控制等领域都能看到它的身影,而将RTL移植到FPGA来进行芯片原型验证,在ASIC、ASSP(专用标准产品)和SoC等从设计到制造的过程中也已经是不可或缺。 随着制造工艺进入7nm、5nm,甚至是更先进的3nm、2nm,成功设计一颗芯片要考虑的因素越来越多。原型验证的目的是在芯片流片之前,尽可能地还原芯片真实的应用场景,提升开发效率,降低开发成本。从具体的执行步骤来看,基于FPGA的原型验证主要包括FPGA选型、定制或者购买原型板、芯片转FPGA、调试启动FPGA原型、软硬件协同验证、现场认证等。确实,鉴于芯片的复杂度与日俱增,原型认证不仅会验证芯片的基本功能,同时也会在现实的使用环境中做更完善的认证保障。 当前,FPGA已经被用于验证相对成熟的RTL。从芯片设计角度来划分,主要会包括RTL0、RTL1、RTL2、RTL3、GLS、TO六大环节,所涵盖的验证内容包括芯片定义、子模块实现、系统实现、门级表验证。当所有这些环节都没有问题的时候,最终环节就是TO流片,芯片开始进入到制造量产环节。 无论是FPGA角度还是RTL角度来切分流程,基于FPGA做芯片的原型验证已经是行业广为认可的方案,在纯硬件和软硬件方面都能够提升效率。在纯硬件方面,虽然目前单片FPGA已经不足以验证先进制程上面的芯片,但方案商通过创新方案能够将多个FPGA芯片组合成一个硬件系统,并克服了子模块信号传输大于FPGA自身I/O接口数的问题。这依然是一个近乎精确的以高速运行的芯片复制品,且极具性价比。 在软硬件协同环节,目前采用FPGA做系统验证具有不可替代性。FPGA的可编程特性带来了极高的可操作性,让软硬件可以并行开发。芯片公司的合作伙伴可以更早地基于FPGA平台做软件和应用开发,显著缩短了产品上市的周期。 综合而言,基于FPGA做原型验证,可以加快芯片设计速度,帮助设计公司降低流片失败的风险,并通过软硬件协同的特性缩短下游产品的上市周期。随着芯片制造工艺越来越先进,这种优势会愈发明显。 高容量FPGA的理想之选 相信从事芯片原型验证相关工作的工程师朋友都对Xilinx的Virtex-7 FPGA系列不陌生。其在芯片原型验证方面有诸多优点,包括更优的功耗性能比架构、DSP性能以及I/O带宽等。 贸泽电子在售的XC7VX485T-2FFG1158I型号FPGA是Virtex-7系列FPGA中的一款。

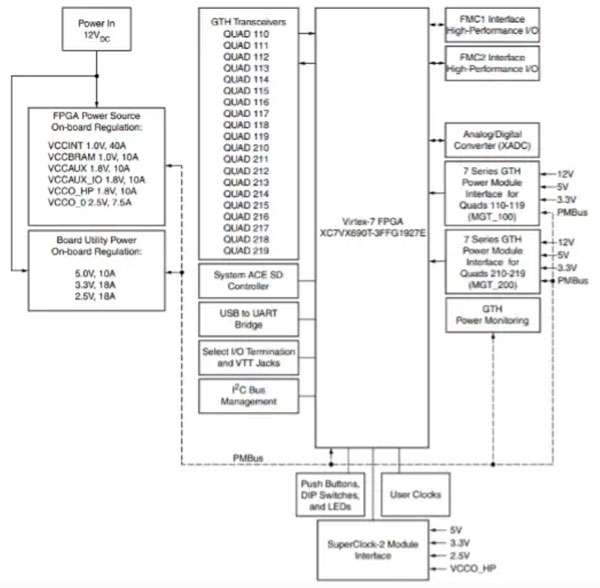

图1:XC7VX485T-2FFG1158I示意图(图源:Xilinx) Virtex-7属于四大Xilinx 7系列之一,其他三个FPGA系列是Spartan-7、Artix-7和Kintex-7。Xilinx 7系列FPGA基于低功耗(HPL)、28nm、高K金属栅极(HKMG)工艺技术打造,Virtex-7系列对28nm系统性能和集成进行了优化,属于Xilinx 7系列中的高端系列,提供: · 多达200万逻辑单元 · 6.8B个晶体管 · 多达96个高级串行收发器 · 68Mb的块RAM · 3600个DSP模块 · 5335 GMAC/s的DSP · 1200个I/O接口 在信息传输方面,Virtex-7系列FPGA提供28.05Gb/s的传输速度,2784Gb/s的串行带宽,1866Mb/s的存储速度。同时,数以千计的SLL(Super Long Line)连接资源和跨越SLR的超高性能时钟线路,使得Virtex-7系列FPGA在高容量FPGA中具有领先同时代产品的绝对实力。 原型设计与验证是Virtex-7系列FPGA的典型应用。该系列产品在设计之初就考虑到了SoC原型设计,能够实现高级调试、仿真加速和交互式设计微调。同时设计者借助Xilinx Vivado设计套件,还可协同优化设计流程,进一步降低成本和流片风险,并提高设计效率,缩短产品的上市周期。 讲了这么多,你一定对Virtex-7系列FPGA心动了,但单纯凭借器件参数有些工程师朋友还把握不准该系列FPGA的性能表现。不要担心,大家可以通过贸泽电子在售的Virtex-7 FPGA VC7215特性描述套件深入了解,这款套件的制造商编号为CK-V7-VC7215-G。 VC7215特性描述套件可以支持Virtex-7系列FPGA中的多款产品,包括XC7VX415T、XC7VX485T和XC7VX690T等。图2是该套件的系统框图,用户可以借此对Virtex-7系列FPGA产品的收发器性能进行评估,还可以完成硬件开发、设计工具、IP和预验证参考设计。

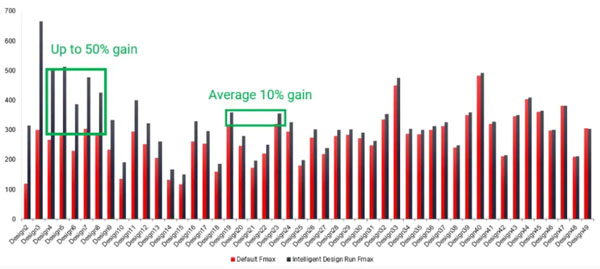

图2:Virtex-7 FPGA VC7215特性描述套件系统框图(图源:Xilinx) 该套件提供的Vivado Design Suiter软件能够极大地提升原型验证的效率。这款软件基于突破性的全新ML算法,能够加速设计收敛。如下图3所示,这套软件能带来平均10%、高达50%的突破性结果质量(QoR)提升。另外,这套软件提供的协同设计环境是业界首个采用模块化设计的图形化IP流程,能够借助团队的设计助力提升生产力,高级DFX功能则能带来5倍平均编译时间减少。

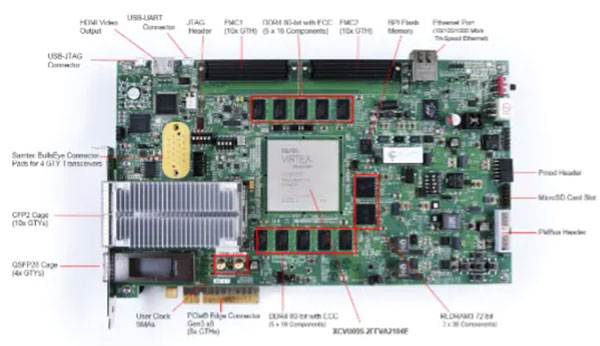

图3:QoR提升效果(图源:Xilinx) Virtex-7 FPGA VC7215特性描述套件上面的BullsEye连接器带来了强大的扩展能力,可连接各种评估平台,包括背板、光学评估板和高速测试设备。每一个BullsEye连接器均可处理1个完整的GTH Quad、4个发送/接收对以及2个独立的参考时钟,从而能够以极灵活的方式测试定制应用。 当然,随着芯片制造工艺的精进与需求复杂度的提升,部分ASIC和SoC原型设计与验证需要更大型的FPGA平台。而Xilinx UltraScale架构无疑提供了功能更强大的解决方案,包括高逻辑容量、超过90%的器件利用率、堪比ASIC的时钟、增强型布线和面向引脚多路复用的高速收发器简化设计分区。 UltraScale架构下的FPGA无疑是为了复现更复杂的ASIC和SoC功能,能够大幅提升复杂原型设计的灵活性。而要深入了解这些领先的器件,可以借助贸泽电子在售的FPGA评估套件。 比如Xilinx VCU108评估套件便是用于开发和评估Xilinx UltraScale XCVU095-2FFVA2104E器件,制造商编号为EK-U1-VCU108-G。通过下方的VCU108评估板布局图能够看出,该评估板提供很多评估系统的通用功能,包括DDR4和RLD3组件存储器、一个高清多媒体接口(HDMI)、一个四通道小型可插拔(QSFP+)连接器、一个八通道PCI Express接口、一个以太网PHY、通用I/O和两个UART接口。

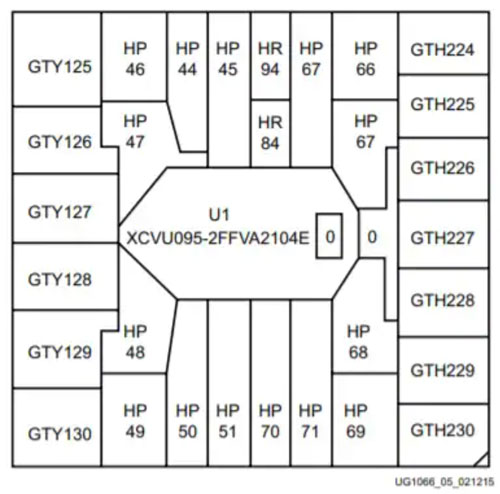

图4:VCU108评估板布局图(图源:Xilinx) 作为系统核心,XCVU095-2FFVA2104E这款FPGA提供了117.6万个逻辑单元。而正如下图5所示,在VCU108评估板上,XCVU095-2FFVA2104E器件共提供了17个I/O bank,为器件功能体验提供了更高的灵活性。因此该评估套件可以为需要大量数据流和数据包处理的原型设计系统(比如400+Gbps系统、大规模仿真和高性能计算)提供一个出色的平台。

图5:VCU108评估板I/Obank分布(图源:Xilinx) 复杂系统下的成本效益 开发套件给了我们一个快速了解器件的捷径,通过贸泽电子在售的Intel Cyclone开发工具便可以评估Intel Cyclone FPGA。这款开发套件的制造商编号为DK-DEV-5CGTD9N,工程师朋友可以直接借助开发工具进行再创新,不仅可用于嵌入式视觉、工厂自动化等应用的开发设计,也是概念验证的理想起点。

图6:Intel Cyclone开发工具(图源:Intel) 作为板子的核心,Intel Cyclone V 5CGTD9 FPGA在FPGA行业面向6.144 Gbps收发器应用的所有产品中,成本和功耗都很低,且自带DSP模块,因此在嵌入式视觉、工厂自动化等应用极具性价比。同时,这块FPGA作为Cyclone V系列产品中配置极高的一款,提供301000个逻辑单元,嵌入内存高达13.917Mb,加上Intel提供的包括软件、知识产权(IP)、设计实例等在内的配套支持,将这款开发套件用于概念验证同样方便易用且具有成本优势。 为了适应ASIC和SoC日益复杂的系统,Intel更推荐IC设计人员采用Stratix®10 GX系列,以合理成本实现高集成度的原型验证解决方案,可实现更短的上市周期、更快的验证速度和更高的系统集成。 在基础性能方面,Intel Stratix®10 GX系列可提供1020万个逻辑元件、2304个用户I/O引脚、308Mb内存以及高达17.4Gbps的带宽,如果你的芯片设计更强调收发器的性能和灵活性,比如以太网相关应用,Intel Stratix® 10 GX系列在单独的收发器块上配备多达96个通用收发器,可提供2666Mbps DDR4外部内存接口性能。这样领先的配置再加上Intel提供的丰富的用户指南,无疑让Stratix® 10 GX系列非常适合ASIC原型设计和系统仿真。 现在,你可以通过Stratix®10 GX FPGA开发套件深入了解这个系列的FPGA产品,开发套件在贸泽电子上的制造商编号为DK-DEV-1SGX-L-A。

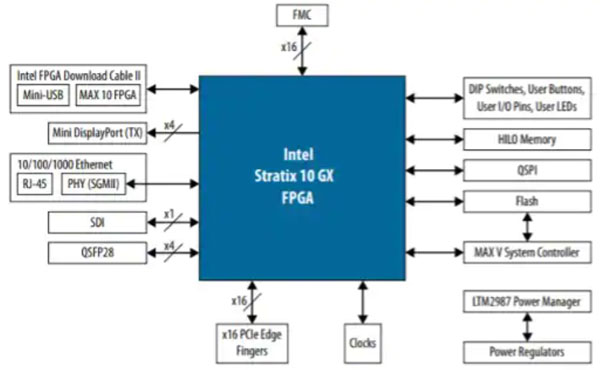

图7:Stratix®10 GX FPGA开发套件(图源:Intel) 下方图8是Stratix®10 GX FPGA开发套件的系统框图,能够看出该开发套件围绕核心——Stratix® 10 GX FPGA打造了一个非常完整的开发环境。丰富的接口资源包括PCIe x16边缘连接器、串行数字接口(SDI)通道和FMC低引脚数(LPC + 15收发器)连接器等,可直接用于开发和测试PCIe 3.0设计以及由DDR4、DDR3、QDR IV和RLDRAM III存储器组成的存储器子系统。

图8:Stratix®10 GX FPGA开发套件的系统框图(图源:Intel) 在支持工具方面,Quartus Prime Pro软件是Stratix®10 GX FPGA开发套件的一大亮点,提供设计和开发Intel FPGA、SoC和CPLD所需的一切,从设计输入和综合到优化、验证和仿真。其中,Quartus Prime Pro Edition主要用于FPGA应用。 让原型验证更高效 半导体产业的共识是FPGA是一个门槛相对较高的领域,当用于ASIC和SoC的原型验证和系统仿真时更是如此。而贸泽电子销售的开发套件无疑帮助降低了这一门槛,提供了解和进一步开发FPGA相关应用所需的完整软硬件配套,让工程师朋友享受来自可编程的无限乐趣。 来源:贸泽电子 作者:Doctor M |

网友评论