用于扇出型面板级封装嵌入式线路和2合1 RDL

发布时间:2020-9-2 16:37

发布者:eechina

|

作者:Kesheng Feng, Kwangsuk Kim, SamindaDharmarathna, William Bowerman, Jim Watkowski, Johnny Lee, Jordan Kologe[MacDermid Alpha Electronics Solutions] 相比扇出型晶圆级封装(FOWLP),扇出型面板级封装(FOPLP)的镀铜性能和封装成本降低都一直是挑战,制造商一直难以回收安装工艺的前期成本。关键的挑战是如何从形成高膜厚均匀性且高解析度的再分布层(RDL)电镀铜线路。尤其在同时电镀线路和填盲孔时(即2合1(RDL)电镀)时,这非常有挑战性。镀铜线路,铜垫和/或填盲孔的表面之间的共面性对于这些镀铜工艺至关重要。非共面的表面可能会导致信号传输损失以及压合后电路层的变形。这些缺陷可能导致短路和灾难性的故障。由于线路的尺寸等级更为精细,采用减铜平面化工艺来恢复共面性可能会导致在该层中产生对位误差。因此,能够提供均匀的表面线路而不需要额外后处理的镀铜工艺是成功实现面板级封装的RDL镀层的关键。在本文中,我们介绍了可为FOPLP形成镀铜金属化的制造技术的背景,讨论了该应用对铜电镀的化学和设备影响,并调查了嵌入式线路和2合1 RDL电镀的商用电镀系统的性能。 SAP, mSAP, 和ETS技术 目前用于FOPLP的RDL制造技术包括半加成法(SAP),改进的半加成法(mSAP)和嵌入式线路电镀。SAP已经用于在有机基材上制作细线。该制程始于化学沉铜以形成超薄导电种子层,然后进行光刻以在表面上形成光阻的图案。然后使用电镀铜在光阻图案之间形成金属化结构。然后,去除光阻并快速蚀刻掉铜晶种层以完成线路图案。SAP已经先进到可以将布线尺寸缩小到9μm,但是由于在快速蚀刻步骤中,镀铜线路会发生少量的侧蚀,因此进一步减小线宽比例一直是一个挑战。随着线宽/间距趋势接近9μm / 9μm,还存在其它挑战,包括与有机载板的粘附力,面板上(尺寸在500mm x 400mm范围内)不平整表面上的设备精准度能力,电镀厚度均匀性以及专用设备(例如高级光刻工具)的高成本。 mSAP是一种更新的制程,已通过有效地实现设备中印刷电路板(PCB)和集成电路(IC)载板的用途,广泛应用于减小移动电子设备的电路尺寸。典型的mSAP制程始于厚度约为1-5μm的非常薄的铜箔有机基材。然后进行激光钻盲孔,之后电浆或化学除胶渣或两者结合对面板除胶渣。该制程清除了目标焊盘上的所有树脂残留物,并使孔壁的外形可以粘附后续的铜沉积物。然后,通过诸如化学沉铜,碳系统或导电高分子聚合物的直接电镀金属化制程来处理面板,活化孔壁以利进行电镀铜。随后对面板进行成像并用电镀铜进行图案电镀,将铜完全填充到盲孔中,并在单一个步骤中将铜线路构建到所需的高度。电镀后,剥离光阻,并进行差异或快速蚀刻以形成最终电路。该技术的细线解析率通常限制为13μm。 嵌入式线路载板(ETS)电镀技术可提供额外的成本降低和更高的解析度优势,而无需进行快速蚀刻步骤,从而使细线解析度达到5μm。ETS技术使用光刻工艺在导电载体上创建镀有图案的铜金属化结构。将这些结构压合到电介质中以嵌入电路,然后使用mSAP或SAP类型的制程进行增层构建。

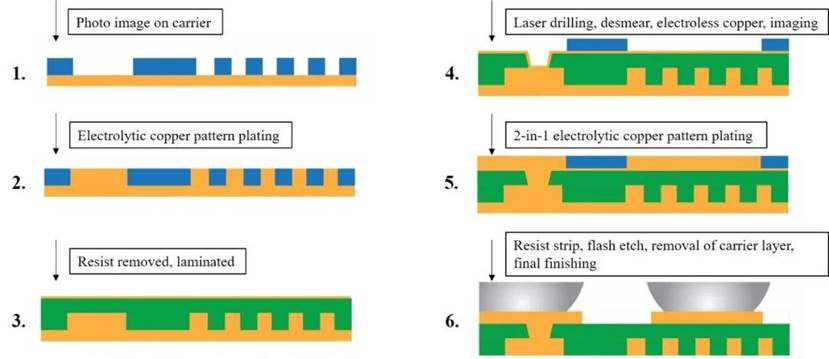

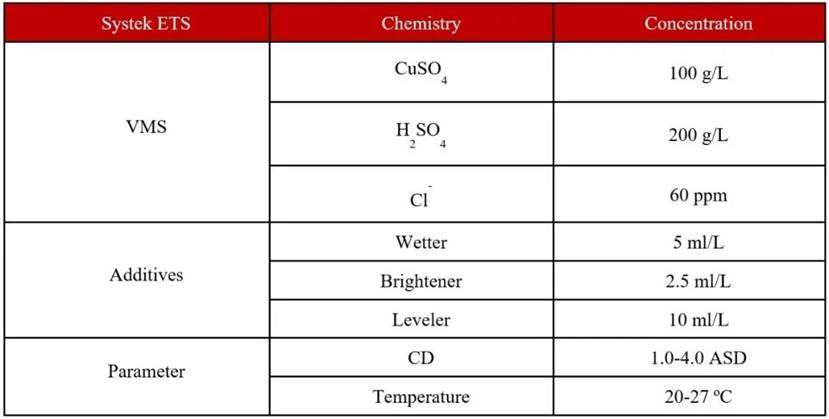

图1. 将嵌入式线路载板技术(步骤 1、2、3 和 6)和 mSAP 技术(步骤 4、5 和 6)组合在一个流程中。 图1描述了通过结合使用ETS和mSAP制程分6个步骤制造面板级载板的工艺。ETS技术涉及在步骤1和2中所示的线路成像之后,采用光刻工艺在导电载体上创建镀有图案的金属化结构。然后将生成的细线路压合到介电质上,以嵌入电路,从而在步骤3中形成M1。在使用mSAP技术对基材进行M2层和M3层之后,在步骤6中除去导电载体。mSAP制程从第3步开始,在有机基材上形成厚度约为1-5 μm的薄铜箔,以实现良好的附着力。如步骤4和步骤5所示,该铜箔与化学沉铜一起通过电镀制程进行电镀,以形成M2或M3层,该层可同时包含细线RDL和盲孔。这是前面提到的2合 1电镀步骤。在快速蚀刻薄铜箔之后,在步骤6中除去覆盖嵌入式线路的铜载体。 影响镀铜质量的因素 典型的酸性铜电解系统包含硫酸铜、硫酸、氯离子和有机添加剂。这些添加剂在控制沉积物分布以及铜沉积物的物理性质方面起着至关重要的作用。为了达到电镀制程的特定目标,必须对这些添加剂进行适当的监控。当将添加剂控制在给定范围内以提高镀层均匀性时,它们可以组合使用。这些添加剂是润湿剂、光亮剂和平整剂。润湿剂在存在氯离子的情况下起作用,以吸附到阴极上并增加扩散层的有效厚度。结果,阴极处的电镀电流增加并且沉积物变得更均匀,因此可以获得密集堆积的铜沉积物而不会烧板。这种改进的扩散层改善了细线镀层中沉积物的分布。光亮剂减少了抑制作用,并用作晶粒细化剂以沉积具有随机取向的细铜晶粒结构。由于光亮剂对整体晶粒结构的强大影响,光亮剂对沉积物的物理性能(例如抗张强度和延展率)的影响最大。 平整剂是一种温和的抑制剂,可吸附到特定位置,例如基材的拐角和峰顶,有助于使铜沉积物的厚度均匀。在面板表面的微形貌内,扩散层往往在峰值处较薄而在谷部较厚。没有平整剂,电镀铜会夸大微形貌,从而导致更高的峰。另一方面,如果存在平整剂,则峰上的镀层将受到抑制,微形貌将减小。正确的添加剂选择和控制对于获得电镀均匀性和电镀铜的理想物理性能至关重要。除了选择和优化添加剂外,还必须考虑阳极类型、VMS和电镀电流密度,因为它们会对电镀性能产生影响。 FOPLP的商业电镀评估 在以下各节中,我们调查了商用嵌入式线路电镀系统的电镀能力。我们描述的电镀制程是为厚度不超过2至3层的面板级封装板设计的。我们还展示了通过改变VMS中铜和酸的浓度比,但使同一电镀添加剂系统用于二合一RDL电镀的结果。通过测量细线、焊盘的共面性,膜厚均匀性,以及在面板级类型的载板上填盲孔来评估性能。我们比较了可溶和不可溶阳极对电镀均匀性的影响,并通过XRD和FIB-SEM成像检查了沉积物的晶粒结构。样品的电镀在大批量生产条件下在垂直连续电镀(VCP)设备中进行。通过循环伏安法剥离(CVS)分析,严格控制所有添加剂成分。 嵌入式线路电镀 对于嵌入式细线电镀,我们使用表1中所列的商标为Systek ETS的电镀系统。所使用的测试板是带有光成像干膜图案的载体,其厚度为25μm。在进入含镀铜添加剂系统的酸性镀铜之前,每个测试板都要经过1分钟的酸清洁剂、1分钟的水洗和1分钟的10%硫酸的预清洁处理。 表1. ETS 电解液和电镀参数

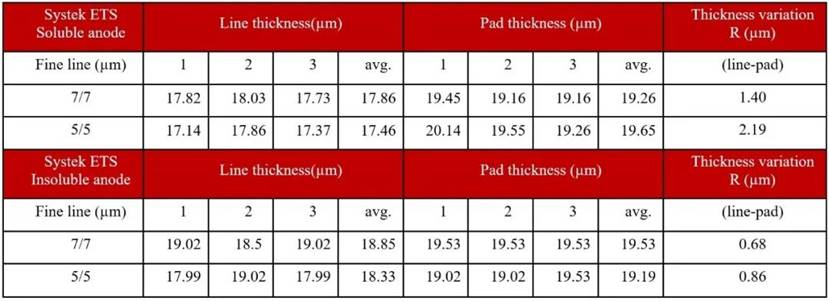

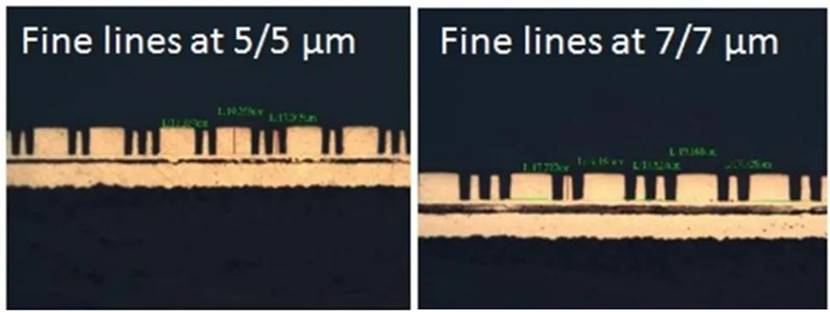

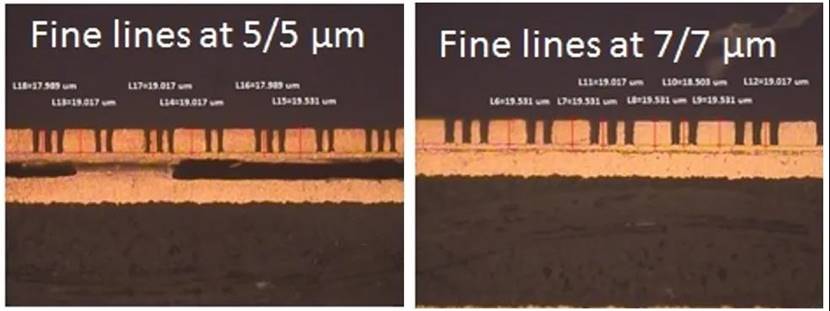

表2说明了阳极类型对使用上述电镀系统的VCP设备中细线和孔电镀均匀性的影响的示例。将面板以1.5 ASD的速度电镀60min,获得约20μm的铜厚度。从横截面测量了宽度为5μm或7μm的细线和较大焊盘之间的电镀高度变化,如图2和3所示。当设备使用可溶阳极操作时,细线和焊盘之间的电镀高度变化在线宽为5μm的面板上为1.4μm,在线宽为7μm的面板为2.19μm。当设备使用不溶性阳极进行操作时,对于5μm和7μm线宽的面板,细线和焊盘之间的电镀高度变化均低于1.0μm。该数据示于表2。 表2. 阳极类型对嵌入式线路中细线和铜垫变化的性能影响

图2. 使用可溶性阳极的电镀工艺细线的横截面

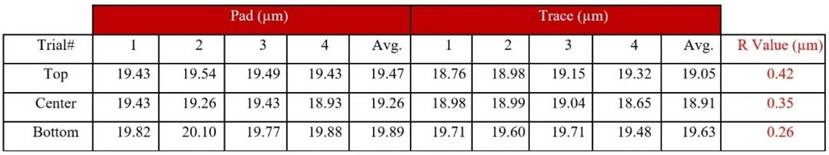

图3. 使用不溶性阳极的电镀工艺细线的横截面 除了具有均匀性控制优点外,不溶性阳极也易于维护,并允许施加更高的电镀电流密度。对于更大的线宽,该制程具有更严格的控制。对于宽度为10μm的细线,以1.5 ASD的电流密度进行电镀时,电镀铜的高度变化低于0.5μm。在4 ASD的较高电流密度下,厚度变化约为1μm。众所周知,当降低电镀电流密度时,可以提高电镀均匀性。 尺寸为410mm x 510mm的整个面板级载板的镀层厚度变化小于0.5μm。在面板的顶部、中央和底部进行测量可以评估整个面板的均匀性。该数据列于表3。 表3. 单位以及面板内细线和铜垫之间的电镀厚度变化

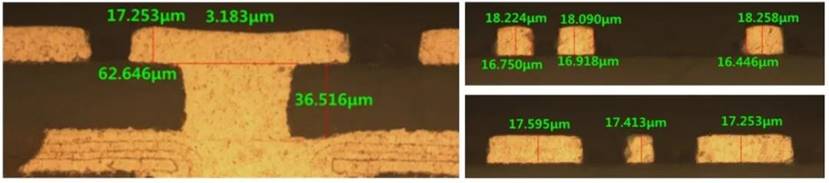

同时进行细线电镀和填孔二合一电镀 对于包含盲孔和细线的RDL应用,电镀液要保持良好的孔填充能力,同时还要在细线上获得良好的均匀性和共平面性是一个挑战。我们发现把电解液VMS的硫酸铜含量调整为220 g/L、硫酸含量调整为50 g/L可以使制程填60 x40μm的盲孔且凹陷小于5μm(表4)。在这些条件下,宽度为15μm的细线与较大焊盘之间的电镀高度变化约为1.0μm(图4)。 表4. 填孔时细线和铜垫之间的电镀厚度变化。

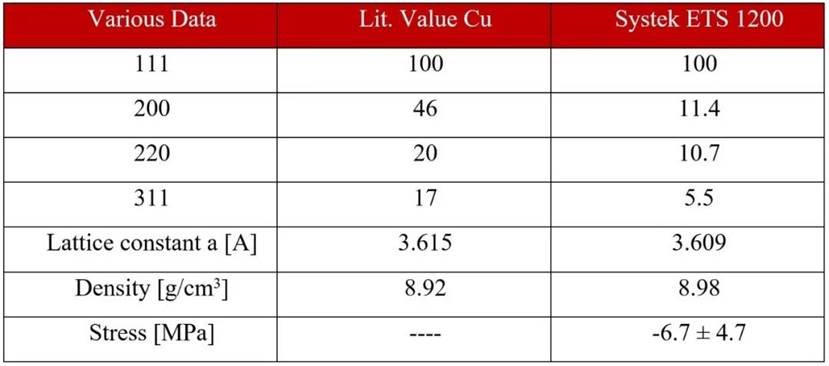

图4. 细线和填孔的横截面和测量数据。 沉积铜的物理性质 电镀铜沉积物的物理性质对于基材的可靠性至关重要。一些最重要的物理性质是抗拉强度、延展率和内应力,这些性质表明了沉积物对热应力和弯曲的耐受性。使用标准测试设备测量沉积物的抗拉强度、延展率和内部应力。使用该制程电镀的铜具有大于36,000psi的拉伸强度和大于18%的延展率。由于现代封装RDL需要极小的尺寸,因此铜金属的内部应力是重要的参数。内部应力较高时,沉积物可能会弯曲,并且随着时间或温度的变化弯曲可能会变得更糟。该制程在各种电流密度下的镀层沉积物均显示出低应力-低于1.0Kg / mm2。 沉积铜晶粒结构 在1.5 ASD的电流密度下对镀层进行了X射线衍射(XRD)研究,以识别晶相和不同平面。获得的铜晶粒的衍射图与文献中给出的铜的标准相同。除了晶体方向的相对强度之外,在确定是否存在最佳方向时,晶体密度和晶格常数也很重要。数据表明,槽液中的沉积物具有优选的[111]平面,如表5所示。 表5. 铜沉积物XRD 数据

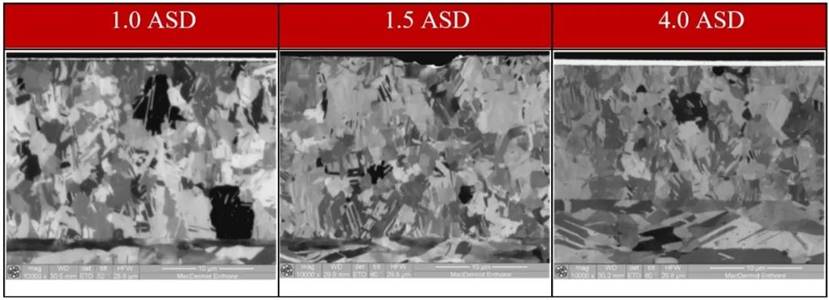

聚焦离子束扫描电子显微镜(FIB-SEM)照片显示,镀铜沉积物具有等轴晶粒结构,在不同的电镀电流密度下变化不大(图5)。

图5. 铜沉积FIB/SEM图片在不同的电镀电流密度下。 结论 面板级封装对电镀铜金属化系统提出了独特的挑战。通过适当选择VMS电解液和设备,先进的封装制造商可以达到所需的共平面度,可以为RDL实现嵌入式线路和2合1电镀。可以使用用于嵌入式线路电镀的商用电镀系统,该系统可以提供足够的性能,甚至可以进行调整以及微调VMS以达成2合1细线电镀和填盲孔。这些镀铜制程的物理性能,抗拉强度和延展率均符合IPC Class III规范,并且在电镀后和退火后具有较低的内应力,从而提供了可靠的沉积物,能较好地承受组装和使用设备时的应力。 参考文献 [1]. H. Akahoshi, M. Kawamoto, T. Itabashi, O. Miura, A. Takahashi, S. Kobayashi, "Fine-line circuit manufacturing technology with electroless copper plating," IEEE Trans. on Components, Packaging, and Manufacturing Tech.: Part A, vol. 18, pp. 127-135, 1995. [2]. Y-H. Chen, S-L. Cheng, D-C. Hu, T-J. Tseng, “L/S ≤5/5μm line embedded organic substrate manufacturing for 2.1D/2.5D SiP application,” IMAPS, Nov. 2015. [3]. C. Chen, M. Lin, G. Liao, Y. Ding, W. Cheng, “Balanced embedded trace substrate design for warpage control,” IEEE Elec. and Comp. Tech. Conf., May 26–29, 2015, pp. 193–199. [4]. Y. Li, D. Goyal, 3D Microelectronic Packaging From Fundamentals to Applications, Springer, Jan. 20, 2017 - Technology. [5] S. Dharmarathna, et al., “High throw DC acid copper formulation for vertical continuous electroplating processes,” IPC APEX Expo 2017, San Diego, CA, Feb. 14-16, 2017. [6]. Y. Zhang, G. Ding, P. Cheng, H. Wang, “Numerical simulation and experimental verification of additive distribution in through-silicon via during copper filling process,” Jour. of The Electrochemical Soc., 162 (1) D62-D67 (2015). |

网友评论