基于CPLD控制的DDS数字频率合成器设计

发布时间:2010-11-7 20:04

发布者:techshare

|

DDS是直接数字合成(Direct Digital Synthesis)技术的简称,是近年来随着数字集成电路和计算机的迅猛发展而出现的一种新的频率合成技术。该技术从相位概念出发来对频率进行合成。它采用数字取样技术,将参考信号的频率、相位、幅度等参数转变成一组取样函数,然后直接运算出所需要的频率信号。由于是全数字结构,其输出信号中含有大量杂散谱线。另外,其超宽频带信号也将遇到谐波电平高,从而难以抑制谐波等问题。这些问题严重影响了DDS输出信号的频谱纯度,也成为限制其应用的主要因素。本文提出了一种解决此问题的电路方案,并对如何改善信号源的频谱质量进行了讨论。 1 AD9952芯片介绍 1.1 AD9952的主要特点 AD9952是ADI公司2003年推出的新产品。该芯片能以早期DDS芯片十分之一的功耗提供速度高达400MHz的内部时钟,可合成高达160 MHz的频率。AD9952的主要性能如下: ●具有高达400MHz的内部时钟,可单端或双端差分输入,并附有PLL参考时钟和可编程乘法器(4倍~20倍)。 ●超低功耗,1.8V时的功耗小于250mW。 ●内部集成有14位DAC和超高速比较器,可产生高稳定度的方波输出。 ●内含32位相位累加器和19位正弦查询表ROM。 ●含有可编程的相位/幅度抖动电路;可以减小由于相位截断和DAC量化误差带来的杂散。 ●DAC输出相位噪声小于-125dBc/Hz/1kHz;动态性能为:80dB SFDR@130MHz(偏移±100kHz)。 ●采用2线或3线串口控制,48脚EPAD-TQFP封装形式。  1.2 AD9952的结构原理 AD9952的内部功能框图如图1所示。 AD9952共有6种时钟输入模式,通过ClkMode-Select管脚、CFR2<0>和CFR2<7?3>(CFR2为24位的第二控制功能寄存器)可决定使用哪种模式。 PLL的控制则通过控制功能寄存器的5位参考时钟倍乘器来实现(即CFR2<7?3>)。当编程数据在0X04~0X14(十进制即:4~20)之外时,PLL被旁路,此时PLL处于节电状态。实验证明,直接使用参考晶振作时钟时,其输出信号的相噪、杂散电平、SF-DR性能比使用倍乘器时有较大的改观;而付出的代价是必须采用频率较高的晶振,成本有所增加。 AD9952中的14位DAC可输出两路互补信号,这种差分形式的输出可减少DAC输出可能存在的共模噪声,提高信噪比。输出电流由连接在DAC_RSET管脚与DAC地之间的Rset决定: Rset=39.19/Iout 最大输出电流为15mA,但是从最优化SFDR的角度考虑,一般取输出电流为10mA。 AD9952采用单点频工作模式,与其他芯片相比功能上有些单一。凡是存储在FTW0中的控制字就会被提供给相位累加器进行累加;将一个新的控制字写入FTW0并发出I/O UPDATE命令即可改变输出频率值。通过相位偏置寄存器可以调整输出信号的相位。  AD9952内部共有16个8位控制寄存器,可分别用来控制输出信号的频率、相位、幅度、同步以及器件操作等。与ADI公司先前的系列产品不同,AD9952只采用串口进行控制。该串口可兼容多种同步传输格式,如:MOTOROLA 6905/11 SPI和IN-TEL8051 SSR协议等。 在AD9952的串口操作中,表1所列的指令字(Instruction Word)具有重要作用。其中指令字A<4:0>用于指定具体哪一个寄存器被访问;MSB位为高时,进行读操作;为低时,进行写操作。 表1 AD9952的指令表

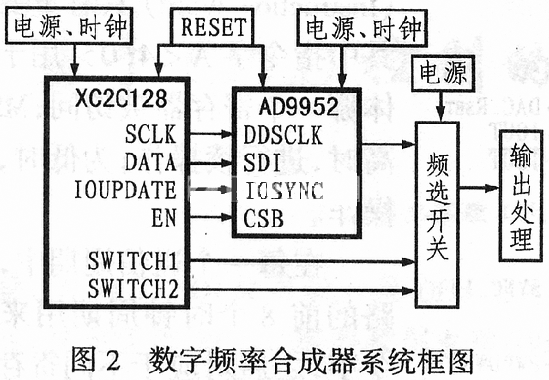

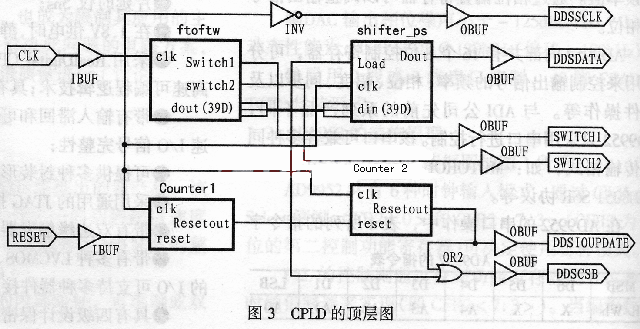

在每一个通信周期中,控制电路的前8个时钟周期用来写入指令字,之后对应于不同寄存器的数据被串行输入到AD9952,传送的字节数与被访问的寄存器有关。比如:当需要访问CFR2寄存器时,由于CFR2是3个字节,所以,指令字后的3字节就默认为是需要传送的内容。传完3字节,一个通信周期也就完成了。 2 XC2C128芯片介绍 XC2C128是Xilinx公司CoolRunnerⅡ系列中有128个宏单元的CPLD器件。这种器件包含了16个内部互联的功能块(AIM)?每个AIM能为功能块提供40个输入,每个功能块包含16个宏单元,这些宏单元同时包含了大量的配置寄存器。 另外,这些寄存器能被全局预置和复位,也可以被提前设置成D或T触发器。可以有多种时钟信号,分别为全局或局部的电路服务。例如在同步时,可以同时应用三个不同的时钟信号。 下面是XC2C128的一些主要特性: ●可采用1.5V、1.8V、2.5V、3V、3.3V等电源供电,XC2C128内部有两个BANK,因而允许采用不同电压供电而不需电压转换器: ●片延时仅5ns; ●在1.8V供电时,静态电流可低至25μA; ●采用RealDigital CPLD技术和先进的低功耗高速可编程逻辑技术;具有低至33μW的静态功耗; ●带有输入滞回和可编程地(GND),提高了高速I/O信号完整性; ●可提供多种封装形式; ●采用通用的JTAG接口; ●带有双边缘触发器,因而速度更快; ●带有多种LVCMOS、HSTL和SSTL I/O,其灵活的I/O可支持多种器件接口; ●具有四级设计保密功能; ●具有灵活的时钟模式,可以直接采用外部时钟,也可以利用内部的时钟分频器(包括2、4、6、8、10、12、14、16分频)。 3 基于CPLD和DDS的数频源设计 图2所示是一个数字频率合成器的总体框图。图中,先由CPLD芯片根据DDS需要的输出频率计算出频率控制字,然后附上DDS寄存器地址输出给DDS芯片,同时输出一路信号给开关,以便分段进行后续处理。 为了实现极低噪声,首先注意晶振的选取,因为根据资料分析,输出信号的相位噪声取决于时钟信号的相位噪声,并将以20log(Fout/Fclk)的规律变化,这意味着在输出信号频率不变的情况下,10MHz时钟信号所产生的相位噪声将会比100MHz时钟信号恶化20dB。所以必须选取相噪指标极低的高频率晶振作为DDS的时钟。同样,根据20log(Fout/Fclk)的公式,在时钟不变的情况下,100MHz输出信号的相位噪声也会比10MHz输出信号恶化20dB。 由于工作频带的相对带宽很宽,因此降低输出频谱谐波电平是着重考虑的问题。如果按照原来的办法,在输出信号后加一级滤波器选择信号,那么无用的谐波分量就会混入到有用信号带宽内,从而造成谐波电平超标,频谱质量降低。因此可以考虑将输出信号频带分段,即由选通开关分配给几组滤波链,最后再合成f1~f2 4.5倍频程宽带信号;滤波器要求带外抑制特性好,带内平坦度好,插损尽可能小。选通开关控制信号可由CPLD控制电路给出。 AD9952时钟输入采用双端差模输入,由外部晶振通过差分器提供。将时钟工作模式的选择管脚接地,即直接应用参考时钟频率的工作模式。输出IOUT和IOUT是一对互补信号,这种差分形式可以减少输出的共模噪声、提高信噪比;DAC_RSET通过可调电阻接地,有利于找到能够抑制噪声的最佳的电阻值;DACBP通过一个0.01μF的电容接至模拟电源,可以改善其谐波失真和杂散电平性能;DDSRE-SET由按键开关控制,按下并抬起可形成一个宽幅脉冲来使AD9952复位;串口输入控制由DDSCLK、DDSDATA、DDSCSB、DDSIOUPDATE组成,全部由控制电路输出;它们之间的关系是:由DDSCLK提供串行时钟,并在它的作用下DDSCSB由高变低时,使DDS芯片处于使能状态,然后输出一个完整的控制数据(包括寄存器地址和频率控制字的内容),之后再将DDSIOUPDATE由低变高,使已传输到AD9952的数据产生作用并使输出频率发生跳变,从而完成了一个动作。继而完成CPLD作为控制电路要实现的主要功能。 通过对AD9952的分析可知,控制电路必须输出4组信号给DDS芯片,包括DDSDATA、DDSCSB、DDSSCLK和DDSIOUPDATE,同时还要输出两组信号给后面的频选开关。DDSDATA信号是寄存器地址和频率控制字的总和,共有40位;DDSCSB作为芯片的使能信号是单独脉冲;DDSSCLK是串行时钟,DDSIOUPDATE也是单独脉冲。因此根据上面的分析,要实现DDSDATA、DDSCSB、DDSIOUPDATE信号都是很困难的。图3是CPLD顶层的电路组成。  在CPLD内部,为了简化设计,重复性使用,常常将一部分功能做成模块的形式。图3的左上脚有一个频率转换模块?ftoftw ,它的功能是根据要输出的频率(其典型值通过内部预先设置的对应表的查询来实现,非典型值则通过公式计算来实现)来输出想要的频率控制字和附加的频率寄存器地址。该模块之所以采用查表方式是出于速度的考虑。图3左下脚的模块可将一个宽幅的按键RESET信号转化成一个时钟周期的RESET信号,并且将输出作为使能信号送到右边的两个模块;该模块内部是由一个计数器来实现的,当计到某一值时输出一个脉冲,而后进入一个无输出的开循环以满足单独的脉冲输出。右上脚的模块是一个并串转换模块(shifter_ps),它可将40位的并行信号转换成串行信号,并在串行时钟的参考下一位一位地输出给DDS芯片,从而实现对寄存器的修改。这样,给输入时钟加一个反门就可得到想要的串行时钟,而且可以很方便地使之随着输入时钟的变化而变化。右下脚的模块是一个简单的计数器(counter2),它的输出正是40个时钟周期后的DDSIOUPDATE信号,同时和前一个计数器的输出通过或门得到DDSCSB信号。 该电路是数模混合电路,为了保证相噪和杂散性能,除了在原理设计和元器件选择方面要注意外,在电路的具体布局和布线方面也要加以考虑,以防止额外干扰的产生。  CB采用4层板设计,数字电源与模拟电源要分开,时钟也要单独供电;为降低电源纹波和其它干扰,还要对每一组电源分别用电容去耦。地平面上要将数字地和模拟地分开,并应在大面积铺地处通过一点连接,各相邻地平面通过磁珠相连。时钟尽量远离其它信号,并应加地线屏蔽。 CB采用4层板设计,数字电源与模拟电源要分开,时钟也要单独供电;为降低电源纹波和其它干扰,还要对每一组电源分别用电容去耦。地平面上要将数字地和模拟地分开,并应在大面积铺地处通过一点连接,各相邻地平面通过磁珠相连。时钟尽量远离其它信号,并应加地线屏蔽。4 结束语 直接数字频率合成技术具有频率转换速度快、频率分辨率高、输出相位连续和全数字化、易于集成、易于控制等优点,是频率合成器的理想选择。采用CPLD控制能进一步发挥DDS的优势,本文针对具体的宽带低噪声频率源给出了电路方案,对如何提高频谱质量进行了一些探讨。 |

网友评论