光电电流互感器高压侧电路模块的设计

发布时间:2010-8-17 16:36

发布者:lavida

|

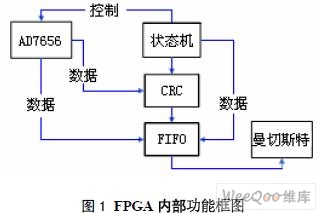

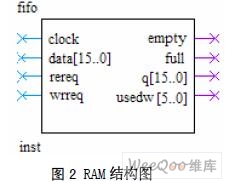

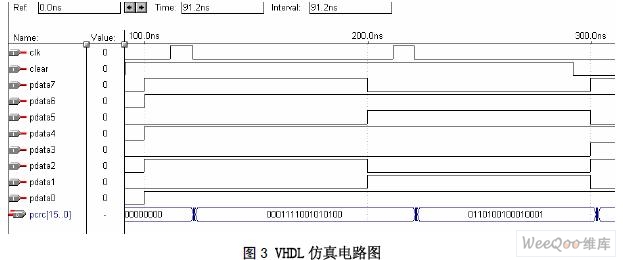

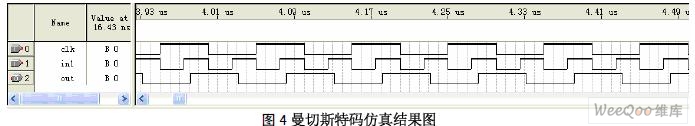

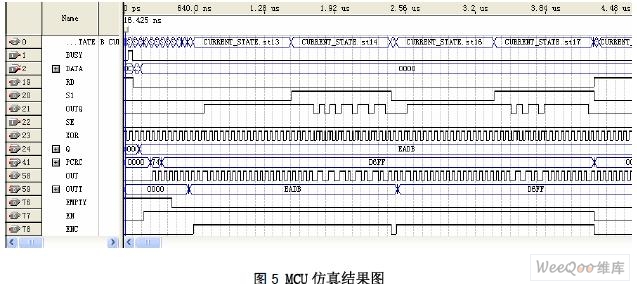

1 引言 电流互感器是电力系统中用于继电保护和电流测量的重要设备,其精确度和可靠性对电 力系统的安全、稳定和经济运行有着重要影响。随着电力系统的发展,发电和输变电容量不 断增加,电网电压不断提高,对互感器提出了许多新的和更加严格的要求,而传统的电磁式 互感器已经越来越不适应这种发展的需要。基于光学技术、电子技术、现代信号处理技术的 新一代光电电流互感器克服了传统电流互感器存在的磁饱和及铁磁谐振等一系列问题,与新 型的光电子技术相结合,具有精度高、智能化等传统电磁式互感器无法比拟的优势,应用前 景十分乐观。现在光电电流互感器的研究方向主要是有源电子式电流互感器。有源电子式电 流互感器系统主要分为三个部分:高压侧,低端侧和供电电源。 高压侧部分主要包括:传感器和高压侧电路模块。传感器现在主要是采用Rogowski 线圈 (罗氏线圈)。而高压侧电路模块主要包括:积分器,放大器,低通滤波器,模数转换器和嵌 入式微处理器。高压侧电路模块是光电电流互感器的重要组成部分,其精度、暂态响应速度 和功耗等主要性能参数对互感器有着重要的影响。 2 高压侧电路模块设计 传统的高压侧电路模块是由前期处理电路、模数转换模块、控制单元MCU、CRC 校验码单 元与曼切斯特编码单元几部分组成。作为高压侧主控单元的MCU,它主要反映了暂态响应速度和功耗两个参数,MCU 的选择可以是DSP、单片机。DSP 速度快功耗大;低功耗单片机则在速 度方面很难达到要求。随着大规模集成电路技术和计算机技术的不断发展,FPGA(Field programmable Gate Array)作为当今比较流行的嵌入式芯片有着其他芯片无法替代的优点, 成为当今应用最广泛的可编程专用器件。本文将A/D 控制模块,CRC 校验码模块和曼切斯特编 码模块的功能合并到FPGA 当中,图1 为FPGA 内部功能框图。  2.1 利用状态实现对A/D 的控制 模数转换器是整个系统中比较重要的器件,本文采用ADI 公司生产的6 通道同时采样模 数转换器AD7656。设计中,FPGA 对AD7656 的控制、读写时序由状态机来实现。本文把控制 过程分成4 个状态分别为ST0、ST1、ST2、ST3。ST0:AD 初始化,ST1:启动转换、等待转换 结束,ST2:转换结束、准备读出数据,ST3:读出数据、给计数器控制信号。 2.2 FPGA 芯片内的存储器的设计 本文在FPGA 内部设计一个16 位的FIFO 来实现数据的存储,用VHDL 语言来实现,芯片 内存储器的结构图如图2 所示。图中data 为数据输入端,wreq 为写控制信号,rdreq 为读控 制线,q 为数据输出端,clock 为时钟。Usedw 为地址信号输出线。  2.3 CRC 校验码的FPGA 设计 光纤通信过程中,在接收方检查所接收的数据是否正确,可采用多种检测方法。其中循环冗 余校验码(CRC 校验)是目前在计算机网络通信及存储器等方面应用最为广泛的一种校验编码方 法,是一种强有力的检测手段。人们将该技术用于多处数据通信系统中,收到了令人满意的效果。 为了满足电力通信的快速性、可靠性要求,本文采用CRC 并行算法来实现CRC 编码。 CRC 校验码的原理是发送端运用CRC 算法计算出待发送数据的CRC 校验码。并附加在待发送 数据的末尾,即在发送数据的同时增加CRC 码(编码过程)。发送后,接收端计算机检测数据和CRC 码之间的数学关系是否正确(译码过程),若不正确则说明数据信息在传输过程中有误码。 FPGA 已经成为当今应用最广泛的可编程专用器件,它解决了传统数字电路设计中所遇到的许多问题,能够快捷地、灵活地实现复杂数字系统的设计。本文开发软件采用Max+plusⅡ,用VHDL 语言编译实现CRC 检验算法。并给出了一组随机的16 进制数做了仿真,仿真结果如图3 所示:从 图中可以看出结果不仅可以准确地反应出CRC 校验码的数组,而且由于优化的原因波形比较平滑, 达到了预期的效果。  2.4 曼彻斯*的实现 光纤传送数据的速率很高,用异步方法恢复时序己经很不实际了,如果在接收端不能从数据 中恢复时钟信号,那么就需要另一条光纤来传时钟,这样不经济而且会造成时基摆动。所以在光 纤数据传输系统中又要选用合适的线路码,而曼彻斯*(Manchester)是当今光纤数据通信中 最常用的一种。 曼彻斯*又叫做数字双相码,是用码元中心的电平跳变来表示要传输的二进制信息,是一 种时钟自同步编码技术。曼彻斯*的编码方法是将每一个码元再分成两个相等的间隔。码元1 是在前一个为高电平而后一个间隔为低电平。码元0 则刚好相反,从低电平变到高电平。它的优 点在于可以保证在每个码元的正中间出现一次电平的转换,这除了可以防止基带信号出现连1 或 连0 的现象,又对接收端提取位同步信号是非常有利的。在实际电路设计中,本文用异或门来实 现编码的设计,但是在编码过程中由于时钟信号有上升时间和下降时间导致编码完的信号有毛刺, 本文用D 触发器来消除这些毛刺。  本文对曼切斯特编码电路作了仿真,图4 为曼切斯特编码仿真图,从图中可以看出输出信号 在输入信号的中心位置跳变,并且信号没有毛刺比较平滑,成功地完成了编码。 2.5 MCU 综合模快 本文已将图1 中的各个主要模块用VHDL 语言进行了编译和仿真,由仿真结果可以看出每一个 模块已经完成了它自己的功能。但是作为FPGA 的时序综合又是一个很复杂的工作,如何将各个模 块的功能结合在一起完成整个系统的功能、如何搭配各个模块间的时序让整个系统的时序比较合 理都是要考虑的问题。 本文对高压侧MCU 综合模快电路作了仿真,如图5 所示。给出了一个采集周期的仿真结果。  从仿真图可以看出整个MCU 模块完成了从控制A/D 采集数据;控制CRC 校验码电路进行校验码的生成;将数据存入存储器经过组合之后送入曼切斯特编码模块进行编码,最后将结果输出。 3 结论 本文把FPGA 技术应用在高压侧模数转换器的控制、CRC 校验码、曼切斯特编码等各模块的电 路设计上。主要功能包括:控制模数转换器采集信号;对采集的数字信号进行CRC 校验;把校验 码和采集数据存入存储器并按格式进行排序;把排序好的数据输入曼切施*编码电路在通过光 纤传到低压侧。采用现场可编程门矩阵FPGA 来做整个高端侧的时序控制器。同时采用FPGA 来实 现编码、解码部分的设计,这样可以把多个功能集成到一个芯片当中进一步提高效率。通过仿真 结果可以证明本文的高压侧信号处理电路设计是可行的,且能够满足电力系统中IEC60044-8 标准 所规定的高效性、时效性要求。 本文作者创新点:本文把FPGA 技术应用在高压侧模数转换器的控制、CRC 校验码、曼切斯特 编码等各模块的电路设计上,把多个功能集成到一个芯片当中,从而使系统的体积更小,精度更 高,功能更强,能够快捷地、灵活地实现系统所要求的功能。 |

网友评论