基于FPGA的HSDI接口设计

发布时间:2010-7-24 10:44

发布者:lavida

|

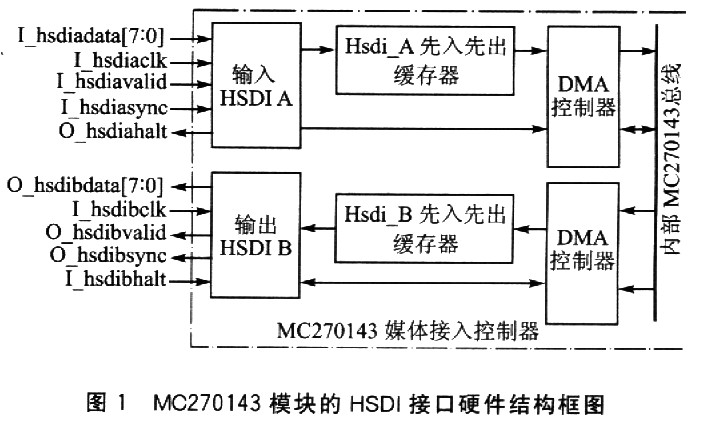

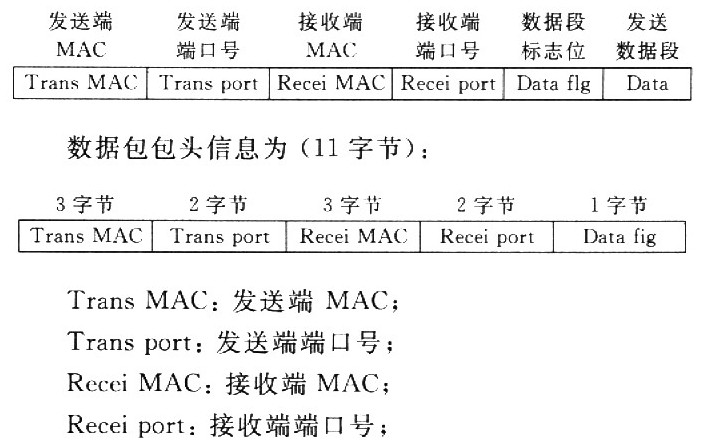

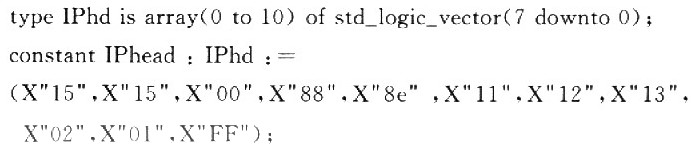

HSDI(High Speed Direct Injection)是一种可配置的高速数据接口。例如,德州仪器公司生产的集成式1394a链接层控制器与舣端口物理层控制器TSB43DA42和TSB43DB42分别包括3个高速数据端口(HSDI)。每个端口均支持数据I/O,能专门负责一个同步数据路径,所有端口都支持与各种编解码器的无缝连接,能够根据IEC61883标准实现压缩的A/V数据与数字音频的传输。还有就是Freescale公司计划开发的UWB系列产品。这些UWB网卡符合美国联邦通讯委员会(FCC)现行拟定的UWB标准,支持多种操作系统;同时,这些产品将拥有mini-PCI和SDIO模组外形结构,并且,还将具有PCI、mini-PCI、HSDI、PCI-Express、USB 2.0和IEEEl394等各种界面。下面就Freescale公司的一种UWB网卡上的HSDI接口作一介绍。 MC270143 MAC是Freescale公司UWB网卡XSllO上的一部分。它直接与基带控制器MC270123相连,当和MC270123控制器以及MC270113 RF发送器结合使用时,可以提供一种完全端到端的WPAN/WLAN芯片集解决方案,并具备低成本、低功耗和高速数据传输速率。 由于Freescale公司的UWB网卡遵循IEEE 802.15.3网络层协议标准,那么对于其上的HSDI接口,从主机来说,遵循IEEE 802.15.3协议标准的请求和响应消息是从HSDI的A口输入的,而确认和指示消息是从HSDI的B口输出给当地主机的;通过空中链路去往另一个UWB设备的数据信息,从HSDI的A口进入,另一个UWB设备从B口输出。在HSDI并行接口中,是以字节为单位来传输数据的,并且字节与字节之间没有延时。 1 HSDI接口硬件结构 图1为Freescale公司XSIlO网卡上MC270143模块的HSDI接口硬件结构框图。  ①HSDI A和HSDI B用于传输高速数据流或者命令和控制信号,它们支持传输同步或异步的数据流以及命令消息和相关的响应消息。HSDI A只能配置成输入接口,HSDI B只能配置成输出接口。HSDIA和HSDI B都是由8位并行端口和输入时钟以及相关控制信号组成的。 ②每个FIFo的容量为512×32位。 ③O_hsdiahalt信号用来阻止数据从HSDI A接口输入,O_hsdiahaltxin信号产生后MC270143最多还可以接收16字节的数据。也就是说,外部时钟必须在16个时钟周期之前产生O_hsdiahalt。 ④任何从MC270143接收输出数据的设备必须能够在产生I_hsdibhalt后再接收至少1 6字节的数据,也可配置MC270143上的HSDI B模块忽略产生I_hsdibhalt信号。 2 HSDl接口信号描述 整个XSll0模块的外部接口主要为:输入是天线部分,输出是HSDI接口。接口(相对UWB网卡而言)说明如表l所列。  HSDI接口可以配置成发送和接收定长/可变长度的数据包。定长数据包模式包括HSDI输入模式(HSDI A)和HSDI输出模式(HSDI B):所有输入到HSDI接口的数据都是在hsdiclk的上升沿采样输入;输出数据在hsdi-clk的下降沿输出。相应的时序图如图2和图3所示。  说明:在定长和可变长数据包类型下,HSDI接口信号描述是相同的;惟一的不同在于,在可变长模式下,hsdisync信号与最后一个有效字节对齐,而在定长模式下与第一个有效字节对齐。 3 基于FPGA实现HSDI接口的设计 利用FPGA硬件处理速率高的特点,通过普通数据包的发送可实现发送端HSDI接口的设计,并把数据通过HSDI接口发送到UWB网卡,再由UWB网卡发送出去,随后由另外的UWB网卡接收相应的数据。 发送端FPGA负责把数据打包并生成相应的数据有效信号和同步信号,然后通过HSDI接口发送给UWB网卡。FPGA与HSDI的接口定义如图4所示。  4 打包发送模块程序设计 由于USB网卡遵循IEEE 802.15.3网络层协议标准,考虑到发送端和接收端.做简单的应用层协议如下:  Data flg:数据段标志位,标志随后的为数据字节,以便对数据进行处理。 首先,把包头信息定义好固化在1个11字节的表中,程序为:  其中:dataflg为x“FF”标志,随后的为数据信息,同时也说明数据信息的长度。 其次,按照HSDI传输格式,可以确定的是在发送hsclivalid、hsdisync、hsdidata信号的时候要用lasdiclk的下降沿送出,以保证网卡的正确采样。(VHDL程序见本刊网站www.mesnet.com.cn——编者注) ①hsdidata数据信号的生成:将发送包的包头信息存放在一个固化的小表里(内部的自建存储器)。数据的打包发送主要由2个与时钟同步的计数器datacntl和datacnt2(hsdiclk下降沿产生)控制。datacntl为4位,控制发送11位包头信息,根据不同计数器的值决定发送包头信息位数据。发送到最后1位包头信息时。启动datacnt2计数,开始发送包数据,且发送的数据和计数器datacnt2的值是相等的,以确保接收端检测数据传输的正确性。 ②hsdivalid信号的生成:由datacnt2来控制。hsdi-valic初始化为0,在计数器datacnt2记到x“FF”时为0,其他情况下为l即可标志一个包的有效数据位。 ③hsdisync信号的生成:由datacntl来控制。hsdi-sync韧始化为0,由于采用的是定长数据包模式,所以在计数器记到x“00”时为1,标志包数据的第1位,其他情况下为0。modelsim仿真得到的时序如图5所示。QuartusⅡ仿真结果如图6所示。  5 结论 本文详细讨论了HSDI接口的硬件结构以及接口信号的时序和功能操作。结合FPGA高处理速度的特点,实现了基于FPGA的HSDI接口设计,最后结合实例成功地进行了仿真和验证,并在实际硬件平台上实现了发送和接收解析数据包。 |

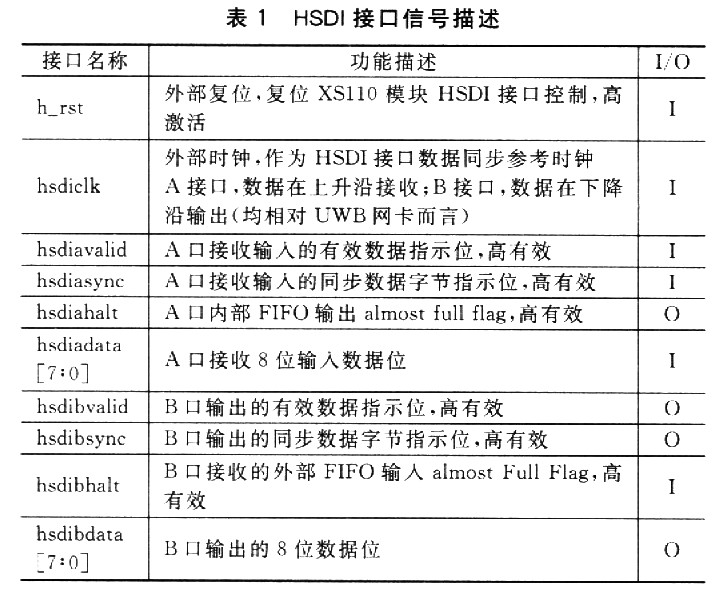

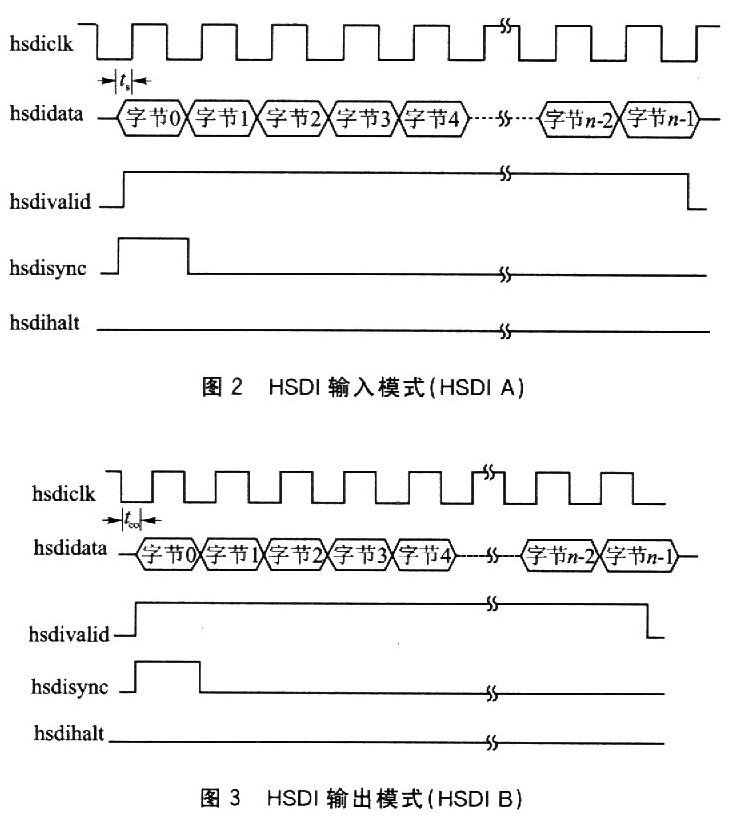

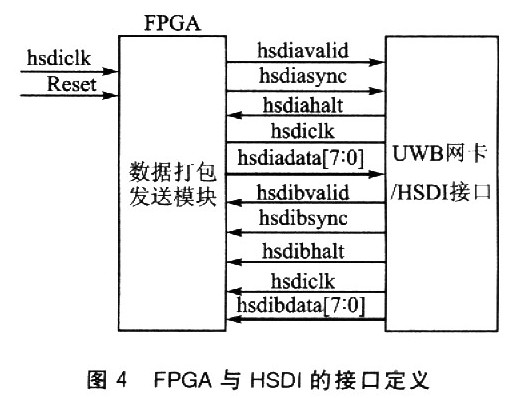

网友评论