FPGA设计开发软件ISE使用技巧之:典型实例-增量式设计演示

发布时间:2015-11-24 09:18

发布者:designapp

|

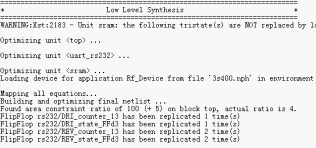

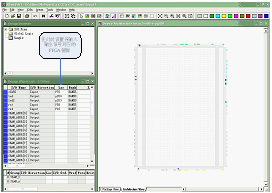

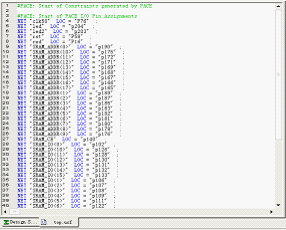

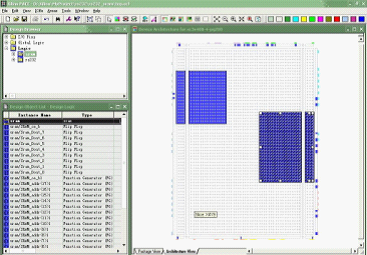

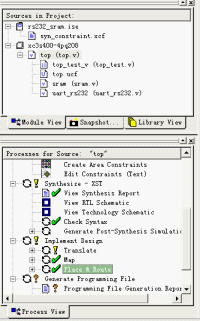

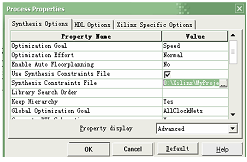

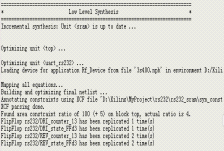

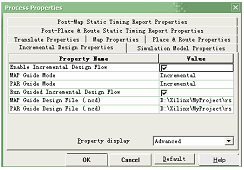

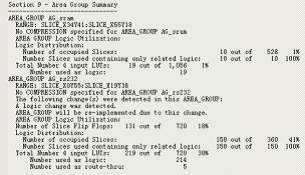

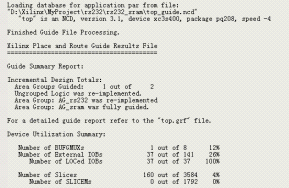

6.9 典型实例12:增量式设计(Incremental Design)演示 6.9.1 实例的内容及目标 1.实例的主要内容 6.7节对增量式设计这一方法的基本概念和流程做了全面的介绍。本节将以一个具体的实例帮助读者熟悉增量式设计的操作流程。 本实例的源代码参见随书光盘Example6.9。此程序为PC机通过串口向SRAM写入数据,再由FPGA从SRAM中读取数据通过串口将其送到PC机。 本实例的重点在于设计过程中是如何应用增量式设计的,而不是如何实现程序本身的功能。 2.实例目标 通过本训练,读者应达到下面的目标。 · 掌握增量式设计与一般设计的区别。 · 掌握增量式设计的设计流程。 6.9.2 实例详解 增量式设计的具体实现步骤如下。 (1)打开ISE工程。 设计的第一步为创建逻辑分组。 在本设计中,top.v为顶层模块。顶层模块中包含两个功能模块,分别为:uart_rs232.v和sram.v。uart_rs232.v用于完成串口数据传输,sram.v用于对于SRAM的基本读写操作。 top.v顶层模块中,仅包含这两个模块,没有其他复杂逻辑。并且每个逻辑分组均以寄存器输出,可将这3个模块看作3个逻辑分组,满足创建逻辑分组所必须遵循的原则。 (2)综合。 为了保证在后面的实现中能够准确地完成分组区域约束,这里需要对综合的属性进行设置,在“Processes for Source”中选择“Synthesize-XST”,单击鼠标右键,设置综合属性如图6.86所示。  图6.86 设置综合属性对话框 选择“Synthesis Options”/“Keep Hierarchy”,设置综合属性为保留结构层次模式。 综合完毕要查看综合报告,为了和下面流程中的增量综合结果作对比,请特别注意综合报告中如图6.87所示的部分。在没有进行增量综合时,要对每个模块都进行综合和优化。  图6.87 未设置综合约束条件时的综合报告 (3)设置管脚约束。 在“Processes for Source”中选择“Assign Package Pins”启动设置管脚约束的工具PACE,如图6.88所示,在Loc处设置各信号对应的FPGA管脚。具体设置可参见例程代码Source文件夹下的top.ucf文件。  图6.88 设置管脚约束界面 设置好管脚约束后,保存退出PACE。在“Processes for Source”中选择“Edit Constraints Text”,即在Text模式下编辑约束文件。可以看到系统自动生成的管脚约束文件内容,如图6.89所示。  图6.89 系统生成的管脚约束文件 (4)设置分组区域约束。 在“Processes for Source”中选择“Create Area Constraints”,启动设置分组区域约束工具PACE。分别选中sram和rs232,单击左上角的  图标,为每一个逻辑分组设置区域约束,如图6.90所示。  图6.90 进入分组区域约束模式 设置区域约束结果如图6.91所示。  图6.91 区域约束设置结果 如图6.91所示,图中左上角的区域对应的是SRAM逻辑分组的约束区域,右下角的区域为rs232逻辑分组的约束区域。采用如上的约束是综合两个逻辑分组内部逻辑的复杂性以及I/O位置来确定的。这里的约束并不惟一,读者可根据需要进行修改。 设置完毕后,保存设置。在“Processes for Source”中选择“Edit Constraints Text”,即在text模式下编辑约束文件,可看到在约束文件中新添了如下内容: #PACE: Start of PACE Area Constraints AREA_GROUP "AG_rs232" RANGE = SLICE_X0Y55:SLICE_X19Y38 ;//设置rs232逻辑分组区域 INST "rs232" AREA_GROUP = "AG_rs232" ; AREA_GROUP "AG_sram" RANGE = SLICE_X34Y41:SLICE_X55Y18 ;//设置SRAM逻辑分组区域 INST "sram" AREA_GROUP = "AG_sram" ; (5)在普通模式下对工程进行映射和布局布线。 在普通模式下(采用ISE下默认的实现属性)对工程进行映射和布局布线是为了得到初始的指引文件,用于在后面的增量设计中指引映射和布局布线。 首先在“Processes for Source”中选择“Implement Design”/“Map”,对工程进行映射。实现后系统会生成:top_map.ncd和top_map.ngm文件,需要用这些文件来指引后面的增量设计的映射。为了避免系统将此文件覆盖,将其改名为:top_map_guide.ncd和top_map_guide.ngm文件。 接着在“Processes for Source”中选择“Implement Design”/“Place&Route”,对工程进行布局布线,会得到top.ncd文件。也将其改名为:top_guide.ncd,将其作为后面增量设计时布局布线的指引文件。  注意如果在此步骤中无法顺利地完成映射和布局布线等步骤,很可能是区域分组约束做得不合适。需要重新做区域分组约束,直到能够顺利完成映射和布局布线为止。映射完成后要查看映射报告看各逻辑分组的资源利用率。如果不合适,需要修改区域约束后重新进行映射和布局布线。映射报告需要注意的内容如图6.96所示。 完成映射和布局布线后的结果如图6.92所示: (6)对工程进行增量综合。 如果在设计调试中发现了某个Logic Group需要修改,对其做微小的改动后,要对工程进行增量综合。例如可以修改uart_rs232.v的代码,然后进行增量综合。 本实例中的增量综合采用ISE自带的工具XST。采用XST进行增量综合时,必须为其添加约束文件(扩展名为xcf)。添加的约束文件可先在记事本中编辑,然后保存为扩展名为xcf的文件。在本实例中综合约束文件为syn_constraint.xcf文件,其内容如下: MODEL "top" incremental_synthesis=yes; //使用增量综合 MODEL "sram" incremental_synthesis=yes; //使用增量综合 MODEL "uart_rs232" incremental_synthesis=yes; //使用增量综合 MODEL "top" resynthesize=yes; //启动增量综合 MODEL "sram" resynthesize=no; //不启动增量综合 MODEL "uart_rs232" resynthesize=yes; //启动增量综合 前3句设置各逻辑分组均采用增量综合,后3句通知哪个逻辑分组内容发生改变,需要重新综合,哪个逻辑分组内容未发生改变,无需重新综合。编辑完毕,将该文件添加到当前的工程当中,如图6.92所示,上面syn_constranit.xcf文件即为添加结果。 添加完毕后,要使这一约束文件有效,还要对综合属性进行设置,如图6.93所示。   图6.92 对工程进行映射和布局布线结果 图6.93 增量综合属性设置对话框 选择“Synthesis Options”/“Synthesis Constraints File”,根据约束文件所在位置,设置约束文件的路径。设置完毕后,对工程进行增量综合。综合完毕后,查看综合报告,注意如下内容。 将图6.94与图6.87进行比较,可以看出综合中仅对top和rart_rs232两个逻辑分组重新进行了综合和优化。SRAM逻辑分组保持不变(Unit is up to date),表明增量综合实现了。   图6.94 增量综合的综合报告图 6.95 增量实现属性设置对话框 (7)对工程进行增量实现(Implement)。 完成增量综合后,就可以利用前面得到的初始的指引文件:top_map_guide.ncd和top_guide.ncd文件来指引增量实现。 首先对工程实现的属性进行设置,具体设置如下。 单击右键,选择进程浏览器中的“Implement Design”的“Property”选项,弹出工程实现属性对话框,如图6.95所示。在增量设计属性页中做如下设置。 · 为“Enable Incremental Design Flow”使能增量实现。 · 为“Run Guided Incremental Design Flow”设置用指引文件来引导增量实现。 · 为“MAP Guide Design File(.ncd)”设置指引映射的指引文件top_map_guide.ncd路径。 · 为“PAR Guide Design File(.ncd)”设置指引布局布线的指引文件top_guide.ncd路径。 按上述方式设置完毕后,对工程进行映射和布局布线后,查看映射和布局布线报告,对于映射报告注意以下内容。 如图6.96所示,在映射报告中会对每个逻辑分组在各自约束的区域内的资源利用情况作一个总结报告。可以看到各分组所用的LUT和Slices占其约束区域总量的百分比。如果出现某一逻辑分组的使用率达90%以上,而有些逻辑分组还不到1%,则需要重新进行区域约束。  图6.96 映射报告(Map Report) 区域约束最好在生成初始指引文件时就确认。在普通模式下完成映射后查看映射报告,查看每个逻辑分组的资源利用率。如是不合适,则更改区域约束,重新进行映射。 对于布局布线报告注意以下内容。 如图6.97所示,布局布线时读取了top_guide.ncd作为指引文件,仅有rs_232逻辑分组重新进行了布局布线(AG_rs232 was re-implemented)。SRAM逻辑分组完全继承了前面已有的结果(AG_sram was fully guided),说明增量实现完成了。  图6.97 布局布线报告(Place&Route Report) 完成了布局布线后就可以下载调试了。如果仍需要改动,重复步骤(6)和步骤(7),直到设计符合要求为止。 6.9.3 小结 本节以一个具体的实例介绍了ISE下增量设计流程。希望读者能够按照上述步骤进一步熟悉ISE的增量设计流程,对增量设计有个比较全面的认识,最终将这种设计方法应用到自己的设计当中。 |

网友评论