Ľý”ŕIQĹ‚Ķų∆ų£¨ĺŖ”–÷–∆ĶļÕĽýīÝŅ…Īš‘Ų“ś“‘ľįŅ…Īŗ≥ŐĽýīݬň≤®Ļ¶ń‹Ķń÷–∆Ķ÷ŃĽýīÝĹ” ’Ľķ

∑Ę≤ľ Īľš£ļ2014-12-17 09:35

∑Ę≤ľ’Ŗ£ļdesignapp

|

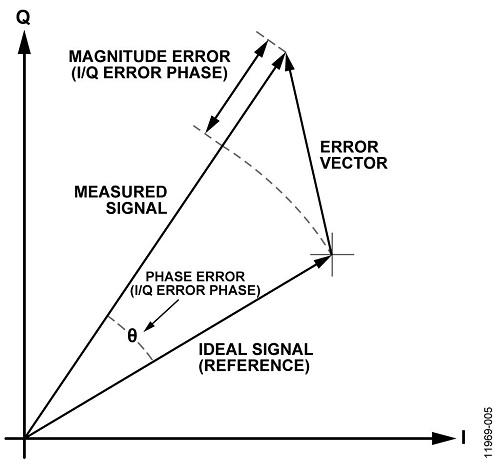

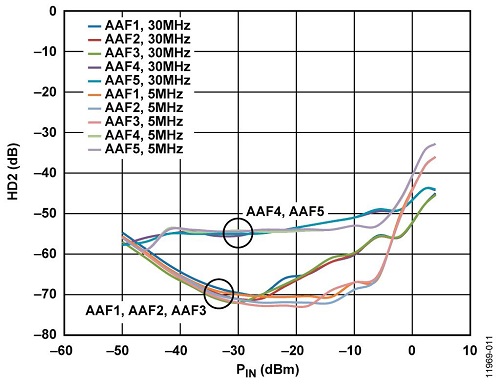

ѨŔ/≤őŅľ∆ųľĢ ADRF6510 30MHzňęÕ®ĶņŅ…Īŗ≥Ő¬ň≤®∆ųļÕŅ…Īš‘Ų“ś∑Ňīů∆ų ADRF6801 750MHz÷Ń1150MHz’żĹĽĹ‚Ķų∆ų£¨ľĮ≥…–° żN∑÷∆ĶPLLļÕVCO AD9248 14őĽ°Ę65MSPSňęÕ®ĶņADC ∆ņĻņļÕ…Ťľ∆÷ß≥÷ ĶÁ¬∑∆ņĻņįŚ ADRF6510∆ņĻņįŚ(ADRF6510-EVALZ) ADRF6801∆ņĻņįŚ(ADRF6801-EVALZ) AD9248∆ņĻņįŚ(AD9248BCP-65EBZ) AD8130∆ņĻņįŚ(AD8130-EBZ)£¨–Ť“™ŃĹłŲ żĺ›≤…ľĮįŚ(HSC-ADC-EVALB-DCZ) …Ťľ∆ļÕľĮ≥…őńľĢ ‘≠ņŪÕľ°Ę≤ľĺ÷őńľĢ°ĘőÔŃŌ«ŚĶ• ĶÁ¬∑Ļ¶ń‹”Ž”Ň ∆ ĪĺĶÁ¬∑ «ŃťĽÓĶń∆Ķ¬ Ĺ›Īš÷ĪĹ”Īš∆Ķ÷–∆Ķ÷ŃĽýīÝĹ” ’Ľķ£¨∆š5dBĻŐ∂®◊™ĽĽ‘Ų“śŅ…ĹĶĶÕľ∂Ń™‘Ž…ýŌĶ ż°£Ņ…ĪšĽýīÝ‘Ų“ś”√ņīĶųĹŕ–ŇļŇĶÁ∆Ĺ°£ĽýīÝADC«ż∂Į∆ųĽĻįŁņ®Ņ…Īŗ≥ŐĶÕÕ®¬ň≤®∆ų£¨Ņ…ŌŻ≥żÕ®ĶņÕ‚◊Ť»ŻļÕ‘Ž…ý°£ īň¬ň≤®∆ųĶńīÝŅŪŅ…ňś◊Ň š»Ž–ŇļŇīÝŅŪĪšĽĮ∂Ý∂ĮŐ¨ĶōĶųĹŕ°£’‚—ýŅ…“‘»∑Ī£”…ĪĺĶÁ¬∑«ż∂ĮĶńADCĶńŅ…”√∂ĮŐ¨∑∂őßĶ√ĶĹ≥š∑÷ Ļ”√°£ ĪĺĶÁ¬∑Ķńļň–ń≤Ņ∑÷ «“ĽłŲľĮ≥… ĹIQĹ‚Ķų∆ų£¨”…–° żN∑÷∆ĶPLLļÕVCO◊ť≥…°£”…”ŕĹŲ”–“ĽłŲ£®Ņ…Īš£©≤őŅľ∆Ķ¬ £¨PLL/VCOŅ…ŐŠĻ©∑∂őßő™750MHz÷Ń1150MHzĶńĪĺ’Ů(LO)–ŇļŇ°£ĺę»∑Ķń’żĹĽ∆Ĺļ‚ļÕĶÕ š≥Ų÷ĪŃų ßĶų»∑Ī£Ńň∂‘őů≤Ó łŃŅ∑ý∂»(EVM)Ķń”įŌžľę–°°£ ĪĺĶÁ¬∑ńŕňý”–‘™ľĢľšĶńĹ”Ņŕĺý≤…”√»ę≤Ó∑÷ Ĺ°£»ÁĻŻ≤ĽÕ¨ľ∂ľš–Ť“™÷ĪŃųŮÓļŌ£¨ŌŗŃŕľ∂Ķń∆ę÷√ĶÁ∆ĹĪňīňľś»›°£  Õľ1.÷ĪĹ”Īš∆ĶĹ” ’Ľķ‘≠ņŪ ĺ“‚Õľ£®őīŌ‘ ĺňý”–ѨŔļÕ»•ŮÓ£© ĶÁ¬∑√Ť Ų Ĺ” ’Ľķľ‹ĻĻ ĪĺĶÁ¬∑Ī ľ«÷–√Ť ŲŃňĹ” ’ĽķĶń÷ĪĹ”Īš∆Ķ£®“≤≥∆ő™Ń„≤ÓĽÚŃ„÷–∆Ķ£©ľ‹ĻĻ°£”ŽŅ…“‘÷ī––∂ŗīő∆Ķ¬ ◊™ĽĽĶń≥¨Õ‚≤Ó ĹĹ” ’ĽķŌŗĪ»£¨÷ĪĹ”Īš∆ĶőřŌŖĶÁ÷Ľń‹÷ī––“Ľīő∆Ķ¬ ◊™ĽĽ°£“Ľīő∆Ķ¬ ◊™ĽĽĶń”Ň ∆»ÁŌ¬£ļ °Ů ĹĶĶÕĹ” ’Ľķłī‘”–‘£¨ľű…Ŕňý–Ťľ∂ ż£ĽŐŠłŖ–‘ń‹ļÕĹĶĶÕĻ¶ļń °Ů Ī‹√‚ĺĶŌŮ“÷÷∆ő Ő‚ļÕ≤Ľ–Ť“™ĶńĽž∆Ķ≤ķőÔ£Ľ÷Ľ–Ť“™ĽýīÝ…ŌĶń“ĽłŲLPF °Ů łŖŃť√Ű∂»£®ŌŗŃŕÕ®Ķņ“÷÷∆Ī»[ACRR]£© Õľ1Ō‘ ĺŃňł√ŌĶÕ≥ĶńĽýĪĺ‘≠ņŪ ĺ“‚Õľ£¨įŁņ®”…–° żN∑÷∆ĶPLLļÕVCO◊ť≥…ĶńľĮ≥… Ĺ’żĹĽĹ‚Ķų∆ų£¨ļůĹ”ĺŖ”–Ņ…ĪšĽýīÝ‘Ų“śĶńŅ…Īŗ≥ŐĶÕÕ®¬ň≤®∆ų°£–ŇļŇŃīĶń◊Óļů“Ľ≤Ņ∑÷ «“ĽłŲŅĻĽžĶĢ¬ň≤®∆ųļÕ“ĽłŲňęÕ®ĶņADC°£ ņŪŌŽ«ťŅŲŌ¬£¨Ķŕ“Ľľ∂Ķń š»ŽļÕ◊Óļůľ∂Ķń š≥Ų”¶…Ť÷√ŌĶÕ≥Ķń∂ĮŐ¨∑∂őߣ®–Ň‘ŽĪ»£©°£ Ķľ …Ō£¨«ťŅŲŅ…ń‹≤Ę∑«»Áīň°£ IQĹ‚Ķų∆ų°Ę–° żN∑÷∆ĶPLLļÕVCO š»Ž–ŇļŇ ©ľ”÷ŃADRF6801’żĹĽĹ‚Ķų∆ų£¨ł√Ĺ‚Ķų∆ųĹę∆Ķ¬ ◊™ĽĽő™Ń„÷–∆Ķ°£ADRF6801∆¨ńŕľĮ≥…∆Ķ¬ ļŌ≥…∆ų£¨ŐŠĻ©ňý–ŤĶńLO–ŇļŇ°£ł√∆Ķ¬ ļŌ≥…∆ų”…–° żN∑÷∆ĶPLLļÕVCO◊ť≥…£¨‘ŕĪÍ◊ľĪ’Ľ∑ń£ ĹŌ¬Ņ…ŐŠĻ©750MHz÷Ń1150MHzĶńLO∆Ķ¬ ∑∂őß°£ ADRF6801 Ļ”√ŃĹłŲňę∆Ĺļ‚Ľž∆Ķ∆ų£¨“ĽłŲ”√”ŕIÕ®Ķņ£¨“ĽłŲ”√”ŕQÕ®Ķņ°£ŐŠĻ©łÝĽž∆Ķ∆ųĶńLO Ļ”√2∑÷∆Ķ’żĹĽ∑÷Ōŗ∆ų…ķ≥…°£’‚ő™IļÕQÕ®Ķņ∑÷ĪūŐŠĻ©Ńň0°„ļÕ90°„–ŇļŇ°£ADRF6801‘ŕRF š»Ž÷ŃĽýīÝIļÕQ š≥Ų÷ģľšŐŠĻ©‘ľ5dBĶń◊™ĽĽ‘Ų“ś°£ ĶÕÕ®¬ň≤®∆ų°ĘĽýīÝŅ…Īš‘Ų“ś∑Ňīů∆ų(VGA)ļÕADC«ż∂Į∆ų ĶÕÕ®¬ň≤®∆ų°ĘĽýīÝ‘Ų“śļÕADC«ż∂ĮĻ¶ń‹»ę≤Ņ Ļ”√ADRF6510ņī ĶŌ÷°£ ©ľ””ŕADRF6510Ķń–ŇļŇŌ÷‘ŕĺŖ”–∂ņŃĘĶńIļÕQ¬∑ĺ∂£¨–ŇļŇ ◊Ō»Õ®Ļż«į÷√∑Ňīů∆ų∑Ňīů£¨»ĽļůĹÝ––ĶÕÕ®¬ň≤®£¨“‘“÷÷∆»őļő≤Ľ–Ť“™ĶńīÝÕ‚–ŇļŇļÕ/ĽÚ‘Ž…ý£¨◊ÓļůÕ®ĻżVGA∑Ňīů°£ ADRF6510Ķń√ŅłŲÕ®ĶņŅ…∑÷ő™»żłŲľ∂£ļ °Ů «į÷√∑Ňīů∆ų °Ů Ņ…Īŗ≥ŐĶÕÕ®¬ň≤®∆ų °Ů VGAļÕ š≥Ų«ż∂Į∆ų Õ®ĻżGNSW“żĹŇ£¨«į÷√∑Ňīů∆ųĺŖ”–6dBĽÚ12dBĶń”√ĽßŅ…—°‘Ų“ś°£ĶÕÕ®¬ň≤®∆ųŅ…Õ®ĻżSPI∂ňŅŕ…Ť÷√ő™1MHz÷Ń30MHzĶń◊™’Ř∆Ķ¬ £¨≤ĹĹÝő™1MHz°£VGAĺŖ”–50dB‘Ų“ś∑∂őߣ¨‘Ų“ś–Ī¬ ő™30mV/dB°£VGA‘Ų“śÕ®ĻżGAIN“żĹŇŅō÷∆£¨GNSW“żĹŇĪĽņ≠ĶÕ Ī∑∂őßŅ…ő™-5dB÷Ń+45dB£¨GNSW“żĹŇĪĽņ≠łŖ Ī∑∂őßŅ…ő™+1dB÷Ń+51dB°£ š≥Ų«ż∂Į∆ųń‹ĻĽĹę1.5Vp-p≤Ó∑÷ĶÁ—Ļ«ż∂Į÷Ń1k¶łłļ‘ōńŕ£¨Õ¨ ĪĪ£≥÷łŖ”ŕ60dBcĶńHD2ļÕHD3°£ Ņ… ©ľ””ŕĶÕÕ®¬ň≤®∆ųÕ¨ Ī»‘‘ŕADRF6510ńŕĪ£≥÷Ņ…Ĺ” ‹ĶńHDĶÁ∆ĹĶń◊ÓīůѨ–Ý≤®(CW)–ŇļŇő™2Vp-p£¨īň Ī‘Ų“ś◊Ó–°£®GNSW=0V£¨GAIN=0V£©°£ ADRF6510∑Ę≥ŲĶńIQ–ŇļŇŅ… ©ľ””ŕń£ ż◊™ĽĽ∆ų(ADC)£¨ņż»ÁAD9248£¨ĶęĪō–Ž ◊Ō»‘ŕŃĹľ∂÷ģľš≤Ņ ūőř‘īĶÕÕ®¬ň≤®°£ ŅĻĽžĶĢ¬ň≤®∆ų Õ®ĻżŅĻĽžĶĢ¬ň≤®∆ųĶńIļÕQ–ŇļŇ”–÷ķ”ŕ£ļ °Ů ľű…ŔīÝÕ‚‘Ž…ý °Ů ľű…ŔADRF6510Ķń š≥Ų‘Ž…ý£®ŐōĪū «‘ŕĹŌłŖĶń‘Ų“śŌ¬£© °Ů ľű…Ŕņī◊‘ADCĶńĶÁļ…∑ī≥Ś °Ů ”–÷ķ”ŕľű…ŔīÝÕ‚◊Ť»Ż£®ňš»ĽňŁ√«”¶ĶĪ”…ADRF6510Ķń¬ň≤®Ļ¶ń‹ľ”“‘ŌŻľű£© ŅĻĽžĶĢ¬ň≤®∆ų «“ĽłŲĶÕÕ®¬ň≤®∆ų£¨…Ťľ∆ő™ĺŖ”–‘ľ30MHz÷Ń120MHzĶń◊™’Ř∆Ķ¬ ∑∂őß°£»ÁĻŻ“—÷™–ŇļŇĶń∆Ķ∆◊≥…∑÷ĶÕ”ŕ30MHz£¨ń«√īŅ…“‘—°‘ŮĹŌĶÕĶń◊™’Ř∆Ķ¬ °£ ◊‹Ļ≤‘ŕŌĶÕ≥÷–≤‚ ‘Ńň5łŲŅĻĽžĶĢ¬ň≤®∆ų°£«į3łŲ≤‚ ‘ĶńŅĻĽžĶĢ¬ň≤®∆ųő™≤Ó∑÷RC–Õ£¨»ÁÕľ2ňý ĺ°£¬ň≤®∆ų1ĶńR=33¶ł£¨C=18pF°£’‚ ĻĶ√ĶÕÕ®◊™’Ř∆Ķ¬ ő™īů‘ľ134MHz°£  Õľ2.ŅĻĽžĶĢ¬ň≤®∆ų£®¬ň≤®∆ų1°Ę2ļÕ3£© ¬ň≤®∆ų2ĶńR=33¶ł£¨C=39pF£¨“ÚīňĶÕÕ®◊™’Ř∆Ķ¬ ő™62MHz°£◊Óļů£¨¬ň≤®∆ų3ĶńR=33¶ł£¨C=68pF£¨“Úīň◊™’Ř∆Ķ¬ ő™35.5MHz°£Õľ3÷–Ķń¬ň≤®∆ų4 «“ĽŅÓLC¬ň≤®∆ų£¨◊™’Ř∆Ķ¬ ő™33MHz£ĽÕľ4÷–Ķń¬ň≤®∆ų5 «“ĽŅÓRLC¬ň≤®∆ų£¨◊™’Ř∆Ķ¬ “≤ «33MHz°£  Õľ3.ŅĻĽžĶĢ¬ň≤®∆ų4  Õľ4.ŅĻĽžĶĢ¬ň≤®∆ų5 ADC ņī◊‘ŅĻĽžĶĢ¬ň≤®∆ųĶń–ŇļŇ ©ľ””ŕADC°£AD9248 «“ĽŅÓňęÕ®Ķņ°Ę14őĽ°Ę65MSPS 3V ADC£¨ľĮ≥…łŖ–‘ń‹≤…—ý-Ī£≥÷∑Ňīů∆ųļÕĽý◊ľĶÁ—Ļ‘ī°£ ≤‚ŃŅĹŠĻŻ£ļADRF6510ļÕADRF6510/ADRF6801◊ťļŌĶńEVM 4QAM°Ę5MSPSĶų÷∆–ŇļŇ ©ľ””ŕADRF6801’żĹĽĹ‚Ķų∆ųĶń š»Ž∂ň£¨≤Ę≤‚ŃŅőů≤Ó łŃŅ∑ý∂»(EVM)°£ Ļ”√ŃĹŅťAD8130-EBZ∆ņĻņįŚĹęADRF6801ļÕADRF6510Ķń≤Ó∑÷ š≥Ų–ŇļŇ◊™ĽĽő™Ķ•∂ň–ŇļŇ°£”–Ļō≤‚ ‘…Ť÷√ĶńłŁ∂ŗ–ŇŌĘ£¨«Ž≤őľŻ°įĶÁ¬∑∆ņĻņļÕ≤‚ ‘°Ī≤Ņ∑÷°£ EVMļ‚ŃŅ ż◊÷∑Ę…šĽķĽÚĹ” ’ĽķĶń–‘ń‹÷ ŃŅ£¨∑ī”≥∑ý∂»ļÕŌŗőĽőů≤ÓňýĶľ÷¬Ķń Ķľ –«◊ýĶ„”ŽņŪŌŽőĽ÷√Ķń∆ę≤Ó£¨»ÁÕľ5ňý ĺ°£  Õľ5.EVMÕľ Õľ6Ō‘ ĺEVM”ŽADRF6801 š»ŽĻ¶¬ ĶńĻōŌĶ£¨ĹŲ Ļ”√ADRF6801ļÕADRF6801£¨ļůĹ”ADRF6510°£∂‘”ŕADRF6801ļÕADRF6510«ķŌŖ£¨…®√Ťő™Ī£≥÷1.5Vp-p š≥ŲĶÁ—Ļ◊ųő™ADRF6801 š»ŽĻ¶¬ ňý–ŤĶńADRF6510‘Ų“śĪšĽĮ°£ ©ľ””ŕADRF6510Ķń«į÷√∑Ňīů∆ų‘Ų“ś…Ťő™6dB°£  Õľ6.EVM”ŽADRF6801ļÕADRF6801/ADRF6510◊ťļŌ š»ŽĻ¶¬ ĶńĻōŌĶ Ķ•∂ņ≤‚ ‘ADRF6801 Ī£¨–Ť◊Ę“‚£¨∂‘”ŕłŖ š»Ž–ŇļŇĶÁ∆Ĺ£¨EVM‘ŕīÔĶĹīů‘ľ+5dBm š»ŽĻ¶¬ ÷ģ«į∂ľ≤ĽĽŠŌ¬ĹĶ°£ĶęĶĪADRF6801«ż∂ĮADRF6510 Ī£¨EVMĹę‘ŕ‘ľ0dBm š»ŽĻ¶¬ ĪŅ™ ľŌ¬ĹĶ°£’‚ «“Úő™ĶĪ«į÷√∑Ňīů∆ų‘Ų“ś…Ťő™6dB«“ń£ń‚‘Ų“śő™◊Ó–°÷Ķ Ī£¨ADRF6510…ŌĶńĶÕÕ®¬ň≤®∆ų÷Ľń‹ī¶ņŪ2Vp-p£¨ľīADRF6510 š»Ž“żĹŇő™1Vp-p°£≥¨≥Ųīň–ŇļŇĶÁ∆ĹĽŠĶľ÷¬ ß’ś£¨ ĻEVMŌ¬ĹĶ°£ ∂‘”ŕĶÕ š»Ž–ŇļŇĶÁ∆Ĺ∂Ý—‘£¨SNRĪšĶ√łŁĶÕ£¨≤Ę«“EVMĶń≤‚ŃŅĹŠĻŻŅ™ ľŌ¬ĹĶ°£Ķ•∂ņ≤‚ ‘ADRF6801 Ī£¨EVMĹę‘ŕīů‘ľ-25dBm ĪŅ™ ľŌ¬ĹĶ°£Ķę «£¨ĶĪADRF6801«ż∂ĮADRF6510 Ī£¨EVM÷ĪĶĹ-40dBm≤ŇŅ™ ľŌ¬ĹĶ°£‘ŕĹŌĶÕĶń–ŇļŇňģ∆ĹŌ¬≤‚ŃŅŃĹłŲ∆ųľĢ Ī£¨EVMĽŠ”–ňýŌ¬ĹĶ£¨’‚÷ų“™ «”…ADRF6510≤ķ…ķĶń‘Ž…ýĶľ÷¬Ķń°£Ķę «£¨‘°ŇŤÕľĶń‘ŽĶ◊łŁő™∆ĹŐĻ«““Ľ÷¬£¨≤Ę«“”…”ŕĽýīÝŅ…Īš‘Ų“ś£¨∑÷ĪśĹŌ–°–ŇļŇĶńń‹Ń¶Ī»ADRF6801«ż∂ĮADRF6510 Ī“™«Ņļ‹∂ŗ°£ ”–ĻōADRF6510ļÕADRF6801łŁŌÍŌłĶńEVM≤‚ŃŅŅ…≤őŅľłų◊‘Ķń żĺ› ÷≤Š°£ ≤‚ŃŅĹŠĻŻ£ļįŁļ¨ADCĶńÕÍ’Ż–ŇļŇŃī Õľ7÷ŃÕľ16÷–Ķń–ŇļŇŃīįŁņ®ADRF6801°ĘADRF6510ļÕAD9248°£»ę≤Ņ»żłŲ∆ųľĢŌŗĽ•÷ģľšĺýő™÷ĪŃųŮÓļŌ°£ADRF6801ļÕADRF6510÷ģľšĶńĻ≤ń£ĶÁ—Ļő™2.6V°£ADRF6510ļÕAD9248÷ģľšĶńĻ≤ń£ĶÁ—Ļő™2.0V°£ADC¬ķŃŅ≥ŐĶÁ—Ļő™2V°£∂‘ADRF6801Ķń š»ŽĻ¶¬ ĹÝ––…®√Ť£¨Õ¨ ĪłńĪšADRF6510Ķń‘Ų“ś£¨“‘Ī„ĹęADC š»Ž…Ťő™-3dBFSĶń ĶĪ–ŇļŇĶÁ∆Ĺ°£ Ļ”√ADCļÕVisual Analog»ŪľĢ≤‚ŃŅSNR°ĘSFDR°ĘTHD°ĘHD2ļÕHD3°£ Ļ”√Agilent 8665BĶÕŌŗőĽ‘Ž…ý–ŇļŇ∑Ę…ķ∆ų£¨Ĺę≤…—ýňŔ¬ …Ťő™65MSPS°£ Ļ”√ŃĹ÷÷≤ĽÕ¨ĶńADRF6510¬ň≤®∆ųīÝŅŪ£ļ5MHzļÕ30MHz°£īňÕ‚£¨ĹęADRF6510Ķń«į÷√∑Ňīů∆ų‘Ų“śī”6dBłńő™12dB°£ š»ŽADRF6801ĶńRF–ŇļŇő™895MHz£¨LO–ŇļŇ…Ťő™900MHz£¨ī”∂Ý≤ķ…ķ5MHz÷–∆Ķ–ŇļŇ“Ű°£ Ļ”√100MHz◊ųő™≤őŅľ°£∂‘≤őŅľ–ŇļŇĹÝ––4∑÷∆Ķ£¨≤ķ…ķ25MHz PFD∆Ķ¬ °£≤…”√–ÕļŇő™119-3651-00ĶńWenzelĺß’Ů≤ķ…ķ100MHz–ŇļŇ°£ ĪĺĶÁ¬∑Ī ľ« ’ľĮĶń żĺ›Ō‘ ĺAD9248 ADCĶńSNR(71.6dB)ļÕSFDR(80.5dBc)–‘ń‹≥¨ĻżŃňADRF6801ļÕADRF6510◊ťļŌĶń–‘ń‹°£ŌĶÕ≥Ķń◊‹SNRļÕSFDR÷ų“™ ‹Ōř”ŕADRF6510Ķń š≥Ų‘Ž…ý£¨‘Ų“śő™20dB Ī∆š∂Ó∂®÷Ķő™-130dBV/°ŐHz£¨¬ň≤®∆ųīÝŅŪő™30MHz£¨‘ŕ÷–ľš∆ĶīÝ≤‚ŃŅ°££®”–ĻōADRF6510‘Ž…ý”Ž‘Ų“śļÕīÝŅŪ…Ť÷√ĶńłŁ∂ŗ–ŇŌĘ£¨«Ž≤őŅľADRF6510 żĺ› ÷≤Š£©°£ ADRF6510¬ň≤®∆ų‘ŕłŖ š»ŽĻ¶¬ ňģ∆Ĺ ĪĪŪŌ÷≥Ų—ĻňűŐō–‘£®Īĺņż÷–ő™ĶÕ‘Ų“ś£©£¨‘Ųľ”Ńň–≥≤® ß’ś°£ĽýĪĺ…Ō£¨‘ŕĶÕ š»ŽĻ¶¬ ňģ∆ĹŌ¬£¨ADC≤‚ŃŅADRF6510Ķń š≥Ų‘ŽĶ◊£¨≤Ę«“HD2ļÕHD3–ŇļŇ“ŰĶÕ”ŕīň‘ŽĶ◊°£”…”ŕ‘ŕĹŌĶÕĶń š»ŽĻ¶¬ Ō¬ĺŖ”–ĹŌłŖĶń‘Ų“ś£¨ADRF6510Ķń š≥Ų‘ŽĶ◊”–ňý‘Ųľ”°£ Õľ7ļÕÕľ8Ō‘ ĺ’ŻłŲ–ŇļŇŃī£®įŁņ®ADC£©ĶńSNR°£‘ŕĶÕĻ¶¬ ňģ∆ĹŌ¬£¨SNRľłļű÷ūdBŌ¬ĹĶ°£ADRF6510Ķń‘Ų“śő™◊Óīů÷Ķ£¨≤Ę«“őř∑®ľŐ–Ý‘ŕĹŌĶÕĶń š»ŽĻ¶¬ ňģ∆ĹŌ¬ŐŠĻ©-3dBFS°£–ŇļŇ∑ý∂»Ō¬ĹĶ£¨∂Ý‘Ž…ýŌŗ∂‘Ī£≥÷ļ„∂®£Ľ“Úīň£¨SNRŌ¬ĹĶ°£ĶĪ–ŇļŇļÕ‘Ų“ś◊„“‘īÔĶĹ-3dBFS Ī£¨SNRīÔĶĹļ„∂®ňģ∆Ĺ°£ Ļ”√ŅĻĽžĶĢ¬ň≤®∆ų3Ņ…ĽŮĶ√◊Óľ—SNR£¨ňš»Ľ∑÷…Ę‘ŕňý”–¬ň≤®∆ų÷ģľšĶń÷Ľ”–īů‘ľ1dB£¨ĶęŅĻĽžĶĢ¬ň≤®∆ų1≥żÕ‚£¨ŌŗĪ»∆š”ŗ¬ň≤®∆ų£¨ł√¬ň≤®∆ų ĻSNRĪš≤Ó°£ ĶĪADRF6510¬ň≤®∆ų…Ťő™30MHz Ī£¨‘ŕ◊ÓłŖĶń š»ŽĻ¶¬ Ō¬SNRīů∑ýŌ¬ĹĶ£¨»ÁÕľ8ňý ĺ°£’‚ «“Úő™ADRF6510¬ň≤®∆ųĶń—ĻňűĶľ÷¬HD2ļÕHD3ÕĽ»ĽŌ¬ĹĶ£¨∂Ý’ŻłŲ‘ŽĶ◊ľĪĺÁ‘Ųľ”°£  Õľ7.5łŲŅĻĽžĶĢ¬ň≤®∆ųĶńŌĶÕ≥SNR£®ADRF6510Ķń¬ň≤®∆ų◊™’Ř∆Ķ¬ ő™30MHzļÕ5MHz£¨5MHz÷–∆Ķ–ŇļŇ“Ű£¨GNSW=ĶÕĶÁ∆Ĺ£¨«į∂ň‘Ų“ś=6dB£©  Õľ8.5łŲŅĻĽžĶĢ¬ň≤®∆ųĶńŌĶÕ≥SNR£®ADRF6510Ķń¬ň≤®∆ų◊™’Ř∆Ķ¬ ő™30MHzļÕ5MHz£¨5MHz÷–∆Ķ–ŇļŇ“Ű£¨GNSW=łŖĶÁ∆Ĺ£¨«į∂ň‘Ų“ś=12dB£© Õľ9ļÕÕľ10Ō‘ ĺ Ļ”√≤ĽÕ¨ŅĻĽžĶĢ¬ň≤®∆ų Ī£¨’ŻłŲŌĶÕ≥ĶńSFDR°£¬ň≤®∆ų4ļÕ¬ň≤®∆ų5ĪŪŌ÷ļ‹≤Ó£¨‘ŕīů≤Ņ∑÷ š»ŽĻ¶¬ ∑∂őßńŕĶńSFDRő™40dB°£’‚ «“Úő™HD3–ŇļŇ“ŰŌř÷∆ŃňSFDR°£∂‘”ŕ∆šňŻŅĻĽžĶĢ¬ň≤®∆ų£¨‘ŕīů≤Ņ∑÷∑∂őßńŕSFDR∂ľ≥¨ĻżŃň60dB°£”…”ŕ÷ų–ŇļŇ“Ű≤Ę∑«-3dBFS£¨ š»ŽĻ¶¬ ĹŌĶÕ ĪSFDR¬‘őĘŌ¬ĹĶ°£ ‘ŕĹŌłŖĶń š»ŽĻ¶¬ ňģ∆ĹŌ¬£¨SFDR ‹Ōř”ŕADRF6510¬ň≤®∆ų—Ļňű≤ķ…ķĶń–≥≤®°£  Õľ9.5łŲŅĻĽžĶĢ¬ň≤®∆ųĶńŌĶÕ≥SFDR£®ADRF6510Ķń¬ň≤®∆ų◊™’Ř∆Ķ¬ ő™30MHzļÕ5MHz£¨5MHz÷–∆Ķ–ŇļŇ“Ű£¨GNSW=ĶÕĶÁ∆Ĺ£¨«į∂ň‘Ų“ś=6dB£©  Õľ10.5łŲŅĻĽžĶĢ¬ň≤®∆ųĶńŌĶÕ≥SFDR£®ADRF6510Ķń¬ň≤®∆ų◊™’Ř∆Ķ¬ ő™30MHzļÕ5MHz£¨5MHz÷–∆Ķ–ŇļŇ“Ű£¨GNSW=łŖĶÁ∆Ĺ£¨«į∂ň‘Ų“ś=12dB£© Õľ11°ĘÕľ12°ĘÕľ13ļÕÕľ14Ō‘ ĺŌĶÕ≥ĶńHD2ļÕHD3°£ŅĻĽžĶĢ¬ň≤®∆ų4ļÕ5‘ŔīőĪŪŌ÷≥ŲŃňĹŌ≤ÓĶń–‘ń‹£¨HD2–‘ń‹‘ľő™-55dBc£¨∂ÝHD3ĹŲő™-40dBc°£¬ň≤®∆ų1°Ę2ļÕ3ĶńĪŪŌ÷“™ļ√Ķ√∂ŗ£¨HD2ļÕHD3”Ň”ŕ-70dBc°£ ‘ŕ š»ŽĻ¶¬ ∑∂őßńŕĶńĶÕ∂ň£¨HD2ļÕHD3∑÷ŃŅĪ»‘ŽĶ◊ĽĻ–°£¨ Ķľ ľ«¬ľŌ¬ņīĶń «‘Ž…ý°£ADRF6510Ķń‘Ų“śĹĶ÷Ń◊„ĻĽĶÕ“‘ļů£¨ š≥Ų‘Ž…ýŌ¬ĹĶ£¨Ō‘ ĺ≥ŲHD–ŇļŇ“Ű£¨ī”∂ÝŅ…ĹÝ–– ĶĪ≤‚ŃŅ°£ ‘ŕ š»ŽĻ¶¬ ∑∂őßńŕĶńłŖ∂ň£¨HD2ļÕHD3īů∑ýŌ¬ĹĶ°£’‚ «ADRF6510¬ň≤®∆ųĶń—ĻňűĶľ÷¬Ķń°£  Õľ11.5łŲŅĻĽžĶĢ¬ň≤®∆ųĶńŌĶÕ≥HD2£®ADRF6510Ķń¬ň≤®∆ų◊™’Ř∆Ķ¬ ő™30MHzļÕ5MHz£¨5MHz÷–∆Ķ–ŇļŇ“Ű£¨GNSW=ĶÕĶÁ∆Ĺ£¨«į∂ň‘Ų“ś=6dB£©  Õľ12.5łŲŅĻĽžĶĢ¬ň≤®∆ųĶńŌĶÕ≥HD2£®ADRF6510Ķń¬ň≤®∆ų◊™’Ř∆Ķ¬ ő™30MHzļÕ5MHz£¨5MHz÷–∆Ķ–ŇļŇ“Ű£¨GNSW=łŖĶÁ∆Ĺ£¨«į∂ň‘Ų“ś=12dB£©  Õľ13.5łŲŅĻĽžĶĢ¬ň≤®∆ųĶńŌĶÕ≥HD3£®ADRF6510Ķń¬ň≤®∆ų◊™’Ř∆Ķ¬ ő™30MHzļÕ5MHz£¨5MHz÷–∆Ķ–ŇļŇ“Ű£¨GNSW=ĶÕĶÁ∆Ĺ£¨«į∂ň‘Ų“ś=6dB£©  Õľ14.5łŲŅĻĽžĶĢ¬ň≤®∆ųĶńŌĶÕ≥HD3£®ADRF6510Ķń¬ň≤®∆ų◊™’Ř∆Ķ¬ ő™30MHzļÕ5MHz£¨5MHz÷–∆Ķ–ŇļŇ“Ű£¨GNSW=łŖĶÁ∆Ĺ£¨«į∂ň‘Ų“ś=12dB£© Ļ¶ń‹ŅÚÕľ Õľ17Ō‘ ĺŃň”√”ŕ≤‚ ‘Ĺ” ’ŃīĶń≤‚ ‘…Ť÷√Ļ¶ń‹ŅÚÕľ°£◊Ę“‚£¨–ŇļҬ∑ĺ∂ī”ADRF6801Ķń š≥Ų∂ň÷ŃAD9248Ķń š»Ž∂ň£¨ «ÕÍ»ę≤Ó∑÷Ķń°£ …Ť÷√”Ž≤‚ ‘ Ĺ” ’Ľķ≤‚ ‘…Ť÷√ĶńĶŕ“Ľ≤Ĺ «Ņ™∆Űňý”–≤‚ ‘…ŤĪł°£≤‚ ‘…ŤĪł‘§»» Ī£¨ĶÁ¬∑įŚĪō–Ž’ż»∑Ňš÷√“‘Ī„‘ŕ–ŇļŇŃīńŕ’ż≥£ Ļ”√°£ ‘ŕADRF6801įŚ…Ō£¨Ň‘¬∑ š≥ŲįÕ¬◊£¨“‘Ī„‘ŕADRF6801ļÕADRF6510÷ģľšĽŮĶ√ÕÍ»ę≤Ó∑÷Ķń÷ĪŃųŮÓļŌ–ŇļҬ∑ĺ∂°£ ‘ŕADRF6510įŚ…Ō£¨÷ī––Ō¬Ń–≤Ŕ◊ų£ļ °Ů Ň‘¬∑ š»ŽļÕ š≥ŲįÕ¬◊ °Ů ”√1¶ŐFĶÁ»›»°īķ∆’Õ®COFSĶÁ»› ‘ŕAD9248įŚ…Ō£¨“∆≥żįÕ¬◊£¨≤ĘĹęįŽł’–‘ĶÁņ¬įī’’įÕ¬◊≥ŖīÁĹÝ––ļłĹ”°£’‚—ýŅ…‘ŕADRF6510ļÕAD9248÷ģľšŐŠĻ©≤Ó∑÷÷ĪŃųŮÓļŌѨŔ°£ĪÍ◊ľAD9248∆ņĻņįŚŐŠĻ©Ķ•∂ňĹĽŃųŮÓļŌѨŔ£®Õ®ĻżįÕ¬◊£©ĽÚĶ•∂ň÷ĪŃųŮÓļŌѨŔ£®Õ®ĻżįŚ‘ōAD8138∑Ňīů∆ų£©°£”√ĽßŅ… Ļ”√Ķ•∂ň…Ť÷√£¨Õ¨ Ī“ņ»Ľ÷ī––«įőńňý Ų÷ģ»ę≤Ņ≤‚ŃŅ£®Ļ≤ń£≤‚ŃŅ≥żÕ‚£©°£¬ķŃŅ≥ŐĶÁ—Ļ…Ťő™2V°£‘ŕAD9248∆ņĻņįŚ…ŌĻĻĹ®ŅĻĽžĶĢ¬ň≤®∆ų°£”–∂ŗłŲĪŪŐý∆ųľĢļłŇŐŅ…”√ņīĻĻĹ®ŅĻĽžĶĢ¬ň≤®∆ų°£ ’ľĮ∆ņĻņįŚ£¨≤ĘĹęňý”––ŇļҬ∑ĺ∂Ѩ‘ŕ“Ľ∆ū£¨»ÁÕľ17ňý ĺ°£Ĺęňý”–ĶÁ¬∑įŚŃ¨Ĺ”÷Ń+5V£¨»Ľļů≤Ś»ŽAD9248įŚļÕ żĺ›≤…ľĮįŚ£¨≤ĘѨŔՊĻ©ĶńĶÁ‘ī°£«Ž»∑Ī£ĶÁ‘īĶÁŃų”Ž∆ŕÕŻ÷Ķ“Ľ÷¬°£ »ÁÕľ17ňý ĺÕÍ≥…Ō¬Ń–ѨŔ£ļ Ĺę łŃŅ–ŇļŇ∑Ę…ķ∆ųĶńĶ•∂ň°Ę50¶ł š≥ŲѨŔĶĹADRF6801∆ņĻņįŚĶńRFIN°£ ĹęUSBĶÁņ¬ī”PCѨŔĶĹ ĺ≤®∆ų°£ ĹęADRF6801ĶńREFIN∂ňŅŕѨŔĶĹĶÕŌŗőĽ‘Ž…ý‘ī£Ľīň ĪWenzel’ŮĶī∆ų∆Ķ¬ ő™100MHz°£ ‘ŕAgilent E4438C łŃŅ–ŇļŇ∑Ę…ķ∆ų…Ō£¨÷ī––Ō¬Ń–≤Ŕ◊ų£ļ ĹęRF‘ō≤®∆Ķ¬ …Ť÷√ő™895MHz°£ Ĺę∑ý∂»…Ť÷√ő™-30dBm°£ Ĺ”Õ®RF∂ňŅŕ°£ ‘ŕPC…Ō∆Ű∂ĮVisual Analog»ŪľĢ°£‘ŕ»ŪľĢ÷–÷ī––Ō¬Ń–≤Ŕ◊ų£ļ ≤ť’“AD9248£¨īÚŅ™FFT∆ĹĺýĽ≠≤ľ°£ …Ť÷√ĺý÷Ķő™20£¨»Ľļů…Ť÷√°į“∆∂Į∆Ĺĺý°Ī°£ ‘ň––»ŪľĢ£¨Ņ™ ľ≤…ľĮADC żĺ›°£ ī”-50dBm…®√Ť÷Ń+4dBm£¨“‘Ī„‘ŕīň≤‚ ‘…Ť÷√Ō¬≤‚ ‘Ĺ” ’Ľķ°£ADRF6510…ŌĶń‘Ų“ś ľ÷’…Ť÷√ő™ ĶŌ÷-3dBFSĶńADC š»Ž∂ň–ŇļŇĶÁ∆Ĺ£¨ľī1.0Vp-p≤Ó∑÷–ŇļŇ°£ń≥–©«ťŅŲŌ¬£¨∂‘”ŕľę–°Ķń–ŇļŇĶÁ∆Ĺ£¨ADRF6510őř◊„ĻĽĶń‘Ų“śņīīÔĶĹ1.0Vp-p≤Ó∑÷ĶÁ∆Ĺ°£ ĹęADRF6801ĽÚADRF6510ĶńIļÕQ≤Ó∑÷ š≥Ų–ŇļŇ”Ž÷ī––≤Ó∑÷÷ŃĶ•∂ň–ŇļŇ◊™ĽĽĶńŃĹŅťAD8130∆ņĻņįŚ(AD8130-EBZ) š»Ž∂ňŌŗѨ£¨ľīŅ…≤‚ŃŅEVM°£»Ľļů£¨ĹęĶ•∂ňIļÕQ–ŇļŇѨŔ÷ŃAgilent DSO90604A ĺ≤®∆ų£¨≤ĘĹę ĺ≤®∆ųѨŔĶĹ‘ň––Agilent 89600 VSA»ŪľĢĶńWindows PC°£  Õľ17.≤‚ ‘÷ĪĹ”Īš∆ĶĹ” ’ĽķĶńĻ¶ń‹ŅÚÕľ –ř∂©ņķ ∑ 2013ńÍ11‘¬°™–ř∂©įś0£ļ≥ű ľįś |

ÕÝ”—∆ņ¬Ř