一种数模混合SoC设计协同仿真的验证方法

发布时间:2010-4-9 07:27

发布者:蹦蹦

|

随着微电子工艺制造技术和电子设计自动化技术的飞速发展,集成电路已经进入系统芯片即SoC(System on Chip)时代。SoC芯片设计将数字电路、模拟电路、微处理器等集成在单一的硅芯片上,构成一个系统,实现复杂的功能。如何评估和验证数模混合SoC芯片,成为当今芯片设计者一个新的挑战。 1 固网短信电话专用SoC芯片介绍 固网短信是中国电信开通的一项通过固定电话网收发短信息的业务,由中国电信、上海贝尔、步步高、中兴通讯等公司联合进行固网信服务平台的建设。目前已在许多地区开通了这项业务。 固网短信电话专用SoC芯片是固网信息电话终端专用的微处理器芯片(以下简称为SMS芯片)。其内嵌了一个8位的微控制器(MCU,MicroController Unit),并且集成了电话主叫识别信息传送模块(CID,Calling Identity Delivery)和双音多频编码模块(DTMF,Dual Tone Multi Frequency),使固网电话支持在固网短信服务平台上接收和发送短消息。 SMS芯片的结构框图如图1所示。

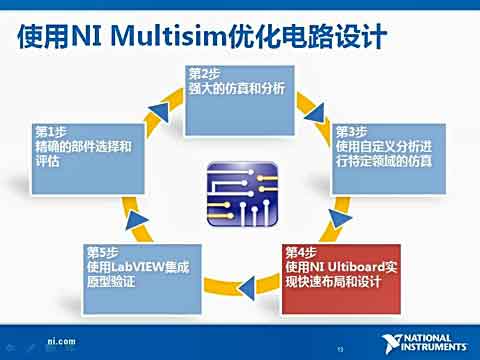

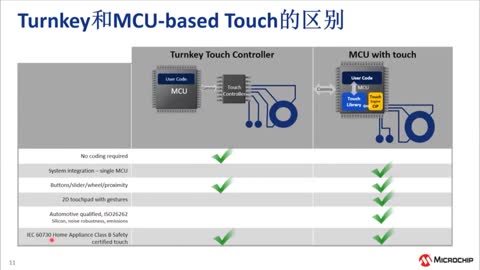

SMS芯片的主要功能是: ①CID模块识别并解调电话线上的FSK调制信号;A/D接口模块将解调后的模拟信号转换为数字信号传递给MCU,MCU对该数字信号进行一定的处理后在LCD上显示信息。 ②MCU将键盘输入的信息转换为数字信号,经A/D接口模块传递给DTMF模块,实现拨号功能。 SMS芯片的设计主要分为两部分,数字部分和模拟部分并行实现。数字部分采用基于标准单元的ASIC设计流程,其中RAM为IP模块;模拟部分采用全定制设计流程,最后将两部分整合到一块芯片上,构成SoC芯片。芯片的功能和时序验证是设计过程中的重要环节。为了实现芯片产业化,缩短设计周期,必须对数字部分、模拟部分和数模信号接口部分进行严格的功能和时序验证。 2 SMS芯片验证方案 SMS芯片数模混合设计的特点使其无法简单地使用一种仿真器进行验证,但考虑到其数模接口信号是数字的(如图1),我们可以选择以下几种验证方案。 (1)传统的验证方法 数字部分采用级仿真,通过反复调试,尽可能发现问题;模拟部分采用晶体管级仿真,以验证其正确性,如果模拟部分规模较大可以自底向上进行验证。这种验证方法无法对整个系统进行同步仿真,因此需要分别对数字部分和模拟部分的接口引脚时序进行严格的定义和验证。 (2)仅使用数字仿真器的验证方法 首先对芯片的模拟部分进行晶体管级仿真,然后根据仿真结构对模拟部分输出的数字信号时序进行Verilog行为级建模,再将该模型和数字部分一起用数字仿真器验证。这种方法仿真速度比较快,但模拟部分每进行一次修改,设计者就得重新对其进行仿真和建模;而这样的修改对于模拟部分又是比较频繁的,因此这种验证方法需要花费大量人力进行建模。 (3)仅使用模拟仿真器的验证方法 整个系统不论数字部分还是模拟部分都采用晶体管级仿真,这种验证方法不需要设计者进行任何建模,相对比较简单;但其用于仿真的时间比较长,特别是当芯片规模达到一定程度时,仿真需要花费的时间往往是设计者所不能接受的。 (4)数字仿真器与模拟仿真器协同仿真的验证方法 为了充分利用数字仿真器和模拟仿真器各自的优点,解决混合信号同步仿真问题,许多EDA供应商提供一种协同仿真的方法,即通过一个“平台”将一个模拟仿真器和一个数字仿真器连接起来。数字部分用数字仿真器仿真,模拟部分用模拟仿真器仿真,数字部分和模拟部分的接口信号通过“平台”实现同步。这种验证方法提高了仿真效率,实现了对整个系统的仿真。不过虽然“平台”可以提供两个仿真器间的同步功能,但却忽视了混合信号建模的主要问题,使设计者必须人工地在两个仿真器间并行混合信号模型的划分。 SMS芯片中数字电路MCU不适合也不需要采用晶体管级仿真。同时,由于数字部分和模拟部分之间存在数据的传送和接收,这就使数模接口部分的功能和时序验证显得尤为重要。因此,我们将采用数模混合协同仿真技术对SMS芯片进行验证,数字部分采用门级仿真,模拟部分采用晶体管级仿真,通过“平台”实现对整个系统的同步仿真,以验证其数字部分和模拟部分接口的功能和时序。 3 仿真环境 在我们所采用的仿真环境中,数字仿真器使用Synopsys公司的VCS,模拟仿真器使用该公司的NanoSim,VCS-ACE则是连接这二者的“平台”。这三者之间的关系如图2所示。

(1)VCS VCS是编译型Verilog模拟器,完全支持OVI标准的 Verilog HDL语言、PLI和SDF。VCS具有目前行业中最高的模拟性能,支持千万门级的ASIC设计,而其模拟精度也完全满足深亚微米ASIC Sign-Off的要求。VCS是Synopsys完整的验证解决方案核心。 (2)NanoSim NanoSim集成了业界最优秀的电路仿真技术,是一种具有高速、高处理能力的新一代深亚微米晶体管级电路仿真器;支持Verilog-A和VCS仿真器的接口,能够进行高级电路的仿真,其中包括存储器仿真和混合信号的仿真。 4 验证过程与结果 在进行SMS芯片整体系统仿真之前,首先要分别对芯片的数字部分和模拟部分单独进行仿真,以确保这两部分功能和时序的正确性。然后将这两部分合并,验证其接口的同步性。 下面以验证FSK调制信号的接收功能为例,构建图3所示的验证平台。

(1)FSK调制器建模 为了模拟电话线(TIP和RING,电话的接入线)上的FSK调制信号,可以在CID模拟的外围添加一个FSK调制器。用Verilog-A语言对其进行行为级建模,提供CID模块的输入信号。 该FSK调制器要求产生相位连续的FSK信号,即在码元转换时刻的相位是连接的。其调制信号可以写作:

式中:A是载波的振幅,fc是未调载波的频率,θc表示载波的初始相位,Δfd为峰值偏频,m(t)为归一化基带信号。

又由于TIP与 RING上的信号相位相反,取电压偏置为2.5V,初始相位为0,所以FSK调制器的行为级模型为: 'ihclude “std.va” 'include “const.va” module fsk_modu(in,TIP,RING); inout in; inout TIP,RING; electrical in,TIP,RING; parameter real Vbias=2.5; parameter real A=0.28; parameter real fc=1700; parameter real delta_fd=500; real time; analog begin time=$realtime(); V(TIP)<+(Vbias+A*cos(2*3.14*fc*time+2*3.14*delta_fd*idt ((1-V(in)/2.5),0.0))); V(RING)<+(Vbias+A*cos(2*3.14*fc*time+2*3.14*delta_fd*idt((1-V(in)/2.5),0.0)+3.14)); end endmodule FSK调制器的仿真波形如图4所示。

其中in为待调制码元信号,a为电话线TIP线信号,b为电话线RING线信号。 (2)模拟部分 Verilog建模 在TESTBENCH中需要例比数字部分和模拟部分,而TESTBENCH是用Verilog语言编写的,因此需要对用SPICE语言描述的模拟部分进行Verilog建模。这种建模相对比较简单,只需要用Verilog语言给出模拟部分输入、输出引脚定义。 (3)模拟部分测试矢量 待调制信号的测试矢量必须满足CID模拟与MCU之间的硬件通信协议,即:每帧数据由10位组成,第一位必须为“0”,作为起始位;最后一位必须为“1”,作为结束位,即0XXXXXXXX1。软件通信协议暂不考虑。 考虑到当“0”和“1”交替出现时是CID模拟FSK解调的最坏情况,因此取待调制信号的测试矢量为0101010101。 (4)数字部分测试程序 ROM为Verilog语言编写的行为级程序寄存器模型,通过读入编译过的汇编指令文件完成程序的装载,MCU则从ROM取指令,完成相位的功能。 MCU执行程序如图5所示。

(5)验证的理论结果 根据硬件通信协议,当测试矢量为“0101010101”时,有效的数据为“10101010”,即十六进制数据“0AAH”,所以MCU累加器将接收到数据“0AAH”。 (6)验证的实际结果 验证结果如图6所示。

图6中,in为待调制信号;R_CLK为FSK数据接收时钟信号,由CID模块产生,MCU在该时钟信号的上升沿接收数据,暂存在 FSK数据接收寄存器中;R_FDRN为数据准备好信号,由CID产生,根据汇编程序,MCU查询到该信号有产,则将FSK数据接收寄存器中的数据写入累加器acc_[7:0]中。从图6中可以看出,最后累加器接收到由模拟部分传递的数据0AAH,这与理论分析的结果相一致。因此可以得出结论:SMS芯片 FSK数据接收的功能和时序符合设计要求。 同样采用数模混合协同仿真技术,我们对SMS芯片的其它功能时序进行了验证,得到的结论符合设计要求。2002年12月,我们将芯片在CSMC采用0.6μmCMOS工艺进行流处制造,其物理版图如图7所示。

5 结论 随着系统级芯片(SoC)应用的增加,对混合信号仿真的需求也将不断扩大。数模混合仿真已经成为当今SoC设计中的重要一环,采用高效的仿真技术不但能显著提高设计质量,而且还可以减少产生面市时间。 SMS芯片采用数模混合协同仿真技术进行验证,充分利用了各个仿真器的优点,大大综合了仿真时间,实现了对整个芯片系统的同步仿真。验证得到的正确结果增强了我们投片的信号。不可否认数模混合协同仿真技术是一种高效的仿真技术。当然,这种仿真技术也存在不足:其一,使用两种仿真引擎导致设计成本增加;其二,需要人工进行数模划分。我们相信在不久的将来会出现更为理想、更为高效的数模混合仿真技术。 参考文献 1. 郭梯云 数据传输 1998 2. Lai Xinquan.Zhang Yue.Li Yushan.Liu Xuemei Behavioral Modeling of Electronic Circuit Module with Verilog-A Language [会议论文] 2000 3. YDN069-1997 YDN069-1997. 电话主叫识别信息传送及显示功能的技术要求和测试方法(暂行规定) 1998 作 者:东南大学 金肖科 凌明 茆邦琴 来 源: 单片机与嵌入式系统应用 2004(1) |

网友评论