支持Xilinx FPGA中的32位 DDR4 SDRAM

发布时间:2020-5-18 15:27

发布者:英尚微电子

|

尽管现代FPGA包含内部存储器,但可用存储器的数量始终比专用存储器芯片的存储器数量级低几个数量级。因此许多FPGA设计人员在其FPGA上附加某种类型的存储器也就不足为奇了。由于其高速和低成本,SDRAM是非常流行的存储器。它们不像静态存储器那样容易控制,因此经常使用SDRAM控制器。 FPGA器件属于专用集成电路中的一种半定制电路,是可编程的逻辑列阵,能够有效的解决原有的器件门电路数较少的问题。FPGA的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元。由于FPGA具有布线资源丰富,可重复编程和集成度高,投资较低的特点,在数字电路设计领域得到了广泛的应用。 对于控制器,针对的可能是最简单的SDRAM:一款支持用于Xilinx FPGA或Altera FPGA中的32位DDR4 SDRAM。如Kintex Ultrascale FPGA中可支持32位DDR4 SDRAM,支持免费送样及测试。 32位 DDR4 SDRAM特征 •密度 -8Gb •组织 -32M字×32位×8组 -无铅/RoHS •电源 -VDD=VDDQ=1.14V-1.26V -VPP=2.375V–2.75V •数据速率: -3200Mbps/2933Mbps/2666Mbps/2400Mbps/ 2133Mbps/1866Mbps/1600Mbps •接口:伪漏极开路(POD) •爆破长度(BL):爆破(BC)为8和4 •预充电:每个突发访问自动预充电选项 •刷新:自动刷新,自刷新 •刷新周期 -平均刷新周期0℃≤TC≤+85℃时为7.8μs+85℃ -商业:TC=0℃至+95℃ -工业:TC=-40℃至+95℃ •双数据速率架构:每个时钟周期两次数据传输 •高速数据传输通过8位预取流水线架构实现 •双向差分数据选通(DQS_t和DQS_c)与数据一起发送/接收,以便在接收器处捕获数据 •每个DRAM寻址能力(PDA) 每个DRAM可以分别设置不同的模式寄存器值,并可以单独调整。 •细粒度刷新 2x,4x模式用于较小的tRFC •最大的省电模式,功耗最低,无需内部刷新 •可编程的部分阵列自刷新(PASR) •RESET_n引脚用于上电序列和复位功能  8Gbit DDR4(x32bit)_Datasheet_v1.0.pdf

(1.49 MB)

8Gbit DDR4(x32bit)_Datasheet_v1.0.pdf

(1.49 MB)

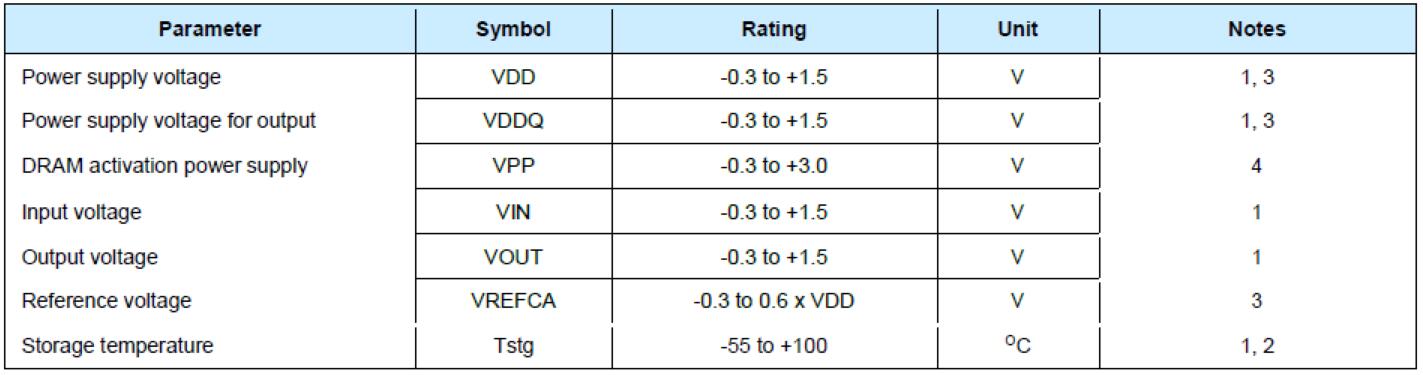

电气条件 绝对最大额定值  表1:绝对最大额定值 注意: 1. 大于绝对最大额定值列出的压力可能会导致设备永久损坏。这仅是额定压力,并不暗示在这些或任何其他条件(超出本规范的操作部分所指示的条件)下器件的功能运行。长时间暴露在绝对最大额定值条件下可能会影响可靠性。 2. 存储温度是DRAM中心/顶侧的外壳表面温度。 3. VDD和VDDQ始终必须在300mV之内。当VDD和VDDQ小于500mV时,VREFCA必须不大于0.6×VDDQ;VREFCA可以等于或小于300mV。 4.VPP必须始终等于或大于VDD/VDDQ。 工作温度条件 表2:工作温度条件 8Gb 32位 DDR4 SDRAM

|

网友评论