一种基于Flash型FPGA的高可靠系统设计

发布时间:2010-8-10 15:58

发布者:lavida

|

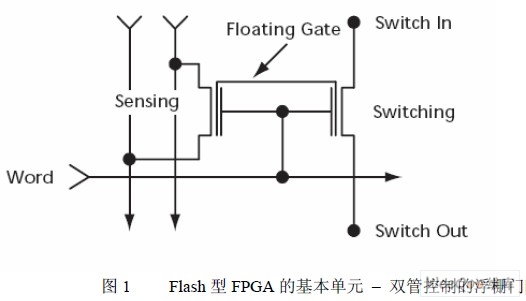

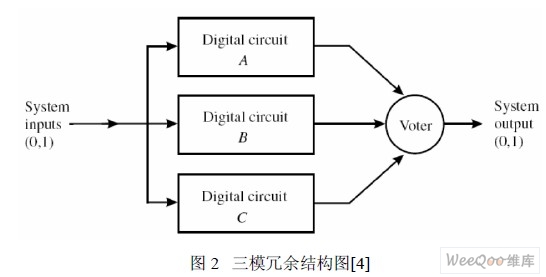

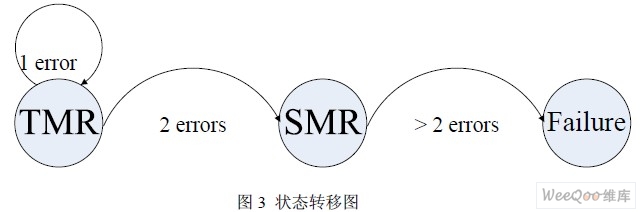

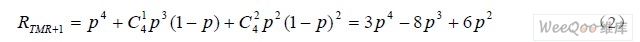

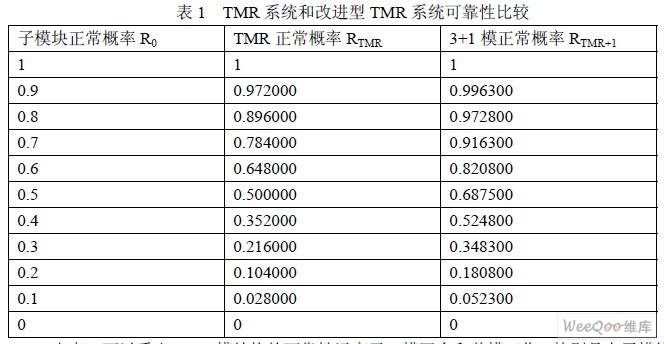

摘要:本文以星载测控系统为背景,提出了一种基于 Actel Flash FPGA的高可靠设计方案。采用不易发生单粒子翻转的 flash FPGA芯片,结合 FPGA内部的改进型三模冗余、分区设计和降级重构,实现了高实时、高可靠的系统。 2 引言 在复杂的空间环境中存在各种高能粒子和宇宙射线,星载系统的电子器件容易发生单粒子翻转等错误,造成整个系统的崩溃。对于星载系统而言,可靠性是非常重要的一项性能指标。在系统研制时,必须保证系统在局部出现故障时屏蔽和容忍错误,把错误造成的损失降到昀低。比较常用的可靠性措施包括选用抗扰等级高的元器件和适当的屏蔽设计等,但是这些措施都无法绝对预防永久性故障的发生,为了满足卫星可靠性的要求必须进行冗余设计。 本文中的设计就采用 Flash型 FPGA取代了 SRAM型 FPGA,前者在结构上的特点决定了它不容易发生单粒子翻转等错误,从而在固件上提高了可靠性。同时采用了改进型的 TMR冗余设计,在保障可靠性的同时也兼顾了实时性。 3 基本思想和系统实现 3.1 Flash型 FPGA概述目前广泛用于电子产品的 FPGA(Field-Programmable Gate Array,现场可编程门阵列)主要有反熔丝型、SRAM型和 Flash型三种。反熔丝型 FPGA利用熔丝点的通断来存储编程信息,只能烧写一次,可靠性很高,但是同时开发成本也很高,一般只在成熟正品中使用。 SRAM型 FPGA使用非常广泛,它的可编程单元是六管结构,编程信息是保存在附加的 PROM里的,每次上电时从 PROM中加载到 FPGA中,断电后编程内容消失。在航天应用中,SRAM型 FPGA昀大的缺点是容易发生单粒子翻转(Single Event Upset, SEU),以及上电加载过程中容易产生错误指令。 Flash型 FPGA的可编程单元是两个三极管组成的 flash开关,其中一个只在编程时起传感器作用,另一个控制开关的通断,两个管子共享的浮栅门存储了编程信息。 Flash型 FPGA无需附加 PROM,上电时间也很短,另外 flash相比于 SRAM不容易出现单粒子翻转,因此 Flash型 FPGA很适合航天应用。 本文中的遥控系统采用 Actel公司的 ProASIC plus系列的 APA300芯片。  3.2 系统描述 本文主要实现了高可靠遥控系统中将地面和星载计算机发送的串行码字译码成对应通道指令脉冲的功能,全部功能在一块 FPGA中实现。遥控电路板上采用两块相同的 FPGA进行双机热备份,通过 54LVC244选择输出。每块 FPGA内部又采用了下面描述的改进型 TMR设计。该系统完成了遥控译码的功能,各指令响应正常。 本文重点介绍 FPGA片内的改进型 TMR冗余设计。 3.3 改进型 TMR设计 三模冗余(TMR)是一种常用的容错技术,把需要容错的部分复制三份,然后由表决器根据多数表决原则输出结果。TMR属于静态冗余技术,它能够掩盖 1个子系统的错误,而不能修复错误。当 2个或 2个以上的子系统出错,或者表决器出错时,TMR系统将输出错误的结果。TMR技术的优点是简单易行,对于瞬时出现的错误具有良好的容错效果,但是代价是付出了 3倍的面积开销。  本文设计中采用的改进型 TMR,实质上是一种 3+n模冗余,N个子系统中昀多只有三个子系统同时处于运行状态,其余的 N-3个子系统作为备份队列,当某个子系统出现错误时,表决模块用备份的子系统替换下错误的子系统,继续维持 TMR结构。当已无备份可用时, 3模冗余系统可以进行降级重构,由 3模冗余降级为 1模。由于延长了三模冗余系统的工作时间,整个系统的可靠性得到了很大提高。 考虑到资源消耗与可靠性提高的平衡,本文设计中采用了 3+1模结构,也就是 3模冗余, 1模备份。3+1模结构的工作方式为:正常时进行三模冗余表决输出,出现第 1次永久性故障时表决处理模块能够检测出错误,在输出正常信号的同时用备用子系统替换故障子系统,继续维持 TMR结构;出现第 2 次永久故障时,表决处理模块仍然能够检测出错误,在输出正常信号的同时切除故障子系统,自动降级为单模工作直至单模子系统完全损坏。这种 3+1模结构借鉴了软件容错中的恢复块技术和动态冗余结构,能够容忍至少 2个子系统错误。由于 APA300实现遥控系统资源余量较大,采用了单片 FPGA片内冗余的方案,进一步简化了系统的复杂度。  3+1模结构的状态转移图如下, TMR、SMR和 Failure三个状态分别代表三模冗余、单模工作和系统失效。 在设计中,通过冗余单元的互锁机制(Inter-Lock, IL)来防止错误数据通过冗余单元边界传播,为此采用了分区约束的方法进行布局布线设计。分区设计不仅能够隔离错误,而且可以充分利用 APA300的 Spine分布,减少路径延迟。 在用户约束文件 GCF文件中作如下约束: 这四条语句把 U1"U4四个子系统分别限制在一个 spine内,除了全局时钟线和输入输出线以外,子系统之间没有直接的连接,这样分区布局布线以后就能够有效地隔离错误。 在保证可靠性的同时,3+1模设计昀大程度的保证了输出的实时性,不需要经过关机等待周期、重发指令周期或者输出不确定周期,能够连续输出正确结果直到系统完全倒向错误状态。为了避免系统重构时过快降级,考虑到很多错误是瞬时出现又随即恢复的软错误,因此设定错误出现一定次数(例如 3次)以后才去掉故障模块。 对于 3+1模结构,可靠性提高的代价是付出了 4倍的资源开销,另外输出时间延迟会略有增加,因为关键路径上的表决器增加了判断、替换的逻辑单元。因此这种结构只适用于资源充裕、系统频率不高的场合。在空间应用系统中,工作速度往往不是昀重要的,因而 3+1模结构实质上是用速度换面积(可靠性),在资源不足的情况下可以只对关键模块、错误敏感率高的模块进行冗余,以节省资源。 4 系统可靠性分析 假设单机的可靠性为(运行 5年后) , 普通 TMR和本文中改进型 TMR的可靠性分别为。由于 2个以上子系统同时发生错误的概率很小,假定同一时刻昀多只有一个子系统发生错误。 TMR可以容忍 1个子系统错误,可靠性相当于 3个子系统都正常的可靠性加上某一个子系统错误、其它两个子系统正常的可靠性: 同理,改进型 TMR的可靠性相当于以下三种情况的可靠性之和:  1)4个子系统都正常 2)1个子系统错误,其它 3个子系统正常 3)2个子系统错误,其它 2个子系统正常  取一系列的 R0值(0≤R0≤1),按(1)(2)两式计算出 RTMR和 RTMR+1如下表 1:  由表 1可以看出, 3+1模结构的可靠性远高于 3模冗余和单模工作,特别是在子模块可靠性降低的情况下提高可靠性的效果更为显著。 5 结论 本文提出了一种基于 Flash型 FPGA的高可靠系统解决方案,改进型的 TMR冗余利用片内备份的子系统替换出错的系统,能够长期维持 TMR系统,有效地提高可靠性。本文所述思想同样适用于多芯片 /多机情况下的冗余方案。本系统即将应用于某航天型号设备中,经过初步联试证明本系统能够满足可靠性和性能的要求。 本文作者创新点:1、将 Flash FPGA用于星载测控系统,提高了固件可靠性;2、改进型 TMR(3+1模冗余)改善了三模冗余的不足,延长了系统使用时间,大大提高了系统的可靠性。 |

网友评论