PCB设计之实例解析传输线损耗

发布时间:2022-11-10 18:21

发布者:edadoc2003

|

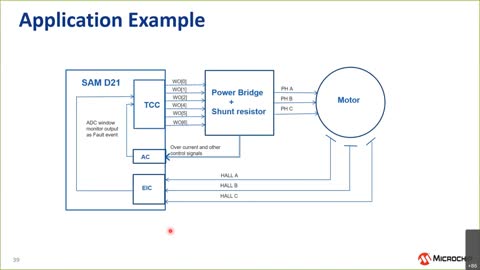

作者:一博科技 [url=]edadoc.com[/url] 高速先生成员 刘为霞 [url=]http://edadoc.com/technology-detail/89.html[/url] PCB设计之实例解析传输线损耗,随着信号速率的提升和系统越来越复杂,传输线已经不是当年的样子,想怎么设计就怎么设计了。PCB仿真设计也越来越难了,现在板子一大,线长轻轻松松上10inch,可能还会跨个背板,经过几个连接器,这样的情况,传输线的损耗就是我们设计中不得不考虑的问题了,不然的话,可能分分钟就翻车了。 那么影响损耗的因素有哪些呢?有哪些又是我们在设计中可以控制的呢?相邻线的串扰,阻抗不匹配,辐射等等因素都可能对损耗造成影响,这些也都可以从设计层面进行优化,尽量减小影响。还有一个最关键的损耗来源,就是我们的传输线不是理想传输线,是有损传输线,本身造成的损耗才是最主要的。下面我们通过一对差分线的仿真来具体说说怎么通过设计来控制损耗。 一般的传输线损耗分为两个部分,一个部分是介质损耗,一个部分是导体损耗。介质损耗的话,主要是板材参数的影响。导体损耗,主要是本身传导损耗,趋肤效应和表面粗糙度。下面两张图是仿真传输线模型时需要设置的参数,这次我们选择的是内层差分线做演示。需要在这个界面编辑线宽,间距,铜厚,以及到参考层的介质厚度等参数,编辑完成后,点击OK即可。 编辑完差分线的参数后,界面就如下图所示。在这个界面,我们可以编辑材料介电常数,损耗因子,铜箔粗糙度,蚀刻因子等参数。 再设置好长度,就可以仿真得到下面的插损曲线了。 上面看到的是传输线的整体的损耗,下面我们看下介质损耗和导体损耗在FR4板材和目前的层叠情况下的一个比例情况,后续就可以比较方便去调整参数减小损耗了。 每周一篇技术文章,学习更多内容,请关注二维码 [url=]  [/url] [/url] |

网友评论