»щУЪDDSРѕЖ¬AD9852µД»щЧјФґЙијЖ

·ўІјК±јдЈє2010-11-12 14:21

·ўІјХЯЈєeetech

|

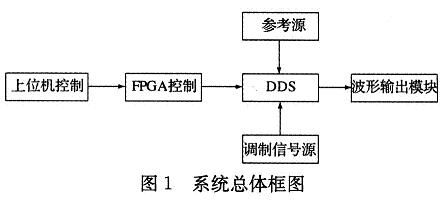

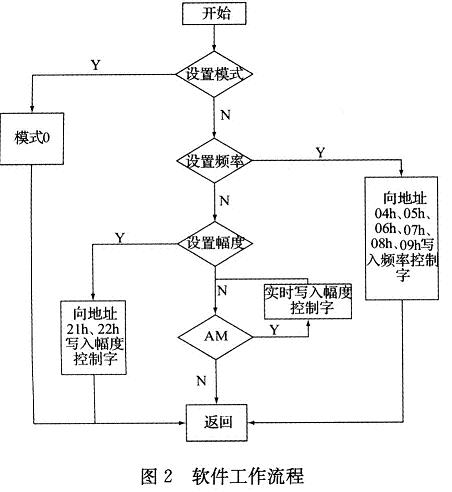

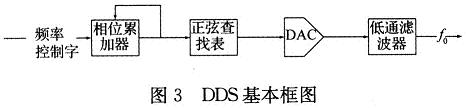

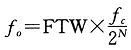

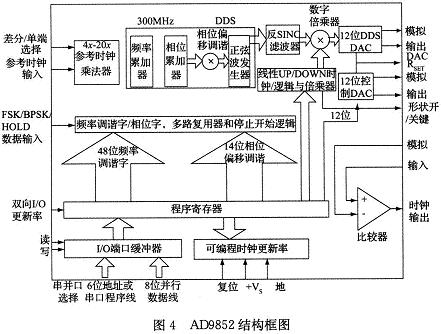

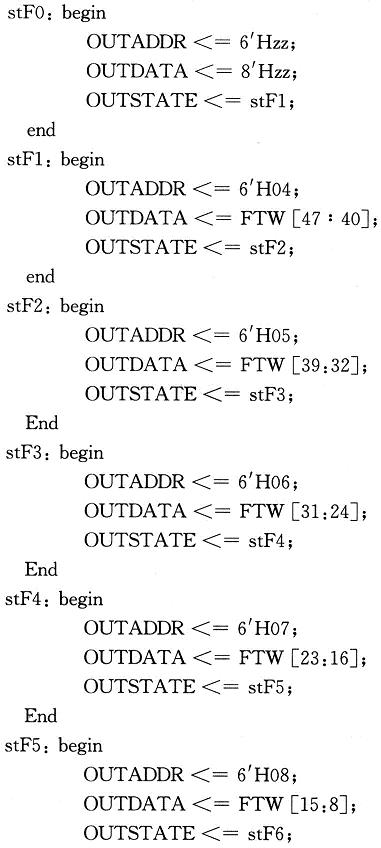

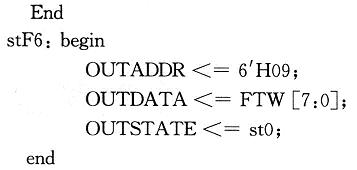

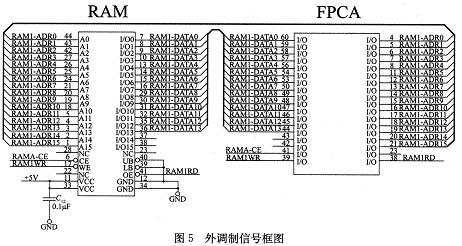

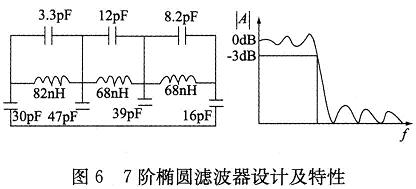

Ц±ЅУКэЧЦЖµВКєПіЙ(DD6)КЗТ»ЦЦТФ№М¶ЁµДѕ«И·К±ЦУФґОЄ»щЧјЈ¬АыУГКэЧЦґ¦АнДЈїйІъЙъЖµВКєНПаО»ѕщїЙµчµДКдіцРЕєЕµДјјКхЎЈЛжЧЕі¬ґу№жДЈјЇіЙµзВ·єНОўµзЧУјјКхµД·ўХ№Ј¬ПЦґъёЯРФДЬЎўёЯјЇіЙ¶ИєНРЎМе»эµДDDSІъЖ·ХэїмЛЩИЎґъґ«НіµДДЈДвРЕєЕЖµВКєПіЙјјКхЈ¬іЙОЄБЛХвАаОКМвРВµДЅвѕц·Ѕ°ёЎЈ±ѕОДАыУГFPGAјЖЛгіцПаУ¦µДЖµВКїШЦЖЧЦЈ¬Іў¶ФDDSРѕЖ¬AD9852ЅшРР±аіМЈ¬ЧоЦХµГµЅЛщТЄЗуµДКдіцІЁРОЎЈ 1 ПµНіЧЬМе·Ѕ°ёЙијЖ »щЧјФґЦчТЄУЙЙПО»»ъїШЦЖЎўFPGAїШЦЖЎўDDSЎўІОїјФґЎўµчЦЖРЕєЕФґј°ІЁРОКдіцДЈїйЧйіЙЈ¬ИзНј1ЛщКѕЎЈЙПО»»ъїШЦЖµҐФЄКЗУЙјЖЛг»ъНЁ№эUSBЧЬПЯБ¬ЅУЦБµзВ·°еЅшРРїШЦЖІЩЧчЎЈFPGAїШЦЖµҐФЄКµПЦУлЙПО»»ъїШЦЖµҐФЄЅ»»ҐРЕПўЈ¬Н¬К±ТФІўРР·ЅКЅПтDDSРѕЖ¬·ўЛНїШЦЖЧЦЈ¬ТФ№ЬАнЖдДЪІїјДґжЖчЎЈІОїјФґОЄDDSМṩёЯѕ«ЧјµДК±ЦУѕ§ХсЈ¬И·±ЈDDSКдіцРЕєЕµДЖµЖЧґї¶ИЎЈµчЦЖРЕєЕµҐФЄОЄDDSМṩНвІїµчЦЖРЕПўЎЈІЁРОКдіцДЈїйУЙµННЁВЛІЁЖчЎўФЛЛг·ЕґуЖчј°µзЧиНшВзЧйіЙЈ¬ЦчТЄНкіЙDDSКдіцРЕєЕµДВЛІЁЈ¬·ЕґуµИ№¦ДЬЎЈ  ПµНіЙПµзёґО»єуЈ¬µзВ·°еЙПµДВМЙ«LED¶юј«№ЬЙБЛёМбКѕХы»ъґ¦УЪХэіЈЧґМ¬ЎЈµ±УРDDSІЁРОКдіцК±Ј¬µзВ·°еЙПµДА¶Й«LED¶юј«№ЬЙБЛёМбКѕ№¤ЧчХэіЈЎЈ 2 ПµНіДЈїйЙијЖ 2Ј®1 ПµНіИнјюЙијЖ »щЧјФґµДЙПО»»ъїШЦЖІЙУГCУпСФ±аіМКµПЦЈ¬ЦчТЄНкіЙ¶ФFPGAДЪІїјДґжЖчµД¶БРґІЩЧчЈ¬Ѕш¶шїШЦЖ°еЙПёчЦЦУІјюЧКФґµД№ЬАнЎЈБнНвЈ¬DDSµДЖµВКїШЦЖЧЦµДјЖЛгТІУЙЙПО»»ъИнјюјЖЛгµГµЅЎЈFPGAЅУКХµЅЙПО»»ъµДГьБоЈ¬ѕЅвОцєуПтDDSµДДЪІїјДґжЖчРґИлїШЦЖЧЦЈ¬НкіЙПаУ¦№¦ДЬЎЈН¬К±Ј¬FPGAёєФрµзВ·°еЙПµДёчЦЦК±ЦУ№ЬАнЎЈПµНіИнјюµДЧЬМ幤ЧчБчіМИзНј2ЛщКѕЎЈ  2Ј®2 ЖµВКїШЦЖЙијЖ ±ѕОДІЙУГDDSјјКхІъЙъЖµВКїЙµчµДІЁРОЈ¬ѕЯУРЖµВК·Ц±жВКёЯЈ¬ПаО»Б¬РшµИУЕµгЎЈDDS»щ±ѕїтНјИзНј3ЛщКѕЎЈ  DDSµД»щ±ѕЅб№№°ьАЁЈєПаО»АЫјУЖчЈ¬ХэПТІйХТ±нROMЈ¬КэДЈЧЄ»»ЖчDACµИЎЈDDSУРБЅёцЦчТЄИ±µгЈєТ»КЗКдіцЖµВКµНЈ¬¶юКЗКдіцЖµЖЧЦРФУЙў¶аЎЈКдіцЖµВКµНЦчТЄКЬDDS№¤ЧчЖµВКµДПЮЦЖЈ¬ЛжЧЕОўµзЧУјјКхµД·ўХ№Ј¬ХвёцИ±ПЭ»бЦ𽥵õЅГЦІ№ЎЈDDSКдіцЖµЖЧЦРµДФУЙўКЗDDSЛщ№МУРµДЈ¬ХвКЗУЙDDSµД№¤Чч·ЅКЅѕц¶ЁµДЎЈ DDSµД»щ±ѕ№¤ЧчФАнКЗЈєПаО»АЫјУЖчФЪNО»ЖµВКїШЦЖЧЦFTWµДїШЦЖПВЈ¬ТФІОїјК±ЦУЖµВКfcОЄІЙСщВКЈ¬ІъЙъґэєПіЙРЕєЕµДКэЧЦПЯРФПаО»РтБРЈ¬Ѕ«ЖдёЯMО»ЧчОЄµШЦ·ВлНЁ№эХэПТІйСЇ±нROM±д»»Ј¬ІъЙъLО»¶ФУ¦РЕєЕІЁРОµДКэЧЦРтБРS(n)Ј¬ФЩУЙКэДЈЧЄ»»ЖчЅ«ЖдЧЄ»»ОЄЅЧМЭДЈДвµзС№ІЁРОS(t)Ј¬ЧоєуУЙѕЯУРДЪІеЧчУГµДµННЁВЛІЁЖчLPFЅ«ЖдЖЅ»¬ОЄБ¬РшµДХэПТІЁРОЧчОЄКдіцЎЈFTWєНfcК±ЦУЖµВК№ІН¬ѕц¶ЁБЛDDSКдіцРЕєЕµДЖµВКfoЈ¬ЛьГЗЦ®јд№ШПµВъЧгЈє  УЙЙПїЙЦЄЈ¬DDSјјКхїЙТФАнЅвОЄКэЧЦРЕєЕґ¦АнЦРРЕєЕЧЫєПµДУІјюКµПЦОКМвЈ¬јґёш¶ЁРЕєЕ·щ¶ИЎўЖµВКЎўПаО»ІОКэЈ¬ІъЙъЛщРиТЄµДРЕєЕІЁРОЎЈґУПµНіµДЅЗ¶ИїЙТФИПОЄКЗёш¶ЁКдИлК±ЦУfcєНЖµВКїШЦЖЧЦFTWЈ¬КдіцДіТ»¶ФУ¦µДХэПТРЕєЕЎЈБнНвЈ¬ТІїЙТФИПОЄDDSКЗТ»ёцїЙ±дµДіМРтРЎКэ·ЦЖµЖчЎЈ ±ѕОДЦРµДDDSРѕЖ¬ІЙУГµДКЗAnalog Device№«ЛѕЙъІъµДAD9852РѕЖ¬Ј¬К±ЦУЖµВКЧоёЯїЙТФґпµЅ300MHzЈ¬ДЪІїјЇіЙБЛ12О»DACЈ¬ПаО»АЫјУЖчµДО»КэОЄ48О»Ј¬ІўЗТѕЯУРFSKЈ¬PSKµИКэЧЦµчЦЖ№¦ДЬЎЈAD9852КЗѕЯУРёЯјЇіЙ¶ИµДDDSРѕЖ¬Ј¬ДЪІїЅбєПУРёЯЛЩРФДЬµДDACєНТ»ёц±ИЅПЖчЈ¬№№іЙБЛТ»ёцКэЧЦїЙ±аіМµДєПіЙЖчЎЈµ±ёш¶ЁТ»ёцѕ«И·µДІОїјК±ЦУФґК±Ј¬AD9852ѕН»бІъЙъТ»ёцёЯОИ¶Ё¶ИЈ¬ЖµВКЎўПаО»ј°·щ¶ИѕщїЙ±аіМµДХэПТІЁКдіцЎЈAD9852µДЖµВКїШЦЖЧЦґпµЅ48О»Ј¬К№ЖдЖµВК·Ц±жВКїЙґп1¦МHzЎЈЖдПаО»ЅШ¶ПµЅ17О»Ј¬К№µГAD9852ѕЯУРј«єГµДЧФУЙФУЙў¶ЇМ¬·¶О§SFDRЎЈAD9852»№Мṩ14О»µДКэЧЦїШЦЖµДПаО»µчЦЖЎЈЖдЅб№№їтНјИзНј4ЛщКѕЎЈ  Хы»ъЙПµзёґО»єуЈ¬ОЄЙиЦГДіТ»ЖµВКЦµЈ¬РиТЄЅ«ЖµВКїШЦЖЧЦґУёЯО»ЦБµНО»ТАґОТФІўРР·ЅКЅРґИлAD9852µДµШЦ·04hЦБµШЦ·09hЈ¬VreilogHDLіМРтґъВлИзПВЈє  2Ј®3 ·щ¶ИїШЦЖЙијЖ AD9852ДЪЗ¶µзБчКдіцРНDACЈ¬ёД±дЖдКдіц·щЦµУРБЅЦЦ·Ѕ·ЁЈє1)AD9852µДКдіцЧоґу·щЦµУЙБ¬ЅУЦБ56ТэЅЕµДµзЧиRsetѕц¶ЁЈ¬ЧоґуВъ°Ъ·щКдіцµзБчОЄ20mAЈ¬µзЧиRsetУлКдіцµзБчIoutµД№ШПµОЄЈєIout=39Ј®9ЈЇRsetЈ»2)AD9852µДµШЦ·21hЎў22hОЄ·щ¶ИїШЦЖјДґжЖчЈ¬ёьёДЖдїШЦЖЧЦјґїЙёД±дКдіцРЕєЕ·щЦµЎЈ Хы»ъЙПµзёґО»єуЈ¬ОЄЙиЦГДіТ»·щЦµЈ¬РиТЄЅ«·щ¶ИїШЦЖЧЦґУёЯО»ЦБµНО»ТАґОТФІўРР·ЅКЅРґИлAD9852µДµШЦ·21hЎў22hЈ¬VreilogHDLіМРтґъВлИзПВЈє  2Ј®4 AMЙијЖ »щУЪ2.3МЦВЫµД·щ¶ИїШЦЖЙијЖЈ¬јУИлНвµчЦЖРЕєЕїЙЅшТ»ІЅКµПЦAMµчЦЖЈ¬ЖдЦРЈ¬НвІїµчЦЖРЕєЕµДІъЙъїтНјИзНј5ЛщКѕЈє  Нј5ЦРЈ¬RAMґжґўНвµчЦЖРЕєЕІЁРОЈ¬±ѕОДЦРРиТЄґжґўХэПТІЁІЁРОЈ¬УЙRAMєНFPGA№ІН¬№№ЅЁNCOЎЈґжґўµДКэЦµУЙЙПО»»ъјЖЛгµГіцЈ¬ІўНЁ№эFPGAРґИлRAMЦРЎЈRAMЦРµДКэѕЭ±»FPGA¶БіцєуЈ¬УЙКэЧЦіЛ·ЁЖч¶ФЖдЅшРР·ЕґуЈ¬іЛПµКэТтЧУУЙAMµДµч·щЙо¶Иѕц¶ЁЎЈПтAD9852µДµШЦ·21hЎў22h(·щ¶ИїШЦЖјДґжЖч)РґИлНвІїµчЦЖРЕєЕЛщ¶ФУ¦µДІЁРОКэѕЭЈ¬јґїЙКµПЦµчЦЖЛЩВКЎўµчЦЖЙо¶ИѕщїЙїШµДAMµчЦЖЎЈ 2Ј®5 ІЁРОКдіцЙијЖ AD9852ЛщІъЙъµДРЕєЕЦ±ЅУУЙЖчјюДЪІїµДУаПТDACКдіцЈ¬ДЪІїІ»є¬µННЁВЛІЁЖчЈ¬№КТЄ¶ФЖдКдіцРЕєЕЅшРРВЛІЁґ¦АнЎЈ±ѕОДЦРЈ¬ОЄБЛЅµµНAD9852ДЪІїПµНіК±ЦУµДёЙИЕЈ¬ІЙУГБЛѕЯУРПВЅµЛЩ¶ИёьїмЎўЗТЅПХ№э¶ЙґшМШРФµД7ЅЧНЦФІВЛІЁЖчЎЈИзНј6ЛщКѕЎЈ  AD9852КдіцРЕєЕµД·щ¶И·¶О§ЅПРЎЈ¬РиТЄёщѕЭКµјКУ¦УГЗйїцЅшРР·Еґуґ¦АнЈ¬±ѕОДІЙУГФЛЛг·ЕґуЖчLM7171ґоЅЁёє·ґАЎ·ЕґуµзВ·ЎЈ 3 ЅбКшУп ±ѕОДЅйЙЬБЛ»щЧјФґµДЙијЖ·Ѕ·ЁЈ¬ІЙУГDDSјјКхЈ¬ѕЯУРЖµВК·Ц±жВКёЯЎўПаО»Б¬РшЎўµНПаФлµНФУЙўµИУЕµгЎЈ»щЧјФґµДЖµВКЎў·щ¶ИѕщїЙїШЎЈН¬К±Ј¬ВЫКцБЛAMµДКµПЦ·Ѕ·ЁЈ¬Па¶ФУЪґ«НіДЈДв·ЅКЅµДЙијЖ·Ѕ·ЁЈ¬ёьјУЗб±гЎўРЎЗЙЈ¬ЗТПЯРФ¶ИБјєГЈ¬±гУЪРЈЧјєНЕъЙъІъЎЈёГDDSТСК№УГУЪ±гРЇКЅРЕєЕФґЦРЈ¬ѕКµІвХы»ъПµНіФЛРРОИ¶ЁЈ¬ФЪЧЬІОДіПоДїЦеõЅКµјКУ¦УГЈ¬ґпµЅБЛФ¤ЖЪµДДї±кЈ¬ѕЯУРНЖ№гјЫЦµЎЈ |

НшУСЖАВЫ