赛灵思ISE 11.1 量身打造四种工具流程

发布时间:2010-11-8 11:00

发布者:eetech

|

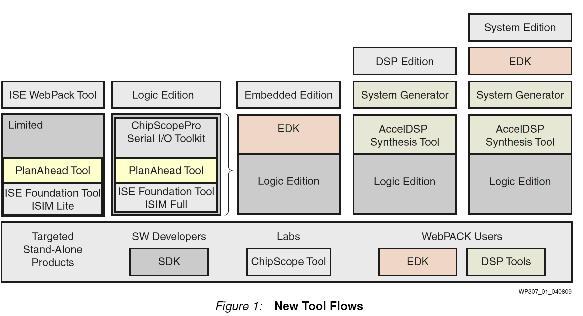

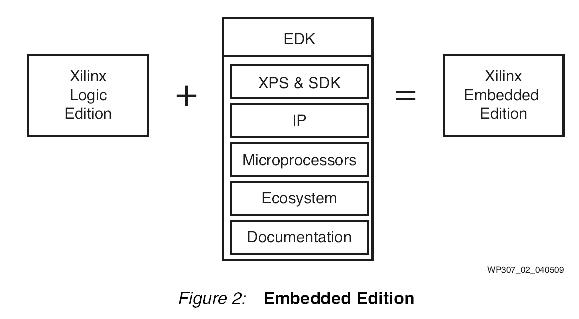

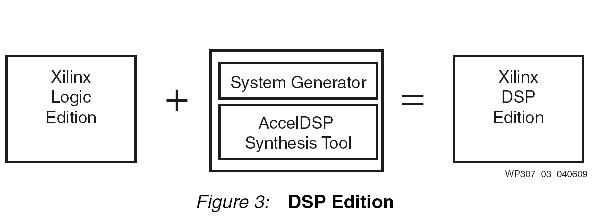

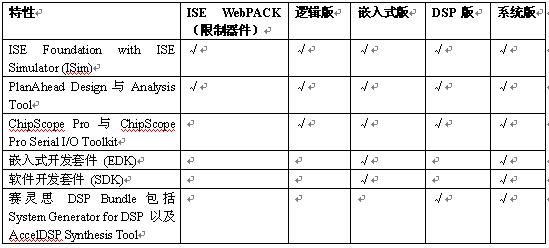

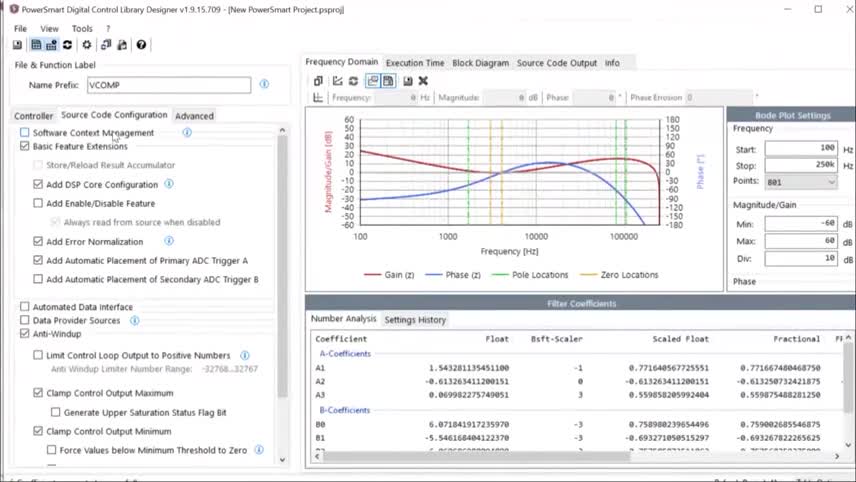

随着 Xilinx? ISE? 设计套件 11.1 的推出,赛灵思在优化设计方法、更好地满足不同技能客户的多样化需求, 以及帮助客户利用赛灵思 FPGA 目标设计平台进行创新设计方面迈出了一大步。赛灵思 ISE 设计套件 11.1同时推出四种全新的工具流程,专为逻辑设计人员、嵌入式开发人员、DSP算法开发人员以及系统集成人员量身定制,以满足他们的不同要求。此前,赛灵思的客户主要是逻辑设计人员,他们是精通硬件设计和硬件描述语言 (HDL) 的电气工程师。不过,在过去 8 年间,随着各代 Virtex? 和 Spartan? FPGA 产品的推出,逻辑单元以及 MPU 和 DSP 等嵌入式软硬件处理器呈指数级增长。在此情况下,赛灵思的客户中迅速增加了大量嵌入式软硬件工程师、DSP 算法开发人员和系统集成人员,他们都使用赛灵思的器件来构建高级片上系统。也就是说,不仅多领域的设计团队在使用赛灵思的器件,而且很多情况下,就连对 HDL设计不了解或了解甚少的人如今也都在用赛灵思 FPGA开展系统设计工作。 在推出 ISE 设计套件 11.1之前,赛灵思为所有客户提供了一套完整的工具和 IP。每个用户可以根据 FPGA 编程的需要选择使用不同的工具。不过,如果客户对逻辑/连接设计不熟悉的话,可能会对众多工具和IP的选择感到无所适从。举例来说,如果客户不熟悉硬件调试,可能就不了解 ChipScope? Pro 分析器的优点,不知道这款工具能自动完成调试任务,可以帮助用户简化设计工作。为了帮助不同设计领域的用户在熟悉的可定制环境中更高效地开展设计工作,赛灵思现在推出了四种全新的ISE 设计套件配置版本:逻辑版本、嵌入式版本、DSP 版本和系统版本(见图 1)。  图 1:全新工具流程 赛灵思对不同领域的客户进行了认真地调查,了解其设计方法,看看他们会使用赛灵思和第三方合作伙伴提供的哪些工具成功进行赛灵思 FPGA设计工作。 赛灵思的软件设计部根据上述调查研究推出了四种全新的 ISE 设计套件 配置版本。这四种配置版本既能帮助经验丰富的客户优化工具选购,也能帮助FPGA设计新手轻松确定哪些工具最适合他们的设计需求。每个配置版本都配套提供全面的设计创建、验证和实施工具以及针对特定领域的 IP。 上述四种新版本都可以定制,因此用户能根据设计流程的需要选择添加赛灵思或第三方合作伙伴提供的其他工具。赛灵思不会规定用户的设计流程,而是创建了可扩展、可定制的基础流程。此外,设计经理可根据设计团队的需求和每名设计团队成员的实际技能选择最适当的许可证数量和类型。举例来说,新推出的四种配置版本允许客户为设计团队添加诸如赛灵思软件开发套件 (SDK) 等额外的许可证选项,这样设计团队就能让数名软件开发人员为单个 FPGA 编写代码,而不必像过去那样购买整套嵌入式开发套件 (EDK)。 全新 ISE 设计套件配置版本的推出是赛灵思目标设计平台战略的关键部分,可帮助赛灵思集中精力推出市场上最佳的 FPGA硅芯片,并配套提供业界一流的软硬件设计工具、IP、开发板以及技术支持,帮助客户取得成功,并让客户集中精力开展增值设计工作,尽快向市场推出创新设计。 全新 ISE 设计套件配置版本 赛灵思 ISE 设计套件 11.1提供了四种全新的不同配置版本:逻辑版本、嵌入式版本、DSP 版本和系统版本。每种版本都提供完整的设计流程,包括相关工具、针对特定领域和应用的IP,以及参考设计。 除了提供上述四种全新的ISE 设计套件配置版本外,赛灵思还继续推出 ISE WebPACK?软件(赛灵思工具流程的限定器件版)、SDK、ChipScope Pro 分析器、EDK和DSP(AccelDSP? 综合工具和System Generator for DSP),作为独立的产品供用户添加到自己的流程中。 逻辑版本 全新逻辑版本是面向RTL设计的完整流程,其特性有助于缩短运行时间,提高存储器利用率、可用性、精确度,以及优化功耗等,相对于前一版本而言,不仅能将动态功耗降低高达 10%,存储器利用率提高28%,而且还可将布局和布线编译时间缩短1/2。 逻辑版本既可作为所有赛灵思设计人员所选版本流程的基础,也可作为一个独立的套件,其包括所有赛灵思老客户熟悉的工具。 逻辑版本包括 ISE Foundation? 软件、PlanAhead? 设计分析工具、带Serial I/O工具包的 ChipScope Pro 分析器、ISE Simulator 以及 CORE Generator? 工具 IP。 逻辑版本:创建设计方案 在逻辑版本流程中,用户可在 ISE Foundation 中打开 ISE Project Navigator以启动项目。利用该工具,用户可启动 CORE Generator 界面并选择最适合设计需要的 IP 核。随后用户可用 Project Navigator 中的 HDL 编辑器来编写设计方案的 HDL 表示。CORE Generator 软件包括数百个针对专门领域和应用的内核,允许用户快速将预定义的功能添加到设计方案中,从而集中主要精力创建设计方案的增值部分。在 ISE 设计套件 11.1 工具中,赛灵思针对视频市场需求增加了新的IP,也为所有赛灵思内核提供了版本数据,使用户全面监控内核情况。 设计人员随后可用 ISE 设计套件 软件中的赛灵思存储器接口生成器 (MIG) 工具生成适用于赛灵思 FPGA 的存储器控制器和接口。MIG 工具还可生成未加密的 Verilog 或 VHDL 设计文件、UCF 约束文件、仿真文件和实施脚本文件,以简化设计流程。在上一版本的 ISE 设计套件 软件中,MIG 用户在修改存储器模块的引脚分配时必须了解布局、布线和时序限制情况。在 ISE 设计套件 11.1 中,赛灵思对相关工具进行了改进,布局和布线引擎在存储器接口的引脚分配发生变动时能自动实施设计方案(用户不必手动改变布局和布线限制)。此外,在将功能集成到设计方案中时,用户还能获得 PCIe? 接口内核的可预见时序功能。ISE 设计套件 11.1 工具目前支持 DDR3 SDRAM、DDR2 SDRAM、DDR SDRAM、QDRII SRAM、DDRII SRAM以及RLDRAM II。 用户选定模块并创建 HDL 表达后,即可综合设计方案,执行平面规划,并前瞻性地进行引脚分配。 针对逻辑综合,ISE 设计套件 软件提供了内置的 XST 综合引擎。在 ISE 设计套件 11.1 中,XST 综合的运行速度比上一版本平均提高 1.6 倍。 所有 ISE 软件版本的捆绑(包括 ISE WebPACK 工具)都免费配套提供 PlanAhead 软件的完整版。PlanAhead 工具是一款功能齐全的设计分析驾驶舱,提供了高级 FPGA 实施管理的关键特性,如I/O引脚分配、平面规划、设计分析和实施等功能。现在,我们可从 Project Navigator 中调用 PlanAhead 工具,执行引脚规划和平面规划等工作。此外该工具也可作为独立的可执行文件使用,提供高级实施和调试功能。 在 ISE 设计套件 11.1 中,用户能通过 PlanAhead 工具获得 ChipScope Pro 调试工具内核插入功能,其中包括全新向导功能,能帮助用户在所有设计方案中方便地插入测试监控逻辑,从而更方便地监控信号,随后还能通过 ChipScope Pro 工具查找错误。 设计人员可用 PlanAhead 软件的引脚布局功能来进行引脚分配,再将引脚布局信息发送给PCB 设计人员,从而尽早启动 PCB 开发工作。 逻辑版本用户还能在设计流程的各个环节利用 PlanAhead 软件中的 TimeAhead 功能来获得实施布局和布线估算,了解给定的平面规划安排对时序预算会产生什么影响。用户获得大致的平面规划后,就能利用实施运行功能。该功能驱动 ISE 软件的布局和布线引擎创建一种或多种不同设计实施方案,以及尝试多种不同的布局方案,并最终确定在单元利用率、节能和设计性能等方面表现最出色的布局方案。在布局过程中,用户可发现出现时序违规的区域,然后对功能和模块调整修改,优化设计方案,解决时序问题,并快速再次运行实施方案来比较结果。 逻辑版:采用 ISE 设计套件 验证设计方案 逻辑版还包含广泛系列的分析与测试工具,可帮助用户验证其设计方案的功能性、时序与功耗。 逻辑版针对逻辑仿真提供了 ISim 仿真器。此外也可使用 Mentor Graphics ModelSim Xilinx Edition (MXE-III)、Cadence NCSim 以及 Synopsys VCS 仿真器。在 ISE 11.1 软件中,ISim的运行速度比此前版本 10.1 (service pack 3) 快 2 倍。ISE 软件的逻辑版还集成了更快速的SecureIP 仿真模型,能对专用模块进行建模。此外,ISim 现在还提供了类似于示波器的波形察看器和导航功能,能编写 Switching Activity Interchange Format (SAIF) 以支持赛灵思 XPower工具的功率估算,同时还能导入和导出用户波形设置。 逻辑版针对功耗分析提供了 XPower Estimator 和 Analyzer 工具。用户首先通过输入频率、器件利用率以及 I/O 类型等数据完成 XPower Estimator 的数据表单,明确其设计方案的功耗目标。设计方案的放置和布线完成后,用户可使仿真器生成 VCD 文件,并用 XPower Analyzer 确保设计方案能够满足其功耗目标。 在逻辑版中,ChipScope Pro 工具使用户能直接在其设计方案中插入逻辑分析器、总线分析器以及虚拟 I/O 低规范软件内核 (Low-profile software core)。用户插入分析器 IP 后,即可查看嵌入式或软处理器等所有内部信号或节点,如同使用了外接示波器。 ISE 11.1软件还提供了 ChipScope Pro Serial I/O 工具套件作为 ISE 设计套件 各版本的标准特性。该工具使用户能够设置并调试 Virtex-4 FX、Virtex-5 LXT、Virtex-5 SXT、Virtex-5 FXT 以及 Virtex-5 TXT FPGA 串行 I/O 通道,测量多通道的比特误差率,在串行 I/O 通道与系统其他部分交互的同时实时调节高速串行收发器参数等。此外,该工具还包含支持所有标准串行 I/O 数据分组的内置模式生成器和模式接收机。 逻辑版:采用 ISE 设计套件 实施设计 逻辑版还包含更高性能的放置与布线引擎。 赛灵思已添加了最新的内置活动估算引擎来实施工具流程,能在设计的实施阶段自动识别功耗大的模块。识别出功耗大的模块之后,该工具可执行再综合任务,以便在相关模块中重新编辑可减少这些模块中开关元件的逻辑。 此外,赛灵思还在 ISE 软件中为放置和布线引擎添加了新的功耗降低特性。ISE 11.1 软件放置器现在可提供最新的时钟门控特性,在用户的指导下可采用全局时钟缓冲器来替代高扇出寄存器时钟启用机制,而该特性反过来不仅有助于减小布线电容,而且还能够最大限度地缩短连线长度,从而使器件的整体动态功耗锐降 10%。 除了低功耗特性之外,ISE 11.1 软件的放置与布线引擎与 10.1 版本相比运行速度快了 2倍,而 SmartGuide 中的增量实施引擎的运行时间也加快了 2 倍。此外,赛灵思还为 Linux版的放置和布线引擎添加了多线程放置支持,可充分发挥多内核处理器工作站的优势,从而帮助用户进一步加速放置与布线的运行时间。 此外,赛灵思还对 ISE 11.1 软件中的 SmartXplorer 进行了升级,其目前可支持计算中心的各个系统,使设计人员能够在整个计算主机网络上的执行多个实施运行。SmartXplorer 支持将实施运行提交给装入程序共享设备 (LSF) 与 Sun 网格引擎 (SGE) 分布式计算中心来处理,而 PlanAhead 软件还支持将实施运行提交给多个 Linux 主机来执行,从而可实现并行处理。 嵌入式版本 在全新嵌入式版本中,赛灵思将其备受欢迎的嵌入式开发套件 (EDK) 与逻辑版本进行了捆绑(见图2)。嵌入式版本旨在满足那些希望在设计过程中充分利用嵌入式处理器高灵活优势的客户的需求。赛灵思提供了两款可实现最高设计灵活性的处理器内核:MicroBlazeTM 软处理器 32 位内核与 PowerPC?440 嵌入式处理器内核。此外,嵌入式版本还提供必要的驱动程序、软件应用程序,以及嵌入式系统设计人员非常熟悉的调试功能。为积极响应客户需求,赛灵思还在 ISE 设计套件 11.1 软件中新增了 EDK 的软件开发套件 (SDK),,SDK 是一种面向软件设计人员的低成本、独立许可配置。 嵌入式版本软件的突出优势包括如下: ?SDK 可为专注于嵌入式软件应用开发与调试的用户提供独立配置,从而可简化用户界面,与较早版本的 EDK 相比,显著降低了磁盘空间占用; ?采用 Base System Builder (BSB) 的双处理器设计创建自动操作; ?在使用赛灵思目标设计平台进行设计时,新版 MicroBlaze 处理器 (7.20) 可实现更高的优化性。  图 2:嵌入式版本 在嵌入式版本中使用 EDK 进行处理器编程 EDK 是由 赛灵思Platform Studio (XPS) 与 SDK 工具、嵌入式 IP、微处理器内核、文档以及诸如 Wind River 与 Monta Vista 等第三方提供的接口组成。 在嵌入式版本设计流程中,用户首先要创建设计 RTL,并将其导入 Project Navigator。如果他们想在设计方案(Virte-4 与 Virte-5 器件中的 MicroBlazeTM 软处理器或 PowerPC 处理器)中添加微处理器内核,应激活 XPS 工具。 XPS 包括高级向导工具 BSB,使用户能够通过一系列鼠标点击选择在设计方案中采用的微处理器(最多两个)。用户还可便捷地选择所需的外设集与设计拓扑。BSB 随后可自动生成包括软硬件平台的可平稳运行的完整嵌入式系统,这些平台可通过 XPS 轻松实施。该工具随后将自动实施。较早版本的 BSB 一次只允许用户实施单个处理器及其外设。而现在,ISE 设计套件 11.1 软件中的新版 BSB 使用户既可实施单处理器设计方案,也可实施双处理器方案,而且配合了相关的外设。 BSB 还可提供进一步功能,使用户在几个窗口中通过一系列鼠标点击指定要使用的开发板。随后用户可在设计方案中选择实施单个处理器或双处理器。他们可指定是否需要处理器使用 FPU,并明确目标处理器、总线性能以及每个处理器的存储器分配/要求(有时需要额外的 FPGA 资源)。用户随后可根据自己的意愿选择添加至每个处理器的 MPU 外设,并指定是否需要给定的外设专用于单处理器或由双处理器共享。用户指定完所有特性后,就可在 XPS 中根据需要查看、放大与实施设计方案。XPS 可精细控制连接,也就是说可获得设计方案的各种视图,其中包括方框图以及系统组装视图。XPS 使用户能够进行详细的分析,并手动调节设计方案中的各个块。用户对设计方案满意后,就可使 XPS 自动实施设计(XPS 将自动在后台运行 ISE 工具)。此外,XPS 还可自动为设计方案的所有硬件组件提供必需的驱动程序。 Platform Studio 的一个全新的特性有助于用户在 SDK 的 XML 文件中导出设计方案。XML 文件包含设计方案中硬件、存储器映射以及外设的描述信息,同时还包括所有硬件外设的数据表单。 用户导入 XML 文件至 SDK 后,就可在业界标准的 Eclipse 软件开发环境下打开设计方案(不是以硬件设计为中心的 GUI),大多数软件开发人员对这种环境都很熟悉,也是他们目前开发应用软件所常用的环境。 使用 SDK,用户还可通过下拉菜单定义所要使用的操作系统。随后该工具便可编辑操作系统,以及适用于设计硬件外设的驱动程序。用户可在工具中启动软件项目,创建软件应用,执行软件调试,建立描述,并向处理器下载应用代码。此外,SDK 还提供了一系列测试应用,其中包括Dhrystone、数种存储器与外设测试,以及 Xilkernel 演示调度程序。 增强的 Platform Studio 版本可实现版本的修订历史跟踪功能,为设计人员提供了渐进性更改设计方案的功能,并确保设计人员能根据需要返回到以前的版本。 DSP 版 新的 DSP 版包括赛灵思逻辑版以及赛灵思 DSP捆绑包(System Generator 开发环境和AccelDSP 综合工具)。参见图 3。  图 3:DSP 版 DSP 版主要以算法开发人员为目标受众,可帮助他们在赛灵思 FPGA 中实施复杂的算法。由于工作流程高度自动化,因此用户无需熟悉 HDL。 在流程中,算法开发人员首先在 The MathWorks 推出的 MATLAB? 软件环境中创建算法和算法的行为模型,然后再在 MathWorks’ Simulink? 产品中测试行为模型,在 MATLAB 和 Simulink 软件之间迭代调试算法,直到算法行为达到预期为止。随后,用户则能用赛灵思 DSP 版来优化和实施赛灵思 FPGA 算法。 算法开发人员可在 DSP 版中用 System Generator 来取代构成所有、大部分或部分算法的行为模块。这些模块包含了赛灵思 CORE Generator 库中的优化 IP,也就是说用户也能通过定制黑盒子用自己的HDL来取代所有或部分模块。如果用户在MATLAB软件中创建了定制算法但没有算法的 VHDL 表达,那么算法开发人员可用 AccelDSP 综合工具自动将定制算法综合到 VHDL 中,并创建新的 System Generator 模块。该模块可用 System Generator设计中的其他模块来替代。System Generator 中的所有算法模块被填充后,用户按下按钮,System Generator 就能自动运行 ISE 软件的放置和布线工具,让工具自己去实施 FPGA 算法表达。这样,算法开发人员只需几分钟就能在赛灵思 FPGA中实施算法,并了解算法在真实硬件上的工作情况。 DSP 版可链接至 Simulink 软件,这使算法开发人员能够在 Simulink 和 MATLAB 环境中重复使用已开发的测试基准来测试其算法,从而确保硬件算法和软件算法的版本行为一致。此外,算法开发人员还能结合使用 DSP 版及 Simulink 和 MATLAB 软件来执行协同仿真任务,同时还能对算法进行故障排除和修改,以实现最佳的性能与功能。例如,如果算法开发人员在开发过程中发现众多行为模块之一需要调整,则可在 FPGA 中运行已知状态良好的模块,以便通过对故障模块的反复调节测试迭代来加速验证工作。硬件协同仿真的运行速度比纯软件仿真加快了 1,000 倍;而且算法越复杂,硬件仿真相对于软件仿真的加速就越明显。 在 ISE 设计套件 11.1 软件中,System Generator 工具可运行在 Linux 与 Microsoft Windows 上。 系统版 系统版提供了赛灵思产品旗下的所有工具,适用于赛灵思器件的各类开发人员和开发团队。嵌入式版包含逻辑版加 EDK,DSP 版包含逻辑版和赛灵思 DSP Bundle,而系统版则包括逻辑版加 EDK 再加上赛灵思 DSP Bundle。 系统版流程中的所有工具均包括以上所述的全部 ISE 设计套件 11.1 软件更新,并提高了逻辑、嵌入式以及 DSP 工具流程之间的互操作性。 WebPACK工具 除了推出 ISE 设计套件 11.1 软件的不同新配置版本外,赛灵思还更新了可供免费下载的ISE WebPACK 工具。在 ISE WebPACK 的 10.1 版本中提供了 PlanAhead 的限制版,而 ISE 11.1 WebPACK 工具则包括 PlanAhead(参见逻辑版章节的相关介绍)完整版的所有实用工具,但仅支持有限数量的器件。 独立工具 赛灵思目前正为客户提供能够充分满足其各种需求的 ISE 软件的各种新型配置版本。一些客户可能希望在现有流程版本的基础上再额外购买某些工具的许可证,因而除了推出逻辑版、嵌入式版、DSP 版以及系统版的配置版本之外,客户还能将 SDK、ChipScope Pro 分析器、EDK 工具及赛灵思 DSP Tools Bundle(包括 System Generator 加 AccelDSP 综合工具)作为独立工具单独购买其许可证。 SDK 版本只包括嵌入式软件工具,主要面向开展嵌入式应用开发、建模和调试的设计团队成员。希望针对其设计进行一些嵌入式软件开发的 DSP 版客户也会发现 SDK 非常实用,并能够充分发挥 ISE 设计套件 11.1 软件将 System Generator 和 SDK 相集成的显著优势。作为独立工具的SDK不包括任何FPGA逻辑实施或仿真工具,因此对硬盘占用很少。 例如,如果用户希望向其设计流程添加嵌入式应用开发功能,那么他们可将 EDK 作为独立工具购买。同样,如果他们希望向设计流程添加 DSP 算法开发,也可单独购买赛灵思 DSP Tools Bundle 的许可证。 ISE 设计套件 的许可证 赛灵思推出的 ISE 11.1 设计套件 拥有全新的工具许可管理方案。在本版本产品发布之前,赛灵思工具的许可管理主要采取基于用户的方式,即每名用户都需要一个许可证才能使用工具,任何工具都不提供流动许可证。 从 ISE 设计套件 11.1 软件开始,赛灵思将以两种配置方式提供工具:节点锁定式,即在单台计算机上锁定许可证;以及流动式,即许可证驻留于客户的网络服务器上。节点锁定式使客户能够将任何赛灵思工具的许可证下载到特定的工作站。多个用户能够共享使用运行在该工作站上的赛灵思软件。流动许可证使用户能将单个许可证下载到其服务器上,以使设计人员无论位于全球任何位置都能同时使用该许可证。赛灵思也以节点锁定和流动配置方式提供独立工具的许可证。请参见表 1。 表 1:新工具流程配置的特性  结论 为了更好地适应客户不同技能水平的需要,帮助客户用赛灵思 FPGA 目标设计平台开展技术创新,赛灵思在精炼设计方法方面迈出了一大步。ISE 设计套件 11.1 软件可提供四种最新的工具流程配置,能够充分满足逻辑设计人员、嵌入式系统开发人员、DSP 算法开发人员以及系统集成商的各种需求。 |

网友评论