ModelSim和QuestaSim功能简介及应用

发布时间:2010-10-17 11:39

发布者:techshare

|

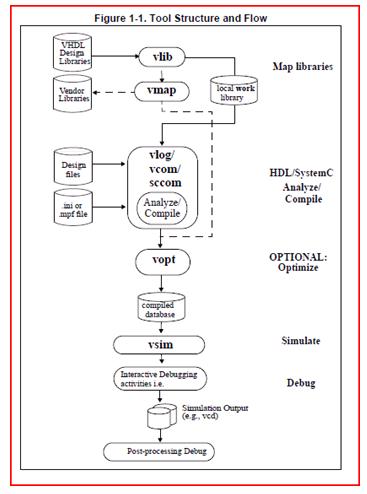

ModelSim是工业界最优秀的语言仿真器,它提供最友好的调试环境,是作FPGA、ASIC设计的RTL级和门级电路仿真的首选。它支持PC和UNIX、LINUX平台,是单一内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真,编译仿真速度业界最快,编译的代码与平台无关,便于保护IP核,具有个性化的图形界面和用户接口,为用户加快调试提供强有力的手段。全面支持VHDL和Verilog语言的IEEE 标准,以及IEEE VITAL 1076.4-95 标准,支持C语言功能调用, C的模型,基于SWIFT的SmartModel逻辑模型和硬件模型。 ModelSim支持RTL仿真,门级仿真,时序仿真:  主要特点:

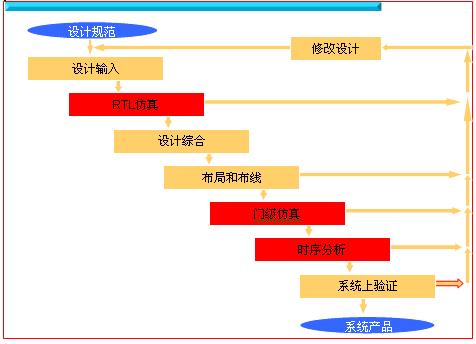

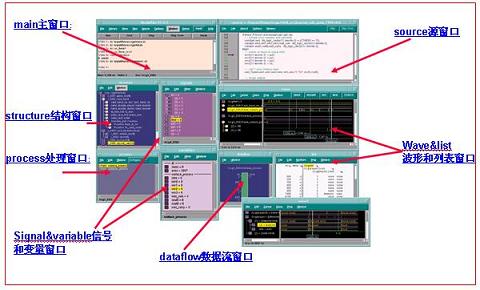

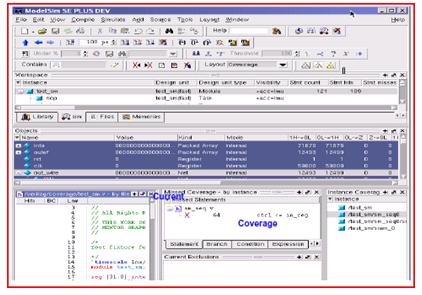

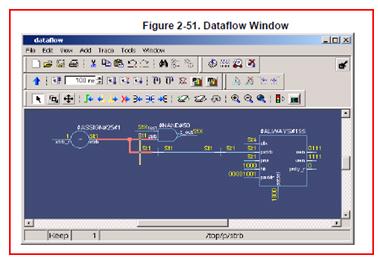

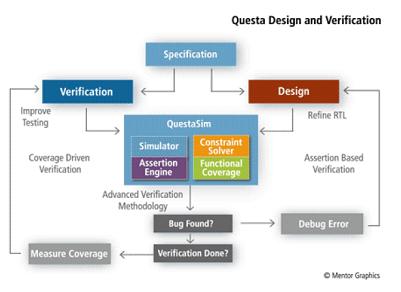

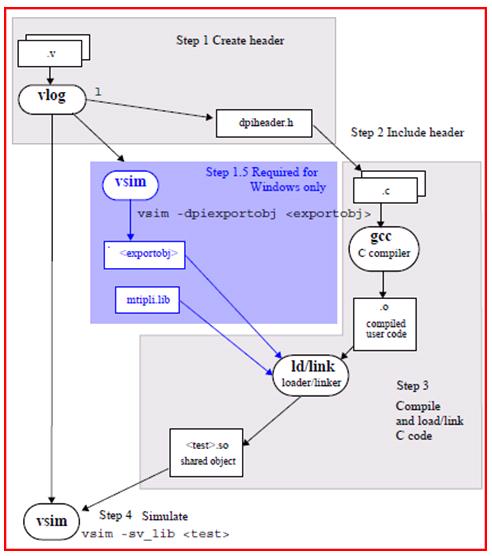

ModelSim用户界面:  ModelSim设计流程:  ModelSim coverage验证:  ModelSim Dataflow窗口:  QuestaSim是第一个基于标准的单核验证引擎,集成了一个HDL模拟器,一个约束求解器,一个判断引擎,功能覆盖,以及一个通用的用户界面。 主要特点: 内建单内核仿真器支持SystemVerilog、verilog、VHDL、PSL以及SystemC。 内建约束解释器支持Constrained-random激励生成,以实现Testbench-Automation; 支持基于PSL,SystemVerilog语言断言的功能验证,支持业界最著名的0-in Checkware 断言库功能验证集成化支持功能覆盖率检查与分析高性能的RTL和Gate-level仿真速度 支持用SystemVerilog和SystemC实现高层次testbench设计与调试高性能集成化的混合语言调试环境加速对混合验证语言;(SystemVerilog,SystemC,PSL,VHDL,Verilog)的交叉调试与分析基于标准的解决方案能支持所有的流程,便于保护验证上的投资 提供最高性价比的功能验证解决方案  Questa AFV提供真正的混合语言验证 Questa AFV是以混合语言流程 (mixed language flow) 为目标的单核心验证解决方案,它同时支持SystemVerilog、VHDL、PSL和SystemC,使设计人员能够选择最合适的语言。 除此之外,与SystemVerilog验证能力的紧密连结,并将其用于受限随机(constrainedrandom)测试平台的产生以及功能覆盖率的验证也对VHDL使用者大有好处。 QuestaSim用户界面与ModelSim类似,命令也完全兼容。 QuestaSim Coverage检查:  QuestaSim DPI Use Flow:  |

网友评论