ЛљгкFPGAЕФ3G/HD/SD-SDIаХКХЙтЯЫДЋЪфЯЕЭГЕФЩшМЦ

ЗЂВМЪБМфЃК2015-12-4 11:14

ЗЂВМепЃКdesignapp

|

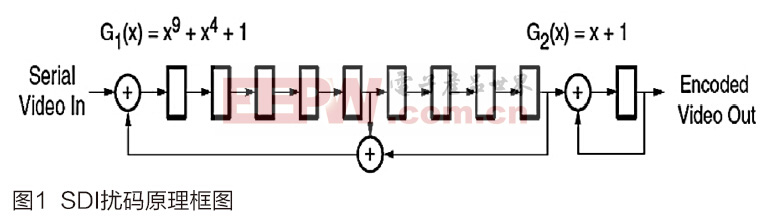

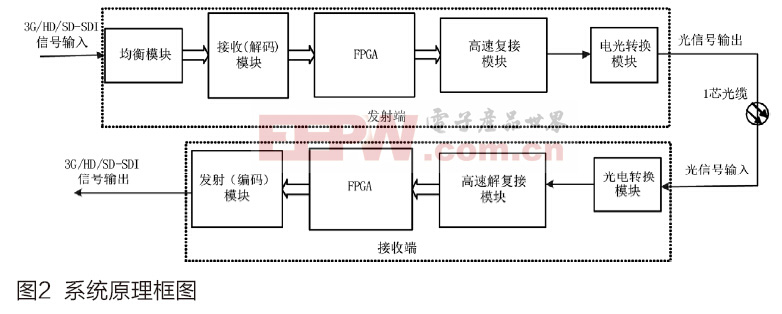

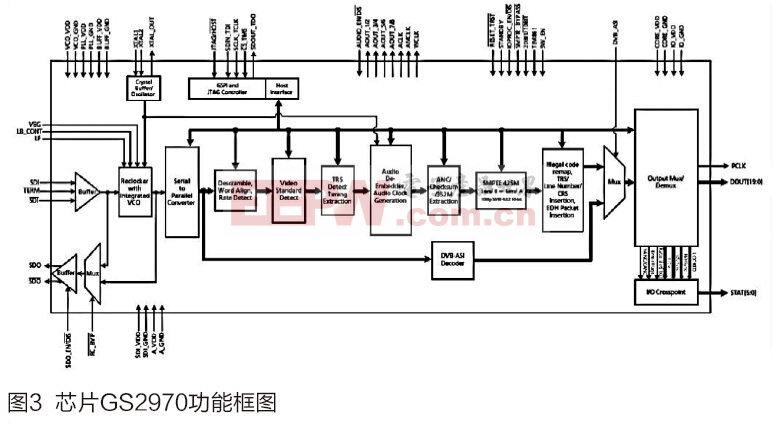

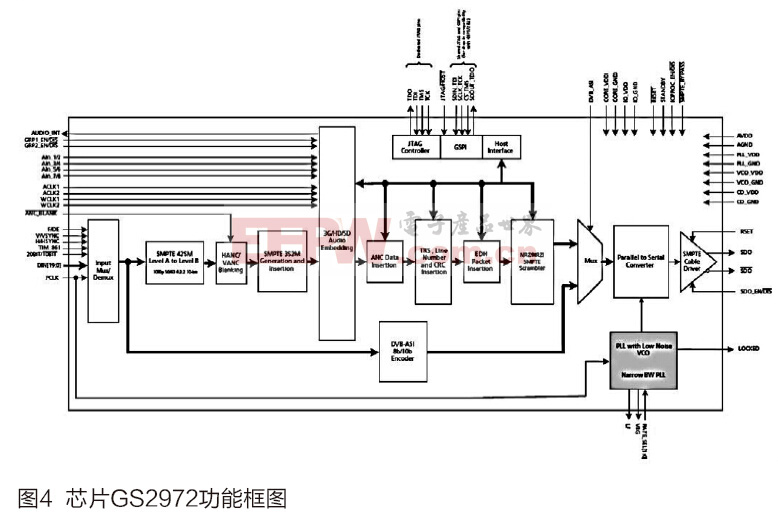

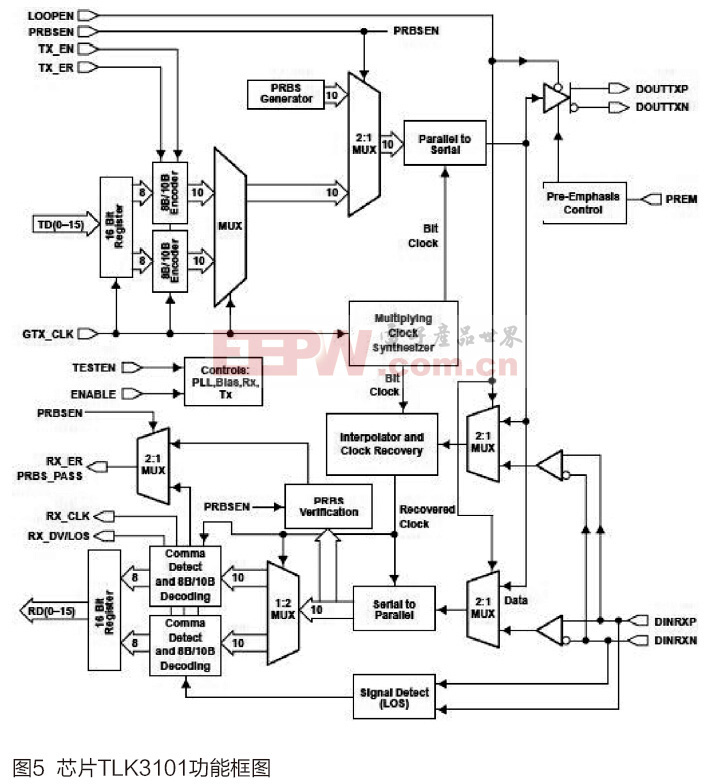

еЊвЊЃКНщЩмСЫЛљгкFPGAКЭИпЫйДЎааИДНг/НтИДНгММЪѕЃЌНЋ3G/HD/SD-SDIаХКХЭЈЙ§ЙтЯЫЪЕЯжЮоЫ№ГЄОрРыДЋЪфЕФЗНЗЈЁЃгыДЋЭГЕФДЋЪфЗНАИЯрБШЃЌДЫЗНАИПЩвдЭъГЩДЋЪфИпЧхЪгЦЕЕФЦНЛЌЩ§МЖЃЌВЂЯђЯТМцШнЯжгаЕФЪгЦЕДЋЪфЭјТчЃЌНЕЕЭСЫЭјТчЕФИФдьЩ§МЖГЩБОЁЃ в§бд SDI(Serial Digital Interface)ЪЧвЛжжЁАЪ§зжЗжСПДЎааНгПкЁБЃЌЭЈЙ§75ІИЭЌжсЯпРТДЋЪфЮобЙЫѕЕФЪ§зжЪгЦЕаХКХЁЃгЩгкДЎааЪ§зжаХКХЕФЪ§ОнТЪКмИпЃЌдкДЋЫЭЧАБиаыОЙ§ДІРэЁЃгУШХТыЕФВЛЙщСуЕЙжУ(NRZI)РДДњЬцдчЦкЕФЗжзщБрТыЃЌЦфБъзМЮЊSMPTE 259MКЭEBU-Tech-3267ЃЌБъзМАќРЈСЫКЌЪ§зжвєЦЕдкФкЕФЪ§зжИДКЯКЭЪ§зжЗжСПаХКХЃЌжЇГж4жжЫйТЪЃК143Mbit/sЕФNTSCжЦИДКЯБрТыаХКХ;177.3Mbit/sЕФPALжЦИДКЯБрТыаХКХ;270Mbit/sЕФNTSCжЦКЭPALжЦЗжСПБрТыаХКХ;360Mbit/s 16ЃК9ГЄПэБШЕФNTSCжЦКЭPALжЦЗжСПБрТыаХКХЃЌЦфжазюГЃМћЕФЪЧ270Mbit/sЁЃдкДЋЫЭЧАЃЌЖддЪМЪ§ОнСїНјааШХЦЕВЂБфЛЛЮЊNRZIТыЃЌШЗБЃдкНгЪеЖЫПЩППЕиЛжИДдЪМЪ§ОнЁЃ дкИХФюЩЯПЩвдНЋЪ§зжДЎааНгПкРэНтЮЊвЛжжЛљДјаХКХЕїжЦЁЃSDIНгПкФмЭЈЙ§270Mbit/sЕФДЎааЪ§зжЗжСПаХКХЃЌЖдгк16ЃК9ИёЪНЕФЭМЯёЃЌгІФмДЋЫЭ360Mbit/sЕФаХКХЁЃNRZIТыЪЧМЋадУєИаТыЁЃгУЁА1ЁБКЭЁА0ЁББэЪОЕчЦНЕФИпКЭЕЭЃЌШчЙћГіЯжГЄЪБМфЕФСЌајЁА1ЁБЛђСЌајЁА0ЁБЃЌЛсгАЯьНгЪеЖЫДгЪ§зжаХКХжаЬсШЁЪБжгЁЃвђЮЊДЎааЪ§зжаХКХНгПкВЛЕЅЖРДЋЫЭЪБжгаХКХЃЌНгЪеЖЫашДгЪ§зжаХКХСїжаЬсШЁЪБжгаХКХЃЌЫљвдвЊВЩгУвдЁА1ЁБКЭЁА0ЁБРДБэЪОгаЮоЕчЦНБфЛЛЕФNRZIТыЁЃдкНгЪеNRZIТыСїЪБЃЌжЛвЊМьГіЕчЦНБфЛЛЃЌОЭПЩЛжИДЪ§ОнЃЌдйОЙ§МгШХЃЌСЌЁА1ЁБЕФЛњЛсМѕЩйЃЌвВОЭЪЙИпЦЕЗжСПНјвЛВНМѕЩйЃЌЪЙНтТыКЭЬсШЁЪБжгаХЯЂИќМгШнвзЁЃЪЕЯжМгШХ/НтШХЕФЩњГЩЖрЯюЪНЮЊG1(x)=x9+x4+1ЃЌИУВНжївЊЪЧНЋЪ§зжЛЏЕФЪгЦЕаХКХБфГЩNRZШХТыаХКХЁЃБрТы/выТыЕФЩњГЩЖрЯюЪНЮЊG2(x)=x+1ЃЌИУВНжївЊЪЧНЋЩЯвЛВНЩњГЩЕФNRZШХТыБфГЩЖдЕчЦНМЋадВЛУєИаЁЂжЛЖдЕчЦНМЋадБфЛЛУєИаЕФNRZIТыЁЃЦфШХТыЕФдРэПђЭМШчЭМ1ЫљЪОЁЃОпЬхЪЕЯжРћгУVerilog HDLБрГЬЁЃдкНгЪеЖЫЃЌгЩSDIНтТыФЃПщДгNRZIТыСїЛжИДГідЪ§ОнСїЁЃ  АДеевЦЖЏЭМЯёКЭЕчЪгЙЄГЬЪІаЛс(SMPTE)жЦЖЈЕФЧхЮњЖШБъзМвЊЧѓЃЌSDIПЩЗжЮЊЃКSD-SDIЁЂHD-SDIКЭ3G-SDIЁЃЦфжаЃК SD-SDIЃКSD-SDI(Standard Definition Seria Digital Interface) ЪгЦЕаХКХЕФЭЈГЃЫйТЪЮЊ270Mbit/sЁЃЦфаХКХИёЪНДг19.4Mbit/sЕН360Mbit/sЃЌжЇГжЗћКЯSMPTE 259MЁЂSMPTE 297MЁЂSMPTE 305MЁЂSMPTE 310MБъзМЃЌвдМАDVB-ASI(EN50083-9)ЕШЪ§зжЕчЪгИёЪНЕФаХКХЁЃSD-SDIЪЧЮобгЪБЁЂЮоЪЇецЕФБъЧхЪгЦЕаХКХЁЃ HD-SDIЃКHD-SDI(High Definition Seria Digital Interface)ЪгЦЕаХКХЕФЫйТЪДяЕН1.485Gbit/sЃЌЫЂаТТЪжЇГж60HzЁЃЦфаХКХИёЪНДг19.4Mbit/sЕН1.485Gbit/sЃЌжЇГжЗћКЯSMPTE 292MЁЂSMPTE 259MЁЂSMPTE 297MЁЂSMPTE 305MЁЂSMPTE 310MБъзМЃЌвдМАDVB-ASI(EN50083-9)ЕШЪ§зжЕчЪгИёЪНЕФаХКХЁЃHD-SDIЪЧЮобгЪБЁЂЮоЪЇецЕФИпЧыЪгЦЕаХКХЁЃ 3G-SDIЃК3G-SDIжаЕФ3GЪЧжИSDIаХКХЕФЪ§ОнДЋЪфТЪдМЮЊ3Gbit/sЁЃЦфаХКХИёЪНДг19.4Mbit/sЕН2.97Gbit/sЃЌжЇГжЗћКЯSMPTE 424MЁЂSMPTE 292MЁЂSMPTE 259MЁЂSMPTE 297MЁЂSMPTE 305MЁЂSMPTE 310MБъзМЃЌвдМАDVB-ASI(EN50083-9)ЕШЪ§зжЕчЪгИёЪНЕФаХКХЁЃгЩгкHDTVПЩвджЇГжУПУы30жЁЕФж№ааЩЈУш1920ЁС1080ЕФЗжБцТЪИёЪНЃЌЖј3GФмЙЛжЇГжБШHDЪгЦЕаХКХзюИпжЁЩЈУшЦЕТЪИпвЛБЖЕФЦЕТЪЃЌМД3GПЩвджЇГжУПУы60жЁЕФHDаХКХЃЌетдкЙлПДЖЏЬЌЪгЦЕЪБЕФВюБ№ЪЧКмДѓЕФЁЃ БОЮФЩшМЦЕФ3G/HD/SD-SDIаХКХЕФЙтЯЫДЋЪфЗНАИЃЌжЇГжБъЧхSD-SDI(270Mbit/s)ЁЂИпЧхHD-SDI(1.485Gbit/s)МАШЋИпЧх3G-SDI(2.97Gbit/s)ЪгЦЕИёЪНЃЌПЩДЋЫЭЗћКЯЪ§зжЪгЦЕЙуВЅ/вьВНДЎааНгПк(DVB-ASI)ЁЂБъзМЧхЮњЖШ(SMPTE 259M)ЁЂИпЧхЮњЖШ(SMPTE 292M)вдМАШЋаТЕФ3G-SDI(SMPTE 424M)ЕШБъзМЕФЪгЦЕЪ§ОнЃЌЭЈЙ§ЙтЯЫЪЕЯж3G/HD/SD-SDIаХКХЕФИпПЩППЁЂИпадФмКЭГЄОрРыДЋЪфЁЃВЩгУЕЅФЃЙтЯЫЃЌЮожаМЬДЋЪфОрРыПЩДя100kmвдЩЯЁЃ 1 ЯЕЭГЩшМЦ гЩгкДЋЪфЕФ3G/HD/SD-SDI аХКХжївЊгУгкЙуВЅЕчЪгаавЕЃЌЦфзЈвЕМЖЕФжИБъвЊЧѓЃЌБиаыШЗБЃЪфГіаХКХгаИпЮШЖЈадгыПЩППадЁЃдкЖдаХКХНјааОљКтвдМАЪБжгЛжИДЃЌНтШХМАДЎВЂзЊЛЛЃЌвдМАКѓЖЫЕФЪфГіЧ§ЖЏЕФДІРэЙ§ГЬжаЃЌОљбЁдёGENNUMЙЋЫОЕФМЏГЩЕчТЗЪЕЯжИпЧхЪгЦЕаХКХНгПкЕФзЊЛЛЃЌетбљзіПЩвдзюДѓЯоЖШЕФБЃжЄИїЯрЙиФЃПщЕФМцШнадЃЌВЂЧвОпгааХКХЛжИДКЭЖЖЖЏвжжЦЙІФмЃЌЯЕЭГЪфГіНгНќЭъУРЕФблЭМжИБъЃЌгаРћгкЬсИпЯЕЭГЕФЮШЖЈадЃЌНЕЕЭаХКХЕФЖЖЖЏЁЃ БОЯЕЭГЕФжїПиФЃПщЪЧFPGAЃЌзлКЯПМТЧГЩБОЁЂеМгУУцЛ§вдМАвдКѓЕФЩ§МЖЃЌОЭашвЊFPGAЕФФкВПзЪдДОЁСПЗсИЛЃЌвђДЫбЁгУXilinxЙЋЫОSpartan-3AЯЕСаFPGAЃЌИУЯЕСаFPGAМЏГЩСЫDSPЙІФмЃЌгЕгаМЋЧПЕФВЂааДІРэФмСІЃЌТњзуЭМЯёКЭЪгЦЕДІРэЫљашЕФадФмвЊЧѓЃЌАќРЈбЙЫѕ(MPEG-2КЭMPEG-4)ЃЌЩЋПеМфзЊЛЛЃЌЭМЯёдіЧПЁЂДІРэЁЂЫѕЗХКЭЪЖБ№ЕШ;ВЩгУSPI PROMФЃЪНЭъГЩХфжУЃЌЮЊБугкЕїЪдЃЌвВдЄСєСЫJTAGНгПк; ЭъГЩЭМЯёВЩМЏЁЂДцДЂКЭећИіЯЕЭГЕФТпМПижЦЁЃ ЯЕЭГЗжЮЊЗЂЩфЖЫКЭНгЪеЖЫЁЃдкЗЂЩфЖЫЃЌаХКХЯШОЙ§ОљКтЁЂДЎВЂзЊЛЛДІРэЃЌЪфШыЕНFPGAЭъГЩвЛДЮИДгУКѓЃЌНјШыИпЫйИДНгаОЦЌЭъГЩЖўДЮИДгУЃЌзюКѓОЕчЙтзЊЛЛФЃПщНЋЦфзЊЛЛЮЊЙтаХКХЃЌетбљОЭНЋ3G/HD/SD-SDIаХКХзЊБфГЩЙтаХКХЁЃдкНгЪеЖЫЃЌНЋНгЪеЕНЕФЕФЙтаХКХОЙтЕчзЊЛЛФЃПщзЊЛЛЮЊЕчаХКХЃЌНјШыИпЫйНтИДНгФЃПщКЭFPGAжаЃЌЭъГЩаХКХНтИДгУКЭЛКДцДІРэКѓЃЌЪфШыЕНЖрЫйТЪSDIБрТыФЃПщЃЌЪфГід3G/HD/SD-SDIаХКХЁЃЯЕЭГдРэПђЭМШчЭМ2ЫљЪОЁЃ  1.1 ЗЂЩфЖЫ НЋДгЭЌжсЕчРТЪфШыЕФ3G/HD/SD-SDIаХКХЭЈЙ§SDIОљКтФЃПщЭъГЩаХКХздЖЏОљКтЃЌаХКХОЙ§ГЄОрРыЕФДЋЪфКѓдкЯпРТжаЛсВњЩњЫ№КФЃЌОЙ§ОљКтКѓЃЌаХКХжЪСПЕУЕНУїЯдЕФИФЩЦЁЃдкФЃПщЪфШыв§НХДІСЌНг75ІИЖдЕиЕчзшНјаазшПЙЦЅХфЁЃОљКтФЃПщЖдЪфШыаХКХДІРэКѓВњЩњвЛЖдВюЗжЪфГіаХКХЃЌдйдкСНЬѕВюЗжЯпжЎМфДЎНг100ІИЕчзшЦНКтЯпМфзшПЙЃЌНЋДЫВюЗжаХКХЪфШыЕНЖрЫйТЪSDIНгЪеФЃПщНјааЪБжгЛжИДКЭ8B/10BНтТыДІРэЃЌОДЎ/ВЂзЊЛЛКѓВњЩњЗћКЯSMPTE 424M/292M/259MБъзМЕФ20/10bitЕФВЂааЪ§ОнЃЌНЋДЫЪ§ОнЫЭШыЕНFPGAжаЁЃЪ§ОнЯШЛКДцдкFPGAФкВПFIFOжаЃЌдкЭъГЩЖдЪ§ОнЕФЕквЛДЮИДгУКѓЃЌИДгУЮЊ10bitЕФВЂааЪ§ОнЃЌЪфГіИјИпЫйИДНгФЃПщЃЌНЋFPGAЪфГіЕФЕЭЫйВЂаааХКХИДНгЮЊИпЫйДЎаааХКХЃЌдйЭЈЙ§ЕчЙтзЊЛЛФЃПщ(бЁгУЫйТЪЮЊ3.125Gbit/sЃЌжЇГжШШВхАЮЕФSFPЙтЦїМў)зЊЛЛЮЊЙтаХКХДЋЪфЕННгЪеЖЫЁЃ 1.2 НгЪеЖЫ ЪзЯШНЋДгЙтРТЕУЕНЕФЙтаХКХЭЈЙ§ЙтЕчзЊЛЛФЃПщзЊЛЛГЩЕчаХКХЃЌНЋДЫЕчаХКХЫЭИјИпЫйНтИДНгФЃПщЃЌНЋИпЫйДЎаааХКХНјааДЎВЂзЊЛЛДІРэЃЌНЋзЊЛЛКѓЕФВЂааЪ§ОнЪфШыЕНFPGAЃЌгЩFPGAЯШЛКДцдкФкВПFIFOжаЃЌ дйНтИДгУГіЗћКЯSMPTE 424M/292M/259MБъзМЕФ20/10bitЕФВЂааЪ§ОнЃЌШЛКѓНЋДЫВЂааЪ§ОнЗЂЫЭИјЖрЫйТЪSDIБрТыФЃПщЃЌДгВЂааЪ§ОнжаЬсШЁГіЪБжгЃЌзїЮЊВЩбљЪБжгЃЌЖдВЂааЪ§ОнНјааЭЌВНДІРэЃЌЭЌЪБЬсШЁГіЭМЯёЪ§ОнКЭЭМЯёИёЪНаХЯЂЃЌЭъГЩ3G/HD/SD-SDIаХКХЕФ8B/10BБрТыЃЌзюКѓЪфГіЕННгЪеЩшБИЃЌЪЕЯжСЫ3G/HD/SD-SDIаХКХЕФЙтЯЫДЋЪфЁЃ  1.3 гВМўЕчТЗЪЕЯж БОЯЕЭГДЋЪфЕФаХКХЫйТЪДг143Mbit/sЕН2.97Gbit/sЃЌжЇГжЗћКЯSMPTE 424MЁЂSMPTE 292MЁЂSMPTE 259MЁЂSMPTE 297MЁЂSMPTE 305MЁЂSMPTE 310MБъзМвдМАDVB-ASI(EN50083-9)ЕШЪ§зжЕчЪгИёЪНЕФаХКХ,ТњзуЙЄвЕМЖКЭЙуЕчВњЦЗЯрЙиБъзМвЊЧѓЁЃ ЯЕЭГгВМўашвЊЕФжївЊЦїМўАќРЈЖрЫйТЪSDIНгЪеаОЦЌGS2970ЁЂЖрЫйТЪSDIЗЂЩфаОЦЌGS2972ЁЂЖрЫйТЪSDIОљКтаОЦЌGS2974B ЁЂFPGA+DSPаОЦЌXC3SD1800AЁЂИпЫйИДНг/НтИДНгаОЦЌTLK3101ЁЃаОЦЌGS2974BНЋЪфШыЕФ3G/HD/SD-SDIаХКХНјааОљКтДІРэЁЃ аОЦЌGS2970НЋЪфШыЕФSDIДЎаааХКХНтТыЃЌЛжИДГіВЩбљЪБжгЃЌВЂНЋЪфШыЕФДЎааЪ§ОнСїзЊЛЛЮЊВЂааЪ§ОнЁЃаОЦЌФкВПМЏГЩДјбЙПиеёЕДЦїЕФЪБжгЛжИДЕчТЗ(Reclocker)КЭЪБжгЛжИДДЎааЛЗТЗДЉдНЕчРТЧ§ЖЏЦїЃЌПЩвдздЖЏЕїНкЪфГібЙАкТЪЃЌвдЪЪгІЪ§ОнЕФЪфШыЫйЖШЁЃаОЦЌЕФЪфШыЖЖЖЏШнЯодђИпДя0.7UI (ЕЅЮЛаХКХЪБМф)ЃЌвђДЫМДЪЙаХКХЕФблЭМвбЙиБе60%вдЩЯЃЌетПюаОЦЌШдПЩНгЪеаХКХвдМАНЋаХКХНтДЎЁЃаОЦЌОпгааХКХЛЗГіЙІФмЃЌБОЖЫЛЗГіЕФ3G/HD/SD-SDIаХКХЃЌПЩжБНгСЌжСИпЧхЯдЪОДѓЦСФЛЛђSDIМрПиЦїЃЌПЩЙЉЯЕЭГЪЕЪБМьВтSDI аХКХЪфШыЪЧЗёе§ГЃЁЃЦфЙІФмПђЭМШчЭМ3ЫљЪОЁЃ аОЦЌGS2972НЋНгЪеЕНЕФВЂааЪ§ОнзЊЛЛЮЊЮобЙЫѕЕФ3G/HD/SD-SDIаХКХЁЃаОЦЌФкВПМЏГЩЕчРТЧ§ЖЏЦїЁЂДјбЙПиеёЕДЦїЕФЪБжгЛжИДФЃПщКЭИпадФмPLLЫјЯрЛЗФЃПщЃЌВЛдйашвЊЭтжУБОЕиЪБжгМАЖЖЖЏЯћГ§ЕчТЗЃЌгааЇНкдМСЫЕчТЗАхЕФУцЛ§;аОЦЌжЛашФЃФт3.3VЁЂ1.2VМАЪ§зж1.2VЙЉЕчЃЌЧвЙІКФЕЭЃЌжЛга400mW(АќРЈЕчРТЧ§ЖЏ)ЃЌДѓДѓНЕЕЭСЫЯЕЭГГЩБОЁЃЦфЙІФмПђЭМШчЭМ4ЫљЪОЁЃ  FPGAаОЦЌXC3SD1800A жЇГж600Mbit/sЕН3.125Gbit/sЕФаХКХЫйТЪЃЌДгаОЦЌGS2970НтТыЪфГіЕФ150MHzЕФ20ТЗВЂааЪ§Он, ОFPGAаОЦЌвЛМЖИДгУзЊЛЛЮЊ10 ТЗ300MHzЕФВЂааЪ§ОнЃЌЭЌЪБFPGAаОЦЌЖд150MHzЕФЪБжгЦЕТЪаХКХНјааБЖЦЕВњЩњгыдгаЪБжгаХКХЭЌЯрЕФ300MHzЪБжгаХКХЃЌвдЬсЙЉИјааЁЂГЁЭЌВНаХКХЃЌНјЖјЪЙааЁЂГЁЭЌВНаХКХгы10 ТЗВЂааЪ§ОнаХКХЭЌЪБИДгУЁЃ FPGAаОЦЌгыБрТыЦїЛђНтТыЦїжЎМфВЩгУСЫLVDSММЪѕЃЌВЛдйЪЙгУTTLЕчЦНСЌНгЁЃLVDSЕчЦНОпгаЗЧГЃЕЭЕФEMIЗјЩфКЭЙІТЪЫ№КФЃЌВЂЬсЙЉИќИпЕФЪеЗЂЫйТЪ;СэЭтЃЌВЂааЪ§ОнзмЯпвВДг20ЮЛМѕЩйЕН10ЮЛЃЌЪЙЕУPCBАхЭМЩшМЦБфЕУИќШнвзЃЌвВНЕЕЭСЫЖдFPGAЕФЕШМЖвЊЧѓЁЃ аОЦЌTLK3101НЋДгFPGAаОЦЌНгЪеЕНЕФ10ЮЛВЂааЪ§ОнНјаа8B/10BБрТыЃЌИДНгЮЊИпЫйДЎаааХКХКѓЪфГі;ЭЌЪБНЋЪфШыЕФИпЫйДЎаааХКХЯШНјаа8B/10BНтТыКЭЭЈЕРЖдЦыЃЌзЊЛЛГЩ10ЮЛВЂааЪ§ОнЪфГіИјFPGAаОЦЌЁЃОпгааХКХЖЊЪЇ(LOS)МьВтЙІФмЁЃПЩНгЪеЕФВюЗжЪфШыУХЯоЕЭжС200mVЁЃНіаш2.5VЕЅЕчдДЙЉЕчЃЌЧвЙІКФЕЭЃЌдМ450mW(Typical)ЁЃЦфЙІФмПђЭМШчЭМ5ЫљЪОЁЃ  2 ЕчТЗВтЪд ЪЙгУTektronixвЧЦї WFM 7120ЖдЯЕЭГДЋЪфЕФSD-SDIаХКХНјааСЫЪЕМЪВтЪдЃЌВтЪдНсЙћШчЭМ6ЫљЪОЁЃ  гЩВтЪдНсЙћПЩжЊЃЌОЙ§БОЯЕЭГДЋЪфЕФЪгЦЕаХКХЛУцЧхЮњЃЌблЭМжЪСПКУЃЌаХКХЖЖЖЏНіга0.12UIЃЌгХгкSMPTE 259MЙцЖЈЕФ0.2UIЁЃ 3 НсЪјгя ФПЧАЃЌИїЪЁЪаЕчЪгЬЈКЭЙуВЅЭЈаХЭјТчЯЕЭГвВдНРДдНЦШЧаашвЊдкЯжгаЕФЙтЯЫСДТЗжаДЋЫЭИпЧхЪгЦЕаХКХЃЌБОЮФЩшМЦЕФЛљгкFPGAЕФ3G/HD/SD-SDIаХКХЕФЙтЯЫДЋЪфЯЕЭГЃЌВЩгУСЫSDIаХКХЕчИДНгЁЂЗжНгММЪѕЃЌЪЕЯжСЫИпжЪСПЪгЦЕаХКХЕФДЋЪфЧвУЛгаШЮКЮЭМЯёжЪСПЕФЫ№ЪЇЃЌСэЭтFPGAОпгаНЯДѓЕФЩшМЦСщЛюадЃЌЖдЪ§ОнЕФВСГ§ЁЂаоИФЃЌжЛашИќИФДњТыЃЌЮоашИФБфЕчТЗНсЙЙЃЌНЕЕЭСЫЯЕЭГГЩБОЃЌЭЌЪБМђЛЏСЫЯЕЭГЕФИДдгадЃЌЬсИпСЫЯЕЭГЙЄзїЕФЮШЖЈадЁЃ ВЮПМЮФЯзЃК [1]РюбхЕЯ. ЛљгкFPGAЕФHD-SDIБрНтТыММЪѕЕФбаОПгыПЊЗЂ[J]. ЕчзгММЪѕгІгУ 2012 [2]Gennum. GS2970 Receiver Datasheet .2009 [3]Gennum. GS2972 Transmiter Datasheet.2011 [4]Gennum.GS2974B Adaptive Cable Equalizer Datasheet.2009 [5]Texas Instruments. TLK3101 Transceivers Datasheet.2001 [6]Xilinx. XA Spartan-3A DSP Automotive FPGA Family Data Sheet.2011 [7]SMPTE 259M,Television 10bit 4:2:2 Component and 4fsc Composite Digital Signals Serial Interface.1997 [8]SMPTE 292M,Television Bit-Serial Digital Interface For High-Definition Television Systems.1998 [9]SMPTE 424M,Television 3Gb/s Signal/Data Serial Interface. 2006 |

ЭјгбЦРТл