»щУЪPSoC 4өДОЮҙ«ёРЖчBLDCҝШЦЖ

·ўІјКұјдЈә2014-12-25 10:40

·ўІјХЯЈәdesignapp

|

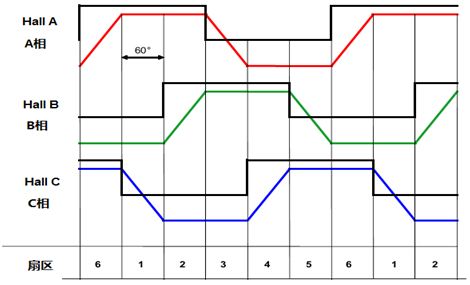

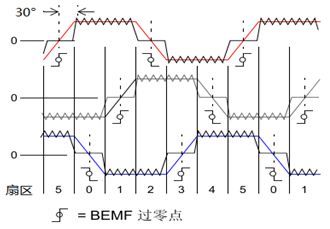

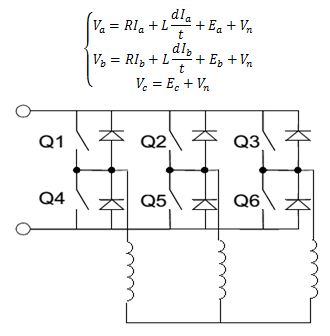

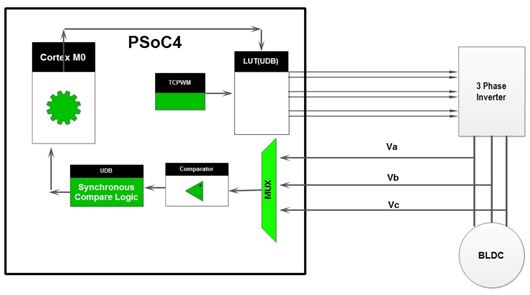

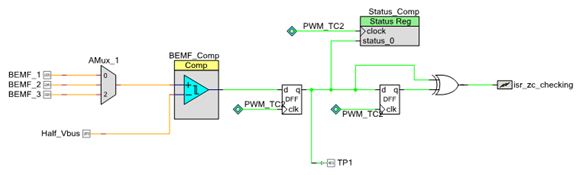

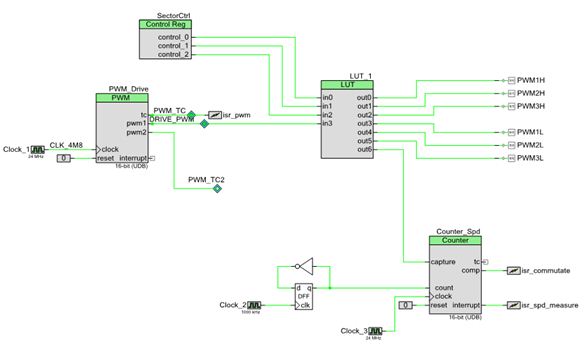

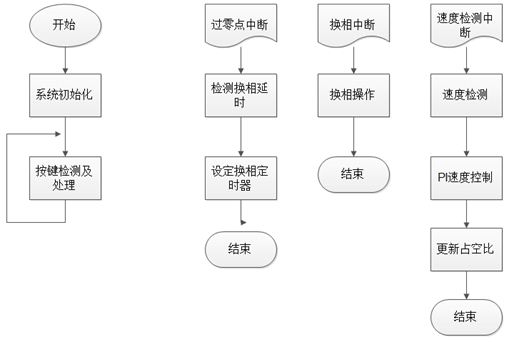

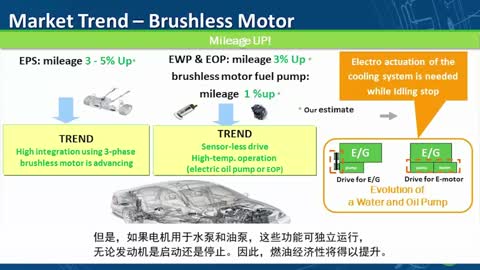

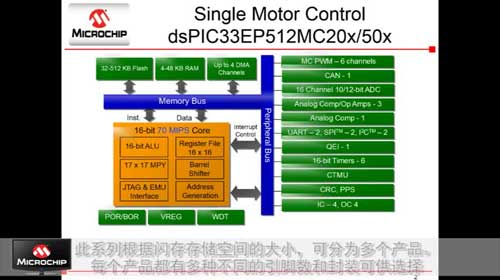

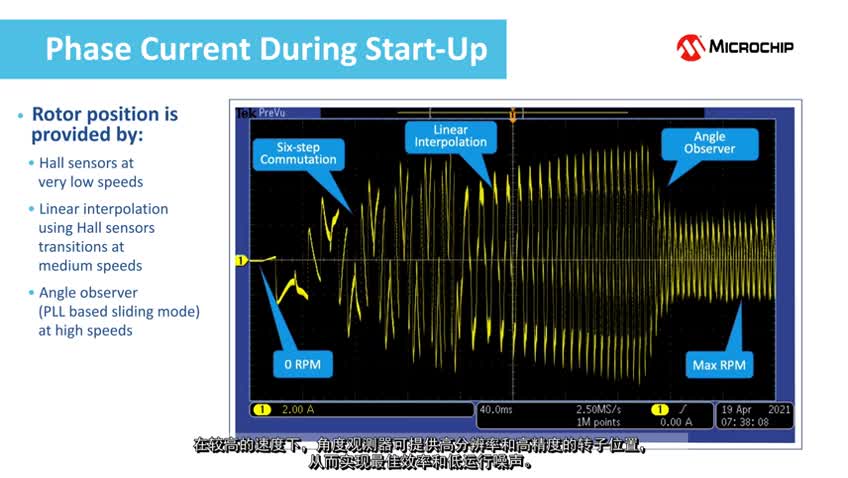

ХӘТӘЈәұҫОДҪйЙЬБЛ»щУЪCypressРВТ»ҙъҝЙұаіМЖ¬ЙППөНіРҫЖ¬PSoC 4өДОЮҙ«ёРЖчBLDCҝШЦЖ·Ҫ°ёЎЈНЁ№эPSoC 4ДЪІҝөДДЈДв¶аВ·СЎФсЖчЈ¬ұИҪПЖчДЈҝйј°ҝЙұаіМКэЧЦВЯјӯДЈҝйЧйіЙөДН¬ІҪұИҪПДЈҝйЈ¬ОЮРиҪиЦъНвІҝРҫЖ¬ұгҝЙКөПЦ·ҙөз¶ҜКЖ№эБгөгјмІвЈ»PSoC 4ДЪІҝјҜіЙөДҝЙұаіМUDBҝЙҪ«»»ПаВЯјӯТФPLDөДРОКҪ№М»ҜФЪРҫЖ¬ЦРЈ¬КөПЦҝмЛЩҝЙҝҝөДУІјю»»ПаЎЈ Abstract: This paper introduces the sensorless BLDC solution based on Cypress new product PSoC 4. With integrated analog MUX, comparator and UDB, PSoC4 can realize BEMF zero-crossing point detecting by hardware which can decrease software overhead; PSoC4 can also realize hardware commutation with LUT. Keywords: PSoC 4Ј¬Sensorless, BLDC, Zero-Crossing Point Detecting 1. ТэСФ ОЮЛўЦұБчөз»ъ(BLDC) УГөзҝШЧ°ЦГИЎҙъБЛөзЛўәН»»ПтЖчЈ¬МбёЯБЛөз»ъөДҝЙҝҝРФЈ¬ІўЗТҫЯУРМе»эРЎЎўР§ВКёЯЎўФлТфөНөИУЕөгЈ¬ФЪПы·Сј°№ӨТөУҰУГЦРөГөҪ№г·әУҰУГЎЈФЪBLDCҝШЦЖЦРЈ¬АшҙЕұШРлУлЧӘЧУО»ЦГН¬ІҪЈ¬ТтҙЛіЈУГТ»ёц»т¶аёцЧӘЧУО»ЦГҙ«ёРЖчИ·¶Ёөз»ъЧӘЧУПа¶ФУЪөз»ъ¶ЁЧУөДО»ЦГЎЈІЙУГО»ЦГҙ«ёРЖчөДBLDCҝШЦЖ·Ҫ°ёҪПОӘјтөҘЈ¬ёщҫЭО»ЦГҙ«ёРЖчөДКдіцИ·¶ЁЧӘЧУЛщҙҰөДЗшјдЈ¬ІўПаУҰөД¶Фөз»ъИЖЧйҪшРР»»ПаЎЈИ»¶шЈ¬О»ЦГҙ«ёРЖчөДК№УГ»бҙшАҙТ»Р©ИұөгЈ¬ИзФцјУПөНііЙұҫЈ¬ҪөөНҝЙҝҝРФЈ»Н¬КұФЪТ»Р©МШКвіЎәПЈ¬ИзФЪөз»ъҙҰФЪҪюГ»өД»·ҫіЦРЈ¬ФтОЮ·Ё°ІЧ°ҙ«ёРЖчЎЈХвҫНТӘЗуөз»ъОЮО»ЦГҙ«ёРЖчФЛРРЎЈ 2. ОЮҙ«ёРЖчҝШЦЖ·Ҫ°ё Нј1јҙОӘҙш»ф¶ыҙ«ёРЖчөДBLDC»»ПаНјЎЈ·Ҫ°ёІЙУГіЈ№жөД120ЎгНЁөз·ҪКҪЈЁБщІҪ»»ПаЈ©Ј¬ ОӘК№өз»ъФЛРРЈ¬ұШРл°ҙХХЦЬЖЪРФјдёфЗР»»НЁөзөДПаЈЁјҙ»»ПаЈ©ЎЈ¶ФУЪіЈ№жНЁөзЈ¬ГҝёцөзЦЬЖЪРиТӘБщҙОөИҫа»»ПаЎЈГҝТ»ІҪ»тГҝТ»ЗшјдЈ¬ПаөұУЪ60ёцөзҪЗ¶ИЎЈБщёцЗшјдЧйіЙБЛ360 ёцөзҪЗ¶И»тТ»ҙОөзЖшРэЧӘЎЈГҝТ»ЗшјдЙП¶јУРБҪёцИЖЧйНЁөзЈ¬Т»ёцИЖЧйОҙНЁөзЎЈТӘК№өз»ъХэИ·»»ПаЈ¬ұШРлІвБҝөзЦЬЖЪЦРөДҫш¶ФО»ЦГЎЈІЙУГИэёц»ф¶ыҙ«ёРЖчјҙҝЙМṩБщҙО»»ПаЛщРиТӘөДО»ЦГРЕПўЎЈ  Нј1 BLDC»»ПаНј ФЪОЮҙ«ёРЖчҝШЦЖ·Ҫ°ёЦРЈ¬ұШРлІЙУГЖдЛы·ҪКҪ»сИЎЧӘЧУО»ЦГЎЈЧӘЧУО»ЦГөД»сөГКЗBLDCОЮО»ЦГҙ«ёРЖчҝШЦЖЦРөД№ШјьјјКхЎЈіЈјыөДЧӘЧУО»ЦГјмІвУР·ҙөз¶ҜКЖ№эБгөгјмІв·ЁЎў·ҙөз¶ҜКЖИэҙОРіІЁ»э·ЦјмІв·ЁЎўРшБч¶юј«№ЬјмІв·ЁЎўҙЕБҙ№АјЖ·ЁөИЎЈЖдЦРЧоіЈУГЧоҫӯөдөДКЗ·ҙөз¶ҜКЖ№эБгөгјмІв·ЁЎЈ·ҙөз¶ҜКЖ№эБгөгјмІв·ЁІ»РиТӘПкПёБЛҪвөз»ъМШРФЈ¬ҝЙККУГУЪ¶аЦЦөз»ъЎЈ ФЪБщІҪ»»Па№эіМЦРЈ¬ГҝТ»ЗшјдЙП¶јУРБҪёцИЖЧйНЁөзЈ¬Т»ёцИЖЧйОҙНЁөзЎЈХвСщФЪОҙНЁөзИЖЧйЙП»біцПЦДіПаЙПөзБчОӘБгЈ¬ФЪөз»ъТэПЯЙПИФҝЙҝҙөҪөзС№өДПЦПуЎЈХвёцөзС№ҫНКЗ·ҙөз¶ҜКЖЎЈјтөҘөДЛөЈ¬·ҙөз¶ҜКЖ(EMF)КЗУАҙЕКҪөз»ъЧӘЧУЧӘ¶ҜКұЈ¬УЙ¶ЁЧУИЖЧйЛщІъЙъөДөзС№ЎЈ·ҙөз¶ҜКЖөД·щЦөУлөз»ъЧӘЛЩіЙХэұИЎЈФЪНј1ЦРЈ¬өЪ1ЙИЗшЦРCПаөзС№Ј¬өЪ2ЙИЗшЦРөДBПаөзС№јҙОӘ¶ЁЧУИЖЧйІъЙъөД·ҙөз¶ҜКЖЎЈ јЩЙиөз»ъУЙЎАUV өзС№Зэ¶ҜЈ¬Фт·ҙөз¶ҜКЖРЕәЕТФ0VОӘЦРРД¶ФіЖЎЈИз№ы·ҙөз¶ҜКЖРЕәЕОӘТ»МхЦұПЯЈ¬ДЗГҙРЕәЕҪ«ФЪёГЗшјдөДТ»°лҙҰЈЁТІҫНКЗёГЗшјдөД30ЎгөзҪЗ¶ИҙҰЈ©НЁ№эБгПЯЎЈёГөгіЖОӘ№эБгөгЎЈФЪ№эБгКВјюәуФЩҫӯ№э30ЎгөзҪЗ¶ИҪшРРПВТ»ҙО»»ПаЎЈТтҙЛЈ¬ҫ«И·јмІв№эБгөгКұҝМұгҝЙ№АЛгЧӘЧУО»ЦГЈ¬К№өз»ъИЖЧйФЪХэИ·өДКұјдҪшРР»»ПаЎЈИзНј2ЛщКҫЎЈ  Нј2 BEMF№эБгөгУл»»ПаНј 3. №эБгөгјмІв·Ҫ°ё Нј3ОӘөдРНөДИэПаBLDCЗэ¶ҜөзВ·НШЖЛНјЎЈјЩ¶ЁИэПа¶ЛөзС№·ЦұрОӘVaЈ¬VbЈ¬VcЈ»VnОӘЦРРФөгөзС№Ј»EaЈ¬EbЈ¬EcОӘИэПа·ҙөз¶ҜКЖЈ»Ia,Ib,IcОӘИэПаөзБчЈ¬RОӘПаөзЧиЈ¬LОӘөзёРЎЈФЪCПаОӘ·ЗөјНЁПаКұҝЙ  Нј3 BLDCЗэ¶ҜөзВ·НШЖЛНј ёщҫЭ№эБгөгКұVa+Vb+Vc=0 ј°ЙПКцөИКҪҝЙөГЈә 3Ec=2Vc-(Va+Vb) ёщҫЭТФЙПөИКҪЈ¬УРИэЦЦІ»Н¬өД№эБгөгјмІв·Ҫ·ЁЈә 1.ЦұҪУУГADCІЙСщИэВ·¶ЛөзС№Ј¬ёщҫЭЙПКц№«КҪЕР¶П№эБгөгЎЈҙЛЛг·ЁРиІЙСщ¶аВ·ADCөзС№Ј¬ЗТРиИнјюВЛІЁЛг·ЁЈ¬¶ФADCј°MIPSҫщУРТ»¶ЁөДТӘЗуЎЈ 2.ФЪ PWM КдіцРЕәЕОӘ OFF КұІЙСщ·ЗНЁөзПаөзС№Ј¬Ҫ«Ц®УлБгөзС№ұИҪПЎЈҙЛЛг·ЁФЪөНЛЩКұұИҪПУРУЕКЖЈ¬ТтОӘөНЛЩКұ·ҙөзКЖРЕәЕұИҪПИхЈ¬ХвЦЦЛг·ЁөДІЙСщЗшУтЗЎОӘ·ЗНЁөзПа¶ЛөзС№№эБгЗшУтЎЈө«өұ PWM өДХјҝХұИұИҪПёЯКұЈ¬УЙУЪҝЙ№©ІЙСщөДКұјдөгМ«¶МЈ¬ИЭТЧФміЙІЙСщК§°ЬЎЈ 3.ФЪ PWM КдіцРЕәЕОӘ ON КұІЙСщ·ЗНЁөзПаөзС№Ј¬Ҫ«Ц®УлДёПЯөзС№өДТ»°лұИҪПЎЈҙЛЦЦЛг·ЁФтҫЯУРҪПҝнөДөчЛЩ·¶О§Ј¬ҪПОӘНЁУГЎЈ ұҫ·Ҫ°ёјҙІЙУГөЪИэЦЦЛг·ЁҪшРР№эБгөгјмІвЎЈ 4.»щУЪPSoC 4өДЙијЖ·Ҫ°ё PSoC 4 јтҪй PSoC 4 КЗ»щУЪARM Cortex-M0 CPUөДҝЙұаіМЗ¶ИлКҪПөНіҝШЦЖЖчјТЧеЈ¬ЛьјҜәПБЛҝЙұаіМДЈДвЧКФҙЎўҝЙұаіМДЪІҝ»ҘБӘЎўУГ»§ҝЙұаіМКэЧЦВЯјӯЎўНЁУГөД№М¶Ё№ҰДЬНвЙијЖТФј°ёЯРФДЬөДARM Cortex-M0 CPUЧУПөНіЎЈПа¶ФУЪPSoC3ЎўPSoC5ПөБРІъЖ·өДёчёц·ҪГж, PSoC 4¶јЧцБЛәЬҙуөДёДҪшЎЈPSoC 4ПЦ°ьә¬CY8C4100 әНCYCY8C4200БҪёцІъЖ·ПөБРЈ¬PSoC4100ПөБРКЗ»щУЪARMДЪәЛөДЧоөНіЙұҫөДPSoCЈ¬ЛьҪ«PSoCөДБй»оРФәНёЯјҜіЙ¶ИТэИл¶ФіЙұҫГфёРөДҙуЕъБҝЙъІъөДІъЖ·ЦРЎЈPSoC4200ПөБРУөУРЛЩ¶ИёьҝмөДҙҰАнЖчЈ¬ёьёЯөДADCІЙСщЛЩ¶ИЈ¬ТФј°»щУЪPLDөДФцЗҝРННЁУГКэЧЦДЈҝй(UDB)ЎЈТФПВёЕАЁБЛЖдЦчТӘМШРФЎЈ Ўс ёЯРФДЬ Cortex-M0 CPU ДЪәЛЎЈ»щУЪ48 MHz ARM Cortex-M0 ЦРСлҙҰАнЖч , Ц§іЦөҘЦЬЖЪіЛ·ЁЎЈ Ўс №М¶Ё№ҰДЬТФј°ҝЙЕдЦГөДКэЧЦДЈҝйЎЈ°ьАЁЛДёц¶АБўөДҝЙЦ§іЦЦРСл¶ФЖлөДPWMЈ¬Ц§іЦ»ҘІ№өДҝЙұаіМЛАЗшј°Н¬ІҪADCІЩЧчЈ»БҪёцҝЙ№ӨЧчОӘSPI/UART/I2C ҙ®РРНЁРЕҪУҝЪөДҙ®РРНЁРЕДЈҝйЈЁSCBЈ©Ј» Ўс ёЯРФДЬДЈДвПөНіЎЈ°ьАЁТ»ёцЦ§іЦБгҝӘПъНЁөАЗР»»№ҰДЬөД12О»1 Msps ADC; БҪёцЦ§іЦұИҪПЖчДЈКҪј°SAR ADCКдИл»әіе№ҰДЬөДФЛЛг·ЕҙуЖч; БҪёцөН№ҰәДұИҪПЖчЈ»Т»ёцөзИЭёРУҰЈЁCapSenseЈ©ДЈҝйЈ¬Мṩј«јСөДРЕФлұИәН·АЛ®№ҰДЬЈ»БҪёцөзБчКэДЈЧӘ»»Жч ЈЁIDACЈ©ЎЈ Ўс ёЯ¶ИҝЙұаіМөДКэЧЦВЯјӯЎЈЛДёцҝЙұаіМКэЧЦВЯјӯДЈҝй(UDB)Ј¬Гҝёц°ьә¬БҪёцОўРНөДҝЙұаіМВЯјӯХуБРәНТ»ёц8О»КэҫЭФЛЛгөҘФӘ ЎЈ Ўс Бй»оҝЙұаіМөДДЪІҝ»ҘБ¬ЎЈ »щУЪPSoC4өДОЮҙ«ёРЖчBLDCҝШЦЖ·Ҫ°ё PSoC4 ДЪІҝјҜіЙЛДёц¶АБўөДҝЙЦ§іЦЦРСл¶ФЖлЎў»ҘІ№өДҝЙұаіМЛАЗшј°Н¬ІҪADCІЩЧчөДTCPWMДЈҝйЈ»БҪёцЦ§іЦұИҪПЖчДЈКҪј°SAR ADCКдИл»әіе№ҰДЬөДФЛЛг·ЕҙуЖчЈ»ҝЙНкіЙН¬ІҪұИҪПВЯјӯөДҝЙұаіМКэЧЦВЯјӯДЈҝй(UDB)Ј»ҝЙЧФУЙЗР»»ДЈДвНЁөАөДДЈДв¶аВ·СЎФсЖчЈ»·бё»өДЖ¬ДЪЧКФҙҝЙҪ«ЦчҝШөзВ·ЛщРиРҫЖ¬јҜіЙөҪТ»Ж¬РҫЖ¬ЦРЈ¬КөПЦёЯ¶ИјҜіЙ»ҜЎЈНј4ПФКҫБЛPSoC4 ОЮҙ«ёРЖчBLDCУІјюҝШЦЖҝтНјЎЈ  Нј4 PSoC4 ОЮҙ«ёРЖчBLDCУІјюҝШЦЖҝтНј Па¶ФУЪЖдЛыҪвҫц·Ҫ°ёЈ¬»щУЪPSoC4өДОЮҙ«ёРЖчBLDCҪвҫц·Ҫ°ёҫЯУРТФПВМШөгУЕКЖЈә 1Ј©ІЙУГёЯРФјЫұИөДCortex-M0ДЪәЛЎЈCortex-M0КЗКРіЎЙППЦУРөДЧоРЎЎўЧоҪЪДЬөДARMҙҰАнЖчЈ¬ҙъВлХјУГҝХјдРЎЈ¬ДЬТФ8О»ҙҰАнЖчөДјЫёс»сөГ32О»ҙҰАнЖчөДРФДЬЈ¬ҝЙГчПФҪЪФјПөНііЙұҫЎЈ 2Ј©ДЪІҝјҜіЙБҪёцЦ§іЦұИҪПЖчДЈКҪј°ҝЙұаіМКэЧЦВЯјӯДЈҝй(UDB)Ј¬ЕдәПДЪІҝДЈДв¶аВ·СЎФсЖчҝЙОЮРиНвІҝРҫЖ¬ҝЙУІјюНкіЙ№эБгөгјмІвЈ¬јхЙЩПөНііЙұҫЎЈ 3Ј©ДЪІҝјҜіЙБҪёцөН№ҰәДұИҪПЖчЈ¬ҝЙУГУЪУІјюұЈ»Ө»тҙнОуРЕәЕҙҰАнЎЈКРіЎіЈУГҪвҫц·Ҫ°ёҙуІҝ·ЦІЙУГНвІҝұИҪПЖчНкіЙҙЛ№ҰДЬЎЈІЙУГPSoC4ҝЙҪшТ»ІҪјхЙЩBOMЈ¬ҪөөНіЙұҫЎЈ 4Ј©НЁ№эUDBКөПЦөДLUTұнУІјюКөПЦ»»ПаВЯјӯЈ¬ҪПИнјю·ҪКҪёьјУҝмЛЩҝЙҝҝЎЈ 5Ј©јхЙЩPCBҝХјдј°BOMіЙұҫЎЈУЙУЪPSoC4јҜіЙБЛөз»ъҝШЦЖЛщРиҙуІҝ·ЦНвЙиј°ЖдЛы·бё»өДДЈҝйЈ¬ҝЙКөПЦёЯ¶ИјҜіЙ»ҜөДЙијЖЎЈ 6Ј©Бй»оөДНЁС¶ҪУҝЪЎЈPSoCМШКвөДҝЙұаіМјЬ№№МṩБЛј«ОӘБй»оөДНЁС¶ҪУҝЪЈ¬ҝЙВъЧгёчЦЦУҰУГөДРиЗуЎЈ »щУЪPSoC4өДЙијЖКөАэ 1Ј©ФӯАнНјЙијЖ ёщҫЭНј4өДҝШЦЖҝтНјЈ¬ОТГЗЙијЖБЛНј5ј°Нј6ЛщКҫөДBLDCҝШЦЖФӯАнНјЎЈ ИэПа¶ЛөзС№НЁ№эIOУлДЪІҝДЈДв¶аВ·СЎФсЖчПаБ¬Ј¬ДЈДв¶аВ·СЎФсЖч»бёщҫЭ»»ПаЧҙМ¬¶ҜМ¬өДЗР»»ЛщТӘІЙСщөД·ЗНЁөзПаІўБ¬ҪУЦБЖ¬ДЪұИҪПЖчЎЈЖ¬ДЪөДұИҪПЖчУлДёПЯөзС№өДТ»°лұИҪПЈ¬КдіцРЕәЕБ¬ҪУЦБDҙҘ·ўЖчөДКдИл¶ЛЎЈDҙҘ·ўЖчөДөДКұЦУРЕәЕАҙЧФУЪКэЧЦДЈҝйЦРөДPWMДЈҝйөДКдіцЎЈ ХвСщНЁ№эDҙҘ·ўЖчҝЙ»сөГФЪPWMОӘёЯөзЖҪөДКұҝМ¶ЛөзС№Ул°лДёПЯөзС№өДұИҪПҪб№ыЎЈ¶шұИҪПЖчөД·ӯЧӘКұҝМјҙКЗ·ҙөзКЖ№эБгөгЎЈұИҪПЖчөДКдіц·ӯЧӘКұЈ¬ҝЙТФҙҘ·ўЦР¶ПЈ¬НЁЦӘCPUЧчПаУҰөДҙҰАнЎЈН¬КұЖ¬ЙПөДұИҪПЖч»№ҫЯУРЦН»ШұИҪПөД№ҰДЬЎЈјҙұИҪПЖчКдіцЖчЧФЙП¶шПВ·ӯЧӘУлЧФЙП¶шПВ·ӯЧӘөДөзС№ІўІ»НкИ«Т»ЦВЈ¬¶шКЗУРТ»ёц10mVЧуУТөДЦН»ШөзС№ЎЈҙЛ№ҰДЬҝЙТФұЬГвұИҪПЖчКдіцКЬГ«ҙМУ°Пм¶шұ»ОуҙҘ·ўЎЈ  Нј5 №эБгөгјмІвФӯАнНј ФЪ№эБгөгЦР¶ПЦРЈ¬CPUҝЙЦұҪУНЁ№эҝШЦЖјДҙжЖчҝШЦЖUDB»»ПаВЯјӯұнLUTЦұҪУЗэ¶ҜИэПаИ«ЗЕөзВ·Ј¬НкіЙөз»ъөДУІјю»»ПаЎЈН¬Кұ»»ПаРЕәЕТІН¬ІҪКдИлЦБ¶ЁКұЖчЈ¬НкіЙөз»ъЛЩ¶ИјмІвЎЈ  Нј6 PWMј°»»ПаВЯјӯФӯАнНј 2Ј©іМРтЙијЖ ЦчіМРтКЧПИіхКј»ҜәНЕдЦГPSoC4өДДЪІҝЧКФҙЈ¬ФЪЦчСӯ»·ЦРКЧПИјмІв°ҙјьөДЖфНЈГьБоЈ¬ЦҙРРПаУҰІЩЧчЎЈёщҫЭНј5ј°Нј6ҝЙЦӘЈ¬іМРтЦчТӘУРИэёцЦР¶ПЈә№эБгөгјмІвЦР¶ПЎў»»ПаЦР¶ПЎўЛЩ¶ИјмІвЦР¶ПЎЈФЪ№эБгөгјмІвЦР¶ПЦРЈ¬іМРтЦчТӘНкіЙ»»ПаСУКұөДјЖЛгј°»»Па¶ЁКұЖчөДЙи¶ЁЈ»»»ПаЦР¶ПЦчТӘНкіЙLUTҝШЦЖјДҙжЖчөДІЩЧчНкіЙ»»ПаВЯјӯЈ»ЛЩ¶ИјмІвЦР¶ПЦчТӘНкіЙЛЩ¶ИјмІв»ъPIҝШЦЖЎЈПа№ШБчіМНјИзНј7ЛщКҫЎЈ  Нј7 іМРтБчіМНј КөСйҪб№ы ФЪPSoC Creator»·ҫіПВұаТл№ӨіМЈ¬ІўБ¬ҪУPSoC4ҝӘ·ў°еЈ¬ИэПаИ«ЗЕЗэ¶Ҝ°еУлBLDCөз»ъЈ¬НЁөзәуөз»ъҝЙХэіЈФЛРРЈ¬Нј8ПФКҫБЛөз»ъФЛРРКұөДИэПа·ҙөз¶ҜКЖІЁРОЎЈҝЙТФҝҙіцЈ¬BLDCФЛРРЖҪОИЈ¬·ҙөз¶ҜКЖОӘұкЧјөДМЭРОІЁЎЈ  Нј8 ИэПа·ҙөз¶ҜКЖНј 5. РЎҪб ЙПКцКөАэҪйЙЬБЛИзәОФЪCypressРВТ»ҙъҝЙұаіМЖ¬ЙППөНіРҫЖ¬PSoC 4 ЖҪМЁЙПКөПЦОЮҙ«ёРЖчBLDCҝШЦЖ·Ҫ°ёЎЈPSoC 4ДЪІҝ¶АМШөДДЈДв¶аВ·СЎФсЖчЎўҝЙұаіМКэЧЦВЯјӯДЈҝйЕдәПДЪІҝұИҪПЖчДЈҝйҝЙКөПЦБй»оөДУІјю№эБгөгјмІв·Ҫ°ёЎЈН¬КұPSoC 4ДЪІҝјҜіЙөДҝЙұаіМUDBҝЙҪ«»»ПаВЯјӯТФPLDөДРОКҪ№М»ҜФЪРҫЖ¬ЦРЈ¬КөПЦҝмЛЩҝЙҝҝөДУІјю»»ПаЎЈPSoC 4ЧчОӘCypressЧоРВНЖіцөДІъЖ·Ј¬Хл¶Фөз»ъҝШЦЖЧціцБЛё»УРМШЙ«өДУЕ»ҜЎЈЖҫҪиЖ¬ДЪ·бё»өДЧКФҙј°ёЯ¶ИөДБй»оРФЈ¬УГ»§ҝЙТФЗбЛЙЙијЖіцёЯ¶ИјҜіЙ»ҜЎўөНіЙұҫЎўРФДЬУЕФҪөДөз»ъҝШЦЖ·Ҫ°ёЎЈ ІОҝјОДПЧ [1].PSoC 4: PSoC 4100 Family Datasheet [2].PSoC 4: PSoC 4200 Family Datasheet [3].PSoC 4 Architecture TRM [4].PSoC 4100/4200 Family PSoC 4 Registers TRM (Technical Reference Manual) [5].AN79953 - Getting Started with PSoC 4 |

НшУСЖАВЫ