九峰山实验室新型SiC Trench MOSFET科研级器件样品发布!

|

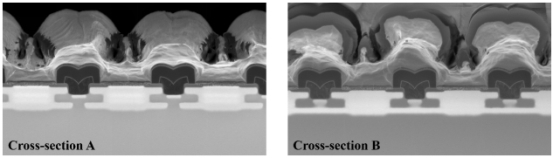

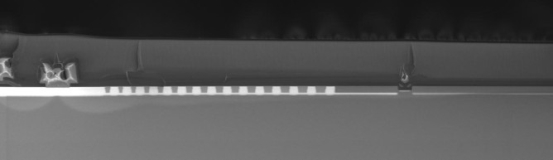

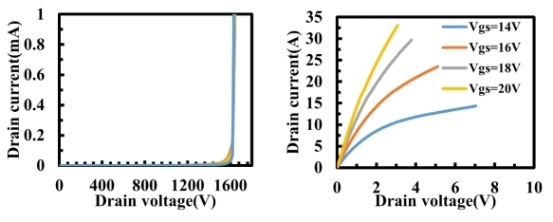

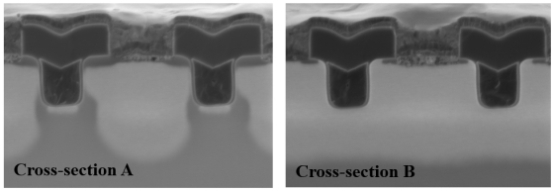

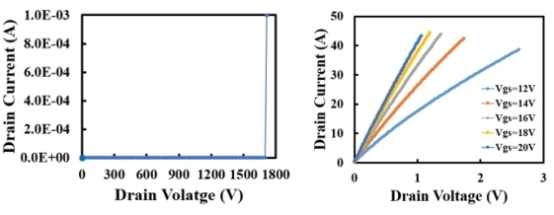

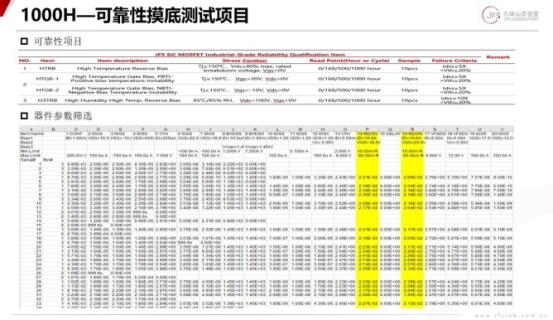

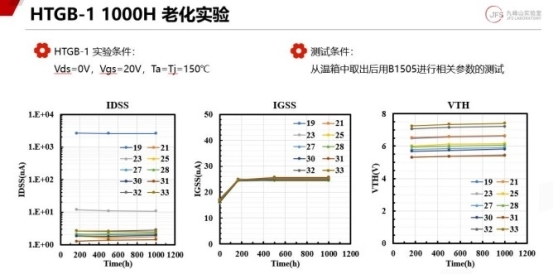

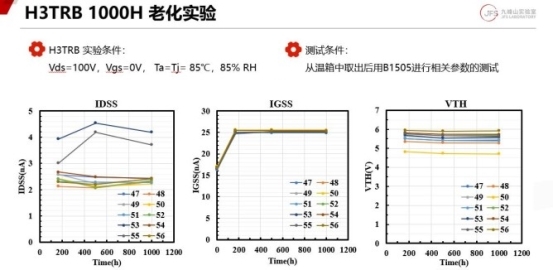

近日,九峰山实验室(JFS Laboratory)推出新型SiC Trench MOSFET科研级器件样品,旨在满足产业及科研机构对具有完全自主知识产权的SiC沟槽新型器件的测试、分析及应用探索需求,进一步推动下一代碳化硅沟槽型MOSFET功率器件的产业发展。  此次推出的科研样品分为两种IP结构: 1、SiC胶囊沟槽MOSFET科研样品 基于九峰山实验室完全自主IP的SiC胶囊型沟槽MOSFET结构,结合优化设计的新型终端技术,提供高可靠性SiC Trench MOSFET。核心专利包括CN114141627A、CN114464680A、CN114883412A等。 规格:BV≥1400 V,60~80 mΩ,可为客户提供bare die (有源区面积约3.35mm*3.35mm)或者TO-247 3 pin封装形式的器件,适用于特定测试及应用场景。10~40 mΩ器件正在流片中,可接受定制化开发。  元胞结构  终端结构  (左)阻断特性(右)导通特性 2、SiC周期性两侧深掩蔽沟槽MOSFET科研样品 基于九峰山实验室完全自主IP的SiC双侧深掩蔽沟槽MOSFET结构,已通过HTGB、H3TRB,HTRB可靠性检测。核心专利包括:CN118472041B、CN119486224A、CN119997569A、CN119342864B等。  元胞结构  (左)阻断特性(右)导通特性 规格:BV≥1400 V,20~80 mΩ,Ronsp~ 2-2.4mOhm.cm2;可为客户提供bare die(有源区面积约3.35mm*3.35mm)和TO-247 3 pin封装形式的器件,适用于特定测试及应用场景。16mΩ以下芯片(有源区面积约5mm*5mm)正在流片中,可接受定制化开发; 3、TO247封装科研样品数据及可靠性测试 科研样品都经过电性能筛选测试,及第三方可靠性摸底1000Hrs测试。采用TO-247 3 pin封装形式器件(有源区面积约3.35mm*3.35mm)的电性能实测数据如下:   1000h HTGB测试结果  1000h H3TRB测试结果 咨询及购买联系方式:wangkuan@jfslab.com.cn |

网友评论