高多层 PCB 拼板踩过的坑,资深工程师总结这 5 条血泪经验

发布时间:2025-6-26 17:08

发布者:科技新思路

|

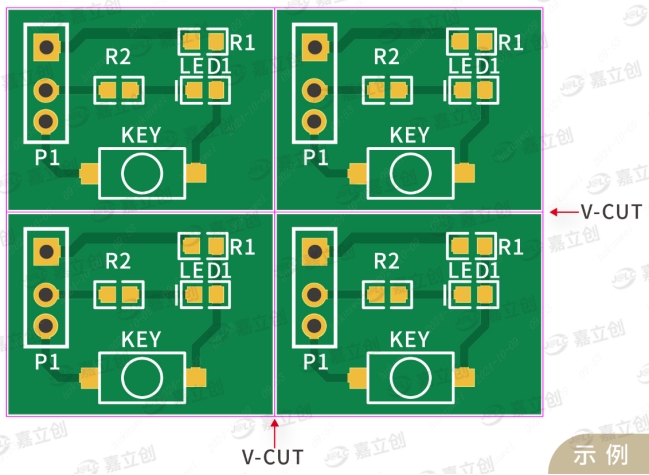

高多层 PCB 拼板因结构复杂,设计失误可能导致批量报废。以下是行业内高频出现的问题及应对策略: 一、案例 1:6 层板 V 割后内层开裂问题根源:板厚 0.6mm+V 割间距<1.2mm,多层压合应力集中;

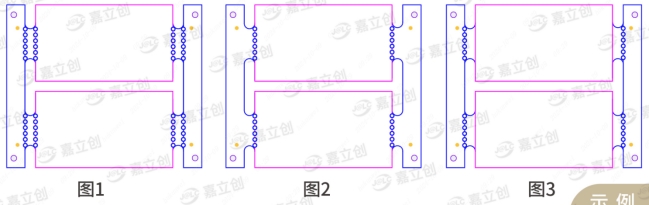

问题根源:邮票孔与内层高速信号线间距仅 0.2mm,分板毛刺刺穿绝缘层;

问题表现:工艺边宽度 5mm,多层板过炉时因热胀冷缩导致定位孔变形;

典型场景:电源层与信号层混拼,导致局部温度过高;

问题原因:传统邮票孔设计未考虑多层板硬度;

写主所知的拼板方面,嘉立创在 PCB 拼板领域优势显著,拥有专用高多层 V 割设备与五轴 CNC 铣板机,精度达 ±0.005mm。专利邮票孔设计搭配电浆清洗工艺,分板毛刺降低 60%。免费 DFM 拼板优化系统,24 小时反馈方案,高多层PCB打样周期最快48h,工艺成熟可靠。 总结:高多层 PCB 拼板需建立 “设计 - 仿真 - 打样验证” 闭环,尤其关注层间应力与热管理细节。 |

网友评论