SRAM的性能及结构

发布时间:2020-6-29 16:10

发布者:英尚微电子

|

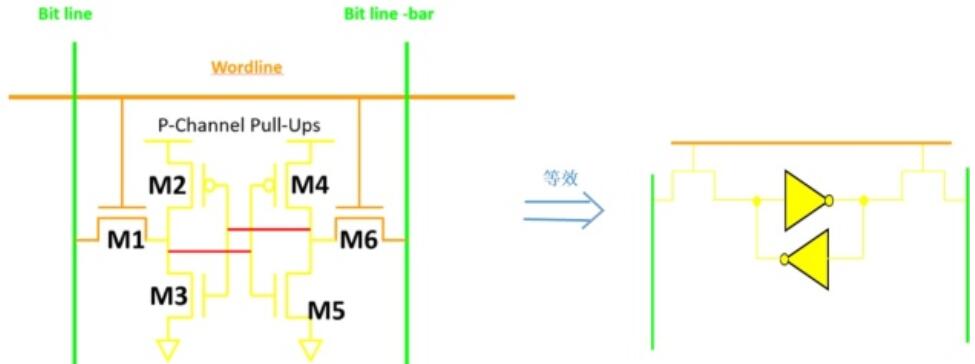

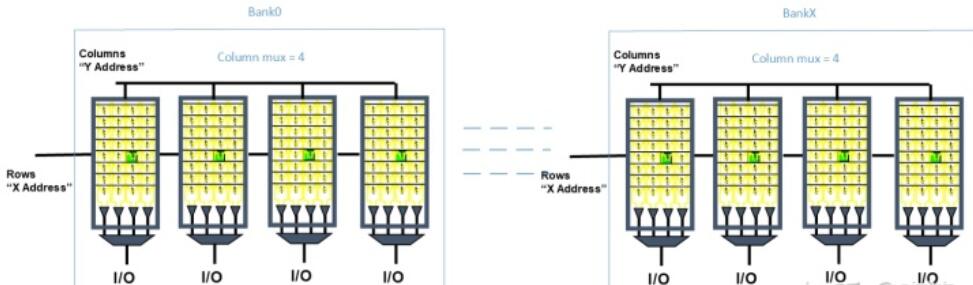

SRAM它也由晶体管组成。接通代表1,断开表示0,并且状态会保持到接收了一个改变信号为止。这些晶体管不需要刷新,但停机或断电时,它们同DRAM一样,会丢掉信息。SRAM的速度非常快,通常能以20ns或更快的速度工作。静态ram中所谓的“静态”,是指这种存储器只要保持通电,里面储存的数据就可以恒常保持。SRAM不需要刷新电路即能保存它内部存储的数据。因此SRAM具有较高的性能, SoC随着工艺进步设计复杂度增加,embeded sram也越来越多。在40nm SoC产品Sram一般在20Mbits左右,当工艺发展到28nm时Sram就增加到100Mbits。如果考虑AI产品,Sram估计更多。如何更好的测试Sram就成为量产测试的重中之重。 SRAM的性能 ·memory compiler的选择 对于一个memory size大小确定的memory block,Column Mux越大,Row address位宽越小: - memory读写的访问速度就高 (row译码选择快) - memory的面积大(cell和cell的横向距离大于纵向距离,column mux增加很增加bits per wordline--横向,减少wordline数--纵向,横向尺寸增加远大于纵向) - 因为一次选择的row地址对应的cell多,功耗也会增加 电流功耗 总电流功耗包括dynamic power和leakage power。不同的sram cell单元(比如HPC,HDC等等)功耗指标不同,体系结构设计需要在面积,速度和功耗之间寻找平衡。 -leakage current是永远存在的 Poweroff模式(cell+periphery off)< Retention模式(cell ON+periphery OFF) < Standby模式(cell+periphery on) 1Mbits memory的standby/Ret leakage电流在0.2mA左右,poweroff leakage电流在0.03mA左右。 -dynamic current:column mux,读写速度,读写辅助电路等都会影响动态电流 如果在常温状态下leakage current比较大,在高温或者大的dynamic current时必须注意thermal runaway的风险,因为温度升高leakage current会增加很快,总功耗的增加会进一步增加温度,形成正反馈。 SRAM的其他特性 SRAM的读写时间可以做成self-timing,当读写被时钟上升沿trigger以后,SRAM内有dummy bitline+dummy driver来驱动计时器得到读写的时间。得到读写时间后,用该时间访问实际sram cell保证读写时间ok。 SRAM的结构 一个6T sram cell的经典结构如图所示:  这些SRAM cell集合成如下图的多个bank的memory block,每个bank有bank address使能;在一个bank内Row address选择一个完整的wordline,Column address选择某组IO bitlines。 举个例子说明如下: 一个memory block是4096x32 cm16,该memory size = 4096*32= 128k bits, row address is 8bits (4096/16 = 256 wordlines), column address is 4 bits(0~15), Wordline bits = 32*16 = 512 bits.  |

网友评论