玩转Zynq连载22——[ex03] 基于Zynq PL的PLL配置实例

发布时间:2019-9-6 08:19

发布者:rousong1989

|

玩转Zynq连载22——[ex03] 基于Zynq PL的PLL配置实例 更多资料共享 腾讯微云链接:https://share.weiyun.com/5s6bA0s 百度网盘链接:https://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw 提取码:ld9c

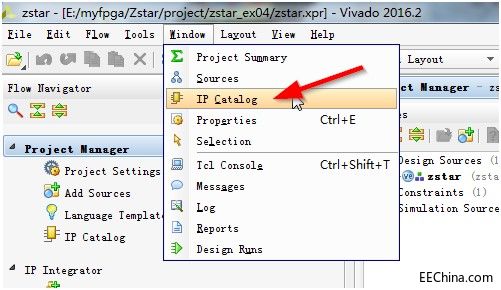

腾讯微云链接:https://share.weiyun.com/5s6bA0s 百度网盘链接:https://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw 提取码:ld9c 本实例通过PLL产生的不同频率的时钟,分别驱动3个LED指示灯闪烁一样的频率。本实例的重点其实不是LED,而是IP核的应用,当然,仅以PLL IP核为例。 参考文档《玩转Zynq-基础篇:基于FPGA的模块化设计.pdf》。 我们常说的IP核,也就是知识产权(Intellectual Property),是那些己验证的、可重利用的、具有某种确定功能的设计功能模块。IP核一般分为软IP(soft IP core)、固IP(firm IP core)和硬IP(hard IP core)。软IP是用某种高级语言来描述功能块的行为,但是并不涉及用什么电路和电路元件实现这些行为。固IP除了完成软IP所有的设计外,还完成了门电路级综合和时序仿真等设计环节,一般以门电路级网表形式提交用户使用。硬IP则是完成了综合的功能块,已有固定的拓扑布局和具体工艺,并己经经过工艺验证,具有可保证的性能。设计深度愈深,后续工序所需要做的事情就越少,但是灵活性也就越小。 在Xilinx的FPGA器件中,IP核设计是非常重要并且必不可少的一部分,应该说,前述的软IP、固IP和硬IP,在我们Zstar板载的Zynq上都能够找到踪影。而对于Vivado来说,对于Xilinx或者其第三方合作伙伴提供的,已经集成在Vivado工具界面中供设计者调用的IP,我们姑且可以称之为标准IP核;而对于Vivado未集成的,第三方或者用户自己开发设计的IP核,我们则称之为用户自定义IP核。 对于Vivado中集成的IP核,可以点击Vivado菜单Window --> IP Catalog查看。

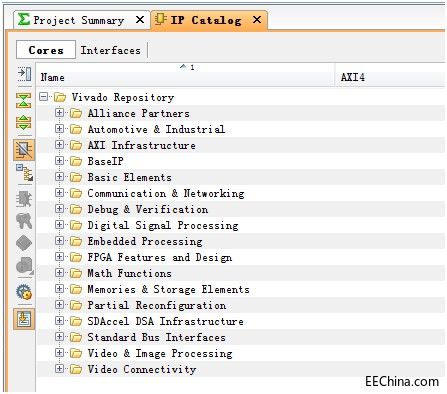

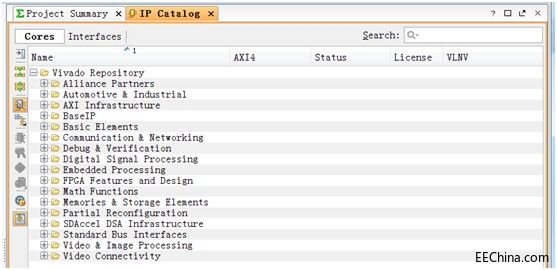

在Vivado主视窗中,IP Catalog --> Cores中,列出了Vivado已经集成的分类IP核,点击各个分类前的+号,可以查看具体分类下都有哪些可用的IP核。

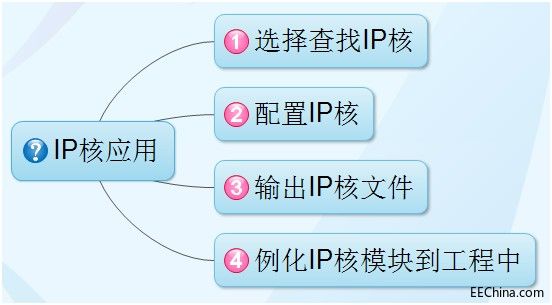

对于一般的IP核,先找到所需要的IP核,然后双击IP核弹出配置页面,配置完成后输出各类IP核相关设计文件,在用户设计中只要例化IP核模块就可以了。

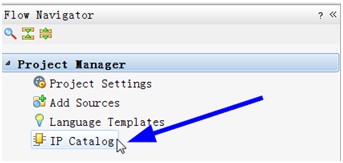

下面我们以zstar_ex04实例的PLL IP核的配置为例,看看如何添加配置Vivado中集成的标准IP核。 如图所示,点击Flow Navigator面板下的“Project Manager à IP Catalog”。

图 IP Catalog菜单 如图所示,弹出的IP Catalog面板中列出了所有Vivado自带IP核的分类列表。

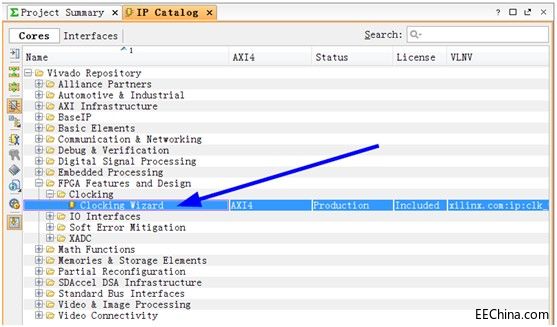

图 IP Catalog面板 如图所示,在“FPGA Features and Design à Clocking”分类展开后,可以看到名为Clocking Wizard的IP核,通过这个IP核,我们可以配置一个PLL用于对FPGA外部输入时钟做各种分频或倍频处理。点击Clocking Wizard后将弹出相应的配置页面。

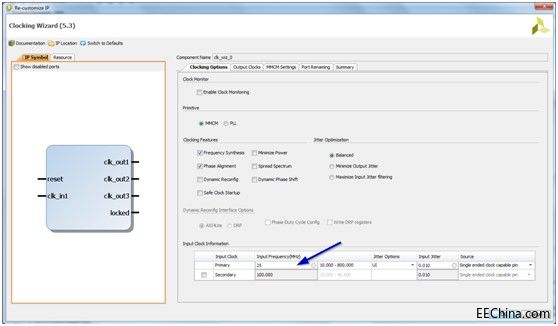

图 Clocking Wizard IP核 弹出的第一个配置页面如图所示,这里的Primitive可以选择“PLL”,然后在时钟频率(Input Clock Information)的Primary一行中设定我们的输入时钟频率(Input Frequency)为25MHz即可。

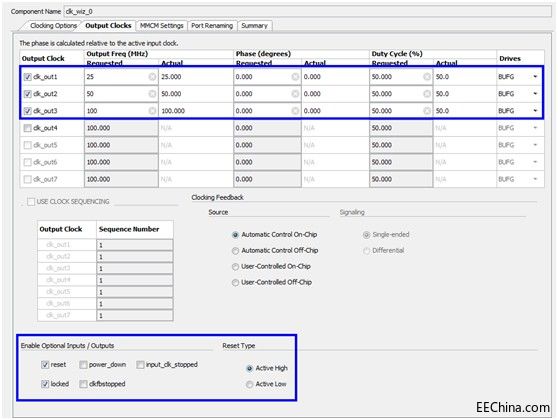

接着在Output Clocks配置页面中,如图所示,勾选clk_out1/2/3这3个时钟,分别设置其输出频率为25MHz、50MHz、100MHz。同时勾选控制信号reset和locked的,并且它们是高电平有效(Active High)。

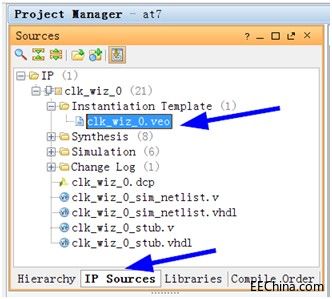

接下来几个页面不需要做配置更改,直接点击OK完成PLL的配置。 配置生效后,我们可以切换到Sources面板下方的IP Sources这个子页面中,如图所示,出现了名为clk_wiz_0的IP核,即我们刚刚配置添加的IP核。可以点击展开它,在“Instantiation Template”下方的“clk_wiz_0.veo”文件就是例化模板,可以双击打开它。

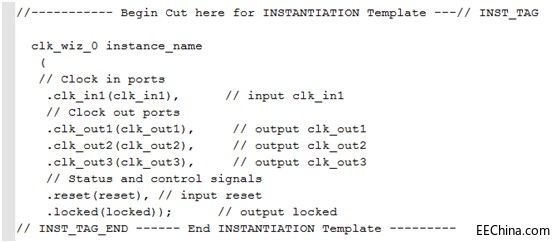

图 查看例化模板 如图所示,可以复制这个PLL的例化模板,在我们的工程中相应修改外部接口。

关于这里PLL模块的接口定义如表所示。

注:方向是相对PLL模块而言的。 参考文档《玩转Zynq-工具篇:Vivado中IP核的移植.pdf》。 参考文档《玩转Zynq-环境篇:XilinxPlatformCableUSB下载器使用指南》,将...\project\zstar_ex03\zstar.runs\impl_1路径下的zstar.bit文件烧录到Zynq中。 看到的效果D1、D2和D3这3颗LED指示灯同步闪烁。 |

网友评论