EEPROMНгПкЕФFPGAЪЕЯж_fpgaзЪСЯ_УїЕТбяжСМђЩшМЦЗЈ

ЗЂВМЪБМфЃК2017-8-2 15:23

ЗЂВМепЃКmdykj33

|

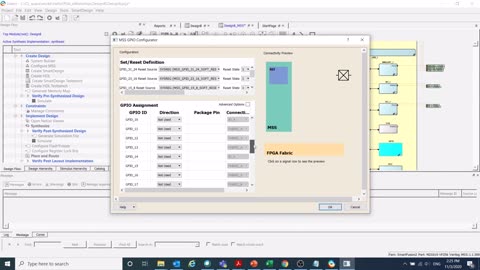

ЙЄГЬЫЕУї AT93C46дкDIНгЪеЕНЖСжИСюЪБЃЌЕижЗБЛНтТыЃЌЪ§ОндкDOв§НХЩЯДЎааЪфГіЁЃаДжмЦкЪЧЭъШЋзджїЕїЪБЕФЃЌдкаДШыжЎЧАВЛашвЊЕЅЖРЕФВСГ§жмЦкЁЃБОЯюФПвЊЧѓAT93C46ЭъГЩЖСКЭаДЙІФмЕФЛьКЯЙІФмЁЃ АИР§ВЙГфЫЕУї БОАИР§вЊЧѓЪЕЯжвЛИіAT93C46ЕФНгПкФмЙЛИљОнУќСюЃЌЪЕЯжEWENЁЂWRITEКЭREADЙІФмЃЌдкетРяЮвУЧЬсЙЉСЫОпЬхЕФЩшМЦЫМТЗЃК 1. ЩЯгЮФЃПщдкrdy=1ЪБЃЌИјГіstartУќСюЃЌПЊЪМНјааEWENЁЂWRITEЛђепREADВйзїЃЛдкrdy=0ЦкМфЃЌstartУќСюЮоаЇЁЃ 2. ЕБstartгааЇЪБЃЌШчЙћmode=0БэЪОНјааEWENВйзїЃЛmode=1БэЪОНјааWRITEВйзїЃЛmode=2БэЪОНјааREADВйзїЁЃ 3. ЕБstartгааЇЪБЃЌaddrКЭwdataгааЇЁЃ 4. ЕБНјааEWENВйзїЪБЃЌНЋaddrаДШыat93c46ЁЃ 5. ЕБНјааWRITEВйзїЪБЃЌНЋaddrКЭwdataаДШыat93c46ЁЃ ЕБНјааREADВйзїЪБЃЌНЋaddrаДШыat93c46ЃЌВЂДгat93c46ЖСЕНЪ§ОнЃЌЭЈЙ§rdataКЭrdata_vldЗЕЛиИјЩЯгЮФЃПщЁЃДњТыЮФЕЕЫЕУї  EEPROMНгПкЕФFPGAЪЕЯж.rar

(31.36 KB)

EEPROMНгПкЕФFPGAЪЕЯж.rar

(31.36 KB)

|

ЭјгбЦРТл