基于CPCI体系的高性能监测测向处理平台研究

发布时间:2010-11-9 11:36

发布者:techshare

|

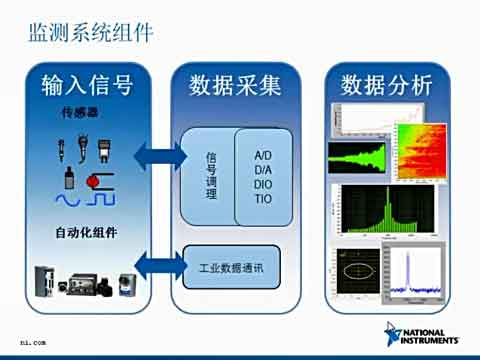

提出一种新的高速并行采样技术架构以及基于可编程芯片技术和支持灵活配置的并行处理嵌入式硬件架构。该平台集多通道高速采集、大容量数据存储、高性能DSP与大规模FPGA紧耦合实时处理等功能于一体,在综合集成与应用方面具有创新性,能够保障对多模式、多速率、多频段信号分析在信号层上频域的宽阔全覆盖和时域的连续性,同时又因其硬件上提供了丰富的资源裕量,因而可以满足信息层上对多种标准和协议分析的需求及应对其未来的演进。 为了克服传统监测测向处理系统通用性和扩展性差的缺点,本文依托软件无线电技术,对一体化设计所需的高速实时数据采集以及高速实时分析处理所需的终端处理硬件结构进行了深入阐述。该系统能够满足目前新体制和复杂信号环境下的监测测向设备各项指标要求,在有效节约资源和成本的同时,拥有较高水平的多系统集成效能。在研究过程中,本文综合考虑目前数字处理终端与不同类型CPU(主机)的接口与结构关系的优缺点,最终选择了基于Compact PCI体系的高性能监测测向处理平台设计方案。 1 系统结构 本文所述的平台结构具有灵活性和开放性的特点,其主要工作原理为:大规模FPGA用于接收多通道高速采样数据流,完成必要的预处理;主控FPGA依据每路信号的处理要求仲裁各路FPGA/DSP的片选信号,同步启动进行实时处理;多片实时处理DSP和主控FPGA紧耦合构成并行处理系统的核心;最后通过局部总线接口送入中央处理CPU作进一步分析处理,完成信息的综合存储管理等。系统结构框图如图1所示。  2 具体方案 2.1 高速数据采集 高速数据采集是高性能监测测向处理平台研究的首要问题。其设计与实现,一方面由需求引导,另一方面也要求对系统各个环节有整体的把握。合理设计模拟信号调理电路、高稳时钟产生电路、高速数据流传输路径、合理的时序及控制逻辑,并充分考虑信号完整性和电磁兼容等问题,是设计一个高性能数据采集模块的基本保障。 对于本文所关注的高速数据采集而言,若直接采用满足采样率设计要求的单片ADC芯片实现,会带来动态范围不够、缺乏灵活性和成本较高、风险较大等问题。而如果选择采用多片采样率较低的芯片用交替采样的方法来实现高速采样的方案,则电路较复杂,而且多片ADC之间延时的不一致和增益的不匹配会使采样后的信号难以无失真的复合。鉴于此,本文所述的高速数据采集设计思路是:模块化设计具有适当采样率的A/D板,基于频带分割和精确同步触发的宽带、大动态数据采集方案。本技术架构在硬件设计上具有模块化、可扩展的特色,在性能上具有等效采样率高及采样带宽不受ADC及调理电路限制的优点。采集模块工作原理如图2所示。  高速ADC是大功耗器件,通常更高的采样率将消耗更多的功耗。在使用多ADC多通道的系统中,耗散问题则更为严重。Linear推出低功耗14 bit、125MS/s ADC LTC2261,该器件功耗127 mW,用1.8 V低压模拟电源工作,提供73.4 dB的信噪比和85 dB的无寄生动态范围。0.17 ps RMS的超低孔径抖动允许其以卓越噪声性能进行中频欠采样。创新性数字输出可以设置为全速率CMOS、双数据速率CMOS或双数据速率LVDS。双数据速率数字输出允许数据在时钟的上升沿和下降沿发送,从而将所需数据线数量减少了一半。另外,对高速信号进行高分辨率的数字化处理需审慎设计时钟电路,就LTC2261和LTC其他高速14 bit系列ADC所表现出的性能看,在高速采样时,0.5 ps的抖动就可对SNR产生明显影响。由公式(1)可以看出,采样速率越高、转换位数越多,对A/D采样时钟的抖动指标要求就越高。  就LTC2261来说,10 ps的时钟抖动将在输入频率为1 MHz时产生0.8 dB的SNR损耗。而在输入频率为120 MHz时,SNR将被降低至41.1 dB。这给高精度时钟电路设计带来了挑战,通常只有选择昂贵的高性能压控晶体振荡器才能保证应有的性能。而美国国家半导体公司提供的超低噪声时钟抖动滤波器LMK04000系列提供了另外一种低成本的选择。该滤波器采用简洁的外置晶体及级联PLLatinum架构,12 kHz~20 MHz的RMS抖动为150 fs,100 Hz~20 MHz抖动为200 fs,时钟输出信号为LVPECL/2VPECL、LVDS和LVCMOS,可以有效改善系统的性能及准确度。其特点是内置高性能的级联锁相环(共2个)、低噪声晶体振荡器、高性能的内置压控振荡器以及低噪声分频器和驱动器。第一个锁相环有2个不同配置可供选择,可以选用简单的外置晶体振荡器或压控晶体振荡器模块执行滤除抖动功能。第二个锁相环可利用内置压控振荡器产生低噪声时钟。 2.2 高速高流量数据存储 采样速率及分辨率越高,则转换后的数据流传输带宽越大,对后续数据传输的实时调度和连续存储的要求就相应提高。现在通常采用的方法是通过扩展位宽以降低传输速率[4-6]。但是,如果通过扩展位宽实现高速数据流的实时海量数据存储必将增大设备规模,对存储深度或者持续采集时间的限制也是非常突出的。本文对存储容量、访问速度、存储区管理的灵活性进行了研究,结合FLASH存储阵列,设计实现了基于FLASH存储器的高速高流量数据存储卡。该存储卡符合CPCI 6U标准,具有模块化、标准化、易扩展以及高稳定性等特点,解决了数字后处理过程中在编码分析和协议解析阶段对连续无失真采样数据的实时存储难题。其主要研究内容包括:采用FPGA进行高速信号的调度处理和缓存,以解决高速数字接口的问题;采用超大规模FPGA实现对存储区的可在线配置灵活管理,以实现整个模块的高集成度、高可靠性、存储区管理灵活(支持冗余备份)等目标。由此实现的海量数据存储子系统结构采用标准化、模块化设计,具有高速率、低功耗、可移植、易扩展的特性,可以满足不同任务的需要。 图3所示是本文设计的基于CPCI标准的大存储容量、高传输带宽的通用数据存储板。板载1片Stratix III E与2片Cyclone III FPGA以及96片NAND FLASH。StratixIII E是存储板数据接收和分发的枢纽,该器件可应对存储器较多的应用,为采用乒乓结构对数据进行缓存提供资源,主要完成以下功能:提供高达1 Gb/s的差分传输速率;通过PCI接口芯片PCI9656连接到PCI总线上,实现64 bit的局部总线;通过J4/J5实现板间自定义的高速差分数据传输。2片低成本Cyclone III分别连接48片NAND,实现数据的高速分发和NAND阵列的二级管理。在高速数据存储卡的设计过程中,打通主机与存储模块之间的数据传输通道是调试的重点,这涉及FPGA中PCI本地端匹配逻辑的设计。一个典型的基于状态机设计的匹配逻辑时序如图4所示。   2.3 紧耦合和支持灵活配置的并行处理模块 主处理平台的计算能力往往构成了获取宽带信号时频域完整信息的瓶颈。本文针对一体化设计的具体需求探讨了一种紧耦合和支持灵活配置的并行处理硬件架构来解决这一问题。信号处理不同模块有不同的运算特点,设计过程中,不同的模块需要选择在不同的器件中完成。FPGA设置灵活,但是主频很难做高,通常只有几百MHz,这与DSP的几千MHz甚至于GHz相去甚远。因而,对复杂的运算和协议分析适合采用DSP处理,而FPGA则偏重于计算量大、运算结构简单的并行处理,在诸如数字下变频(DDC)、匹配滤波器、FFT的设计中具有更好的性能,而且开发方便。同时,要充分体现软件无线电的思想,达到通用性与一体化的要求,可重配置技术的突破是必须完成的任务。FPGA具有的硬件可重构性是GPP、DSP所没有的功能,所以本文采用基于大规模FPGA+高性能DSP的主处理平台设计方案也是保证系统结构具有可重配置特性的前提。同时,为了保障与本总线式结构平台的各个组成部分有好的通联性,并考虑到系统性能和处理能力的可扩展性,本模块采用CPCI作为互联控制总线,设计遵循CPCI 6U规范,并预留有SRIO(J3)、高速自定义IO(J4、J5)作为模块之间或板级芯片之间高速数据流共享和协同处理的通道。该并行处理模块硬件功能相对独立,可方便功能需要的裁剪定制。同时,这些特征也决定了硬件平台具有较长的使用周期,节约了研发经费。并行处理模块原理框图如图5所示。  本并行处理模块采用TI全新高性能1.2 GHz单核DSP TMS320C6455作为并行处理的核心,为同时执行多通道处理任务和应对同时执行多个软件的高强度、高性能应用提供资源。C6455在统一器件上完美结合了高带宽外设集成(千兆以太网MAC)、Serial RapidIO(SRIO)、运行速率553 MHz的DDR2存储器接口以及更大的存储器(L2存储器达 2 MB)。这些为提高常用算法的处理效率、提高系统扩展能力提供了原始支撑,满足了一体化的高性能设计要求。 本文基于最新技术,就高性能监测测向处理平台设计所需的高速数据采集、数据传输、实时处理等核心技术进行了研究,实现了通用系统的多功能性与专用系统的针对性的有机结合,在一体化集成与应用研究方面具有创新性。在充分体现资源裕量设计的基础上,该平台具有很好的实时处理分析和信息综合性能,可以满足多种应用背景和不同技术指标的需求,在工作方式上具有高度的灵活性和适应性。 |

网友评论