|

一.前言 项目竞标:GE PHY芯片设计 STM32Fxx7 系列(互联型产品)中内置了 MAC,配合外置的 PHY 可以实现以太网通讯。这篇文档将介绍以太网接口的信号定义,重点介绍时钟电路的设计,并给出在实践中已成功应用的设计方案,希望可以对需要进行以太网电路设计的朋友提供 帮助。 二.以太网接口 STM32 的以太网支持 10M/100M bits 的全双工和半双工的工作方式,其中的 MAC 通过 MII 接口或者 RMII 接口与 PHY 通讯。 1. MII MII 接口标准定义了 16 跟信号线,根据功能将其可以分为 3 组(发送,接收,载波侦听 和冲突监测),另外还 有用于对 PHY 进行配置的 SMI 接口。

发送 ·TX_CLK:MII 接口需要 25MHz 的时钟(100Mbits 传输速率时),当以 10Mbits 的速率工作,PHY 内部的电路会对 25MHz 的信号进行十分频以得到 2.5MHz 的时钟。 ·TXD[3 :0] : 根据时钟速率,不难算出 TXD 需要 4 根数据线。数据线需要与时钟保持同步。 ·TX_EN : 发送使能信号,也需要与时钟保持同步。 ·TX_ER : 发送错误指示信号,MAC 通过此信号向 PHY 表示数据无效。需要注意的是在许多 PHY 和 MAC 中,这个 信号是没有的(STM32 就没有这个信号,图中用虚线表示),由于在另一端的接 收信号中包含 RX_ER,因此这个 信号是不必要的。 接收·RX_CLK: 接收时钟与发送时钟完全类似。 ·RXD[3 :0]: 与发送数据线完全类似。 ·RX_ER:接收错误指示信号,PHY 通过此信号向 MAC 层表示在某一帧数据中发现问题。需要与RX_DV 一起使用。 ·RX_DV:与 RX_ER 一起进行出错分析。 载波侦听和冲突监测CRS,COL:这两根信号线在半双工工作方式下提供载波侦听和冲突监测功能,全双工下无用。

SMI 接口MDC,MDIO:对 PHY 进行配置的接口。可以通过 GPIO 口进行模拟。 2. RMII

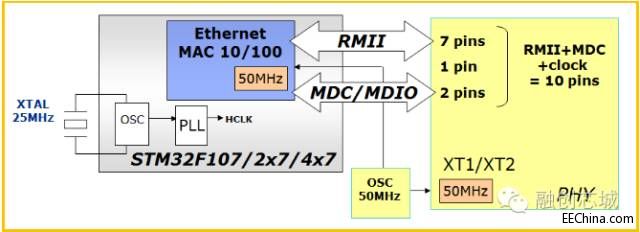

RMII 接口可以简单的理解为(Reduce-MII)接口,即减少了 MII 接口中信号线的数量。基本原理是通 过提高时钟速率来完成的(RMII 的时钟为 50MHz),因此发送/接收数据线都只需要两根,并合并了一定功能引脚。 CRS_DV:此信号是 MII 接口中 CRS 和 RX_DV 的复合信号。

三. 时钟电路设计

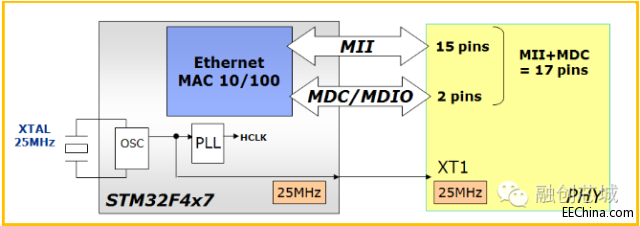

仔细观察图 1 和图 2,细心的读者会发现两者在时钟电路上有着明显的区别。在 MII 接口电路中,时钟由 PHY 向 MAC 提供 (时钟源由通讯的一方来提供);在 RMII 接口电路中,MAC 和 PHY 共同使用来 自外部的时钟信号(数据的发送方和接收 方采用同一个时钟源)。 由于 MAC 和 PHY 的通讯速率相对较快,为保证硬件电路的可靠性,在设计中应该通过器件的数据手册了解相关参数以确定 具体的电路方式。一般需要注意的有: ·上升时间/下降时间 t_rise/t_fall : STM32 的 GPIO 口可以进行摆率的设置,不同摆率下上升时间和下降时间是不同的。 尤为需要注意的是,当使用 MCO(Main Clock Output 需要了解此功能的读者 请阅读参考手册)对多个 PHY 提供 时钟,需考虑负载的增加,对输出能力的要求的影响。 ·时钟抖动(短周期)jitter(short term):特别需要注意的是此项参数,不同的 PHY 对此项参数的有不同的要求,一般 多要求 jitter 小于几十个 ps,有些 PHY 的则要求 jitter 小于几百个 ps。STM32 的 MCO 直接输出 HSE 的时钟抖动 一般在 30~40ps,但若使用 PLL 对 HSE 倍频后,再由 MCO 输出 会带来几百个 ps 的时钟抖动。 下面将分别介绍目前在实践中应用最为广泛的两种接口电路。

1.MII 接口设计

图 3 MII 接口设计实例 如图 3 所示,此系统是典型的 MII 接口电路设计,PHY 所需的时钟由 STM32 的 MCO 管脚输出(直接输出 HSE 的信号,没 有经过 PLL 处理)。需保证 MCO 输出的时钟满足 PHY 的要求。 2.RMII 时钟电路

图 4 RMII 接口设计实例 如图 4 所示,此系统是典型的 RMII 接口电路设计,MAC 和 PHY 所需的时钟由外部的有源晶振(50MHz)提供,需保证OSC 输出的时钟满足 MAC 和 PHY 的要求。 四. 结语 尽管本文讨论的是以太网电路的设计要点,事实上,在数字电路接口的设计中,了解信号链走向和器件的参数要求都是必要 的,也只要如此,才可以保证数字电路接口的硬件可靠性。

文章来源:微信公众号 融创芯城(一站式电子元器件、PCB、PCBA购买服务平台,项目众包平台,方案共享平台)

|