DSPΦΦ θ–≠÷ζΫχ––ΗΏΥΌ¥°–– ΐΨίΖ÷Έω

ΖΔ≤Φ ±ΦδΘΚ2010-9-25 23:37

ΖΔ≤Φ’ΏΘΚeetech

|

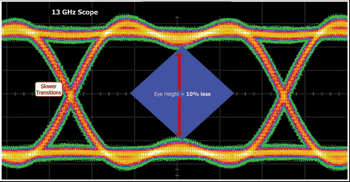

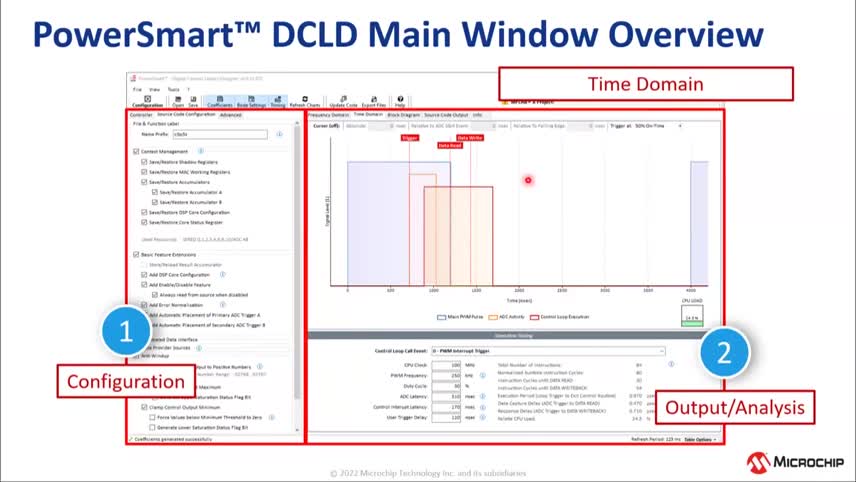

–≈Κ≈Άξ’ϊ–‘ ¥°––ΉήœΏΦΦ θ…œΒΡ–≈Κ≈Άξ’ϊ–‘≤βΝΩ“―Ψ≠≥…ΈΣ…ηΦΤ»Υ‘±≤βΝΩΙΛΉςΒΡ÷Ί“ΣΉι≥…≤ΩΖ÷Θ§»γPCI Express 2.0ΓΔ¥°––ATA IIIΚΆHDMI 1.3ΓΘ“Μ÷¬–‘≤β ‘÷–”ωΒΫΒΡ–μΕύΈ Χβ‘¥”Ύ≤®–Έ…œΒΡ≤ΜάμœκΧΊΒψΘ§»γ‘κ…υΓΔΕΕΕ·ΚΆΕ® ±Μϊ±δΓΘ¥°––±ξΉΦΥθ’≠ΝΥΕ® ±»ίœόΘ§“Σ«σ≤βΝΩΙΛΨΏ÷–ΧαΙ©ΗϋΕύΒΡ¥χΩμΚΆΗϋΗΏΒΡΨΪΕ»ΓΘ”κ¥ΥΆ§ ±Θ§ΜΙ“Σ«σ Ι≤βΝΩ±Ψ…μΒΡ”Αœλ¥οΒΫΉν–ΓΜ·ΓΘ ―έΆΦ≤βΝΩ Ψ≤®ΤςΒΡ¥χΩμ”ΑœλΉ≈÷ΝΙΊ÷Ί“ΣΒΡ–≈Κ≈―έΆΦΓΘ―έΆΦ «“Μ÷÷––“Β±ξΉΦ Ψ≤®ΤςΆΦœώΘ§“≤ «“Μ÷¬–‘≤β ‘ΚΆ―ι÷Λ≤β ‘ΒΡΜυ ·Θ§Υϋœ‘ Ψ1Ηω ΐΨίΓΑΈΜΓ±ΜρΒΞΈΜΦδΗτΘ§Υυ”–Ω…ΡήΒΡ±Ώ―ΊΧχ±δΚΆΉ¥Χ§ΕΦΒΰΦ”‘Ύ“ΜΗωΆξ…ΤΒΡ ”ΆΦ÷–ΓΘΒΟΒΫΒΡΤΝΡΜ‘Ύ÷––Ρ¥σΧε≥ ΝυΫ«–Έ’≈ΩΣ«χ”ρΒΡ÷ήΈßœ‘ Ψ¥σΝΩΒΡ≤®–ΈΙλΦΘΘ§’β”–ΒψœσΓΑ―έΨΠΓ±Θ§Τδ’≈ΩΣ≥ΧΕ»”Οά¥ΚβΝΩ–≈Κ≈÷ ΝΩ(ΓΑ’≈ΩΣΓ±ΒΟ‘ΫΕύ‘ΫΚΟ)ΓΘ¥°––¬ΏΦ≠…η±Η±Ί–κ«χΖ÷―έΆΦ«χ”ρΡΎ≤Ω«ε≥ΰΒΡΉ¥Χ§Γ°1Γ·ΜρΉ¥Χ§Γ°0Γ·Θ§“‘’ΐ»ΖΕ‘ ΐΨίΉς≥ωœλ”ΠΓΘΆ®≥ΘΜα Ι”ΟΆΦ–ΈΓΑΡΘΑεΓ±Ε®“ε―έΆΦ≤β ‘Ά®Ιΐ/ ßΑήΒΡ«χ”ρΓΘ ‘Ύ≤…Φ·–≈Κ≈ ±Θ§¥χΩμ≤ΜΉψΒΡ Ψ≤®ΤςΙωΫΒΒΡΖυΕ»Ω…ΡήΜαΗΏ¥ο1 dB (¥Ι÷±ΖυΕ»)ΓΘ“≈ΚΕΒΡ «Θ§’β÷÷ΥπΚΡ“ΜΑψΜα¬δ‘Ύ―έΆΦ’≈ΩΣΒΡ«χ”ρ÷–Θ§«ΓΚΟ «Ϋχ––ΕΰΫχ÷Τ≈–Ε®ΒΡΒΊΖΫΓΘ“ρ¥ΥΘ§≥δΉψΒΡ¥χΩμ‘Ύ―έΆΦ≤βΝΩΦΑ±Ώ―Ί≤βΝΩ÷–÷ΝΙΊ÷Ί“ΣΓΘ –“‘ΥΒΡ «Θ§œ÷‘Ύ –≥Γ…œ≥ωœ÷ΝΥ–μΕύ“«ΤςΘ§Ω…“‘ΧαΙ©ΉνΙΊΦϋΒΡΕ® ±ΚΆ±Ώ―Ί≤βΝΩ“Σ«σΒΡ¥χΩμΓΘΉν–¬ΒΡ¥°––Ζ÷Έω“«”Β”–20 GHzΒΡ¥χΩμΘ§‘ΌΦ”…œΥυ”–Ά®Βά…œ50 GS/sΒΡ≤…―υ¬ Θ§Ω…“‘¬ζΉψΒ±«Α Ι”ΟΒΡ»ΪœΒΝ–¥°––ΉήœΏΒΡ–η«σ ΓΘ‘Ύ’β–©ΥΌ¬ …œΘ§≤®–Έ±Ώ―Ί10-90%≤ΩΖ÷ΒΡ δ»κ…œ…ΐ ±ΦδΫωΈΣ22 psΓΘ’ΐ»γ±ΨΈΡΚσΟφΧ÷¬έΒΡΡ«―υΘ§Μυ”ΎDSPΒΡ¥χΩμ‘ω«ΩΦΦ θΧαΙ©ΝΥ÷±ΒΫΉνΩλΥΌΒΡΒΎ“Μ¥ζ¥°––±ξΉΦΒΎΈεΗω–≥≤®ΖΕΈßΒΡΤΫΧΙΒΡΤΒ¬ –‘ΡήΓΘ’β“ΜΙΠΡή“≤±Θ÷ΛΝΥΥυ”–Ά®Βά÷–ΒΡΉν”≈ΤΒ¬ ΚΆΖυΕ»œλ”ΠΤΞ≈δΓΘ ΒΎΈεΗω–≥≤®≤βΝΩ ¥σΕύ ΐΒΎ“Μ¥ζ¥°––ΉήœΏΫαΙΙΒΡ ΐΨίΥΌ¬ ÷ς“ΣΦ·÷–‘Ύ2.5Gbit/sΚΆ3.125 Gbit/s÷°ΦδΘ§’β–©ΥΌ¬ ΥΤΚθΆξ»ΪΈΜ”ΎΒ±«Α4GHzΚΆ5 GHz Ψ≤®ΤςΒΡ’ΤΩΊΖΕΈßΡΎΓΘΒΪ «Θ§–≈Κ≈±Θ’φΕ»≤βΝΩ–η“ΣΒΡ¥χΩμ“ΣΗΏΒΟΕύΘ§¥σΕύ ΐ±ξΉΦΜζΙΙ“―Ψ≠»œ ΕΒΫ’β÷÷–η«σΘ§ΥϊΟ«÷ΗΕ®ΥΌΕ»ΉψΙΜΩλΒΡ“«ΤςΘ§“‘≤ΕΜώ ±÷”–≈Κ≈ΒΡΒΎΈεΗω–≥≤®ΓΘ ≤ΕΜώΒΎΈεΗω–≥≤®ΈΣΦλΕ®ΚΆΖ÷ΈωΩλΥΌ…œ…ΐ ±Φδ–≈Κ≈ΧαΙ©ΝΥΥυ–ηΒΡΨΪΕ»Θ§Ά§ ±ΈΣ±Θ÷ΛΉΦ»ΖΒΡΫαΙϊΧαΙ©ΝΥΗϋΕύΒΡ”ύΝΩΓΘ ΆΦ1ΥΒΟςΝΥ‘θ―υ‘ω«ΩΖυΕ»”ύΝΩΓΘΧΊ±π «Θ§ΥϋΥΒΟςΝΥ20 GHz Ψ≤®ΤςΚΆ13 GHz Ψ≤®Τς÷°ΦδΒΡ≤ν“λΘ§±μΟς¥χΩμΗϋΗΏΒΡ“«Τς‘Ύ6.25 Gbit/s ΐΨίΝςPCI-E Gen2–≈Κ≈…œΧαΙ©ΒΡ”ύΝΩ“ΣΗΏΒΟΕύΓΘ‘Ύ20 GHz ±Θ§Υϋ≤ΕΜώΒΎΈεΗω–≥≤®Θ§‘ΎΖ«≥ΘΓΑΗ…ΨΜΒΡΓ±―έΆΦ÷–Ω…“‘Οςœ‘Ω¥≥ω≥δΉψΒΡ”ύΝΩΓΘ‘Ύ13 GHz Ψ≤®Τς…œΘ§ΟΜ”–ΉψΙΜΒΡ¥χΩμ≤ΕΜώΒΎΈεΗω–≈Κ≈Θ§–≈Κ≈¬δ‘ΎΡΘΑεΆβΟφΓΘ  Ρ≥–©±ξΉΦ–ΓΉιΘ§ΧΊ±π «PCI SIGΘ§’ΐ≈§ΝΠ»ΖΕ®≤ΕΜώΒΎΈεΗω–≥≤®±Ί–κΧαΙ©ΒΡΨΏΧε¥χΩμΓΘ Εύ¬ΖΫαΙΙ ΗϋΩλΒΡ¥°––ΉήœΏΘ§Αϋά®ΒΎΕΰ¥ζΚΆΒΎ»ΐ¥ζ¥°––ΉήœΏΫαΙΙΘ§»γHDMI 1.3ΓΔSATA IIIΚΆPCI-Express 2.0Θ§‘ΎΒΞ¬Ζ”Π”Ο÷–ΧαΙ©ΝΥΗϋΗΏΒΡ–‘ΡήΘ§Ά§ ±ΥϋΟ«“≤ΉςΈΣ¥°–– ΐΨίΉήœΏΫαΙΙ Βœ÷Θ§Τδ≤…”ΟΕύΧθΆ®¬ΖΘ§ Βœ÷ΗϋΗΏΒΡ ΐΨίΫΜΜΜΥΌ¬ ΓΘ‘ΎΕύ¬Ζ≈δ÷Ο÷–Θ§¥°–– ΐΨίΑϋœ»±ΜΖ÷ΫβΘ§»ΜΚσΜυ±Ψ…œΆ§ ±Ά®Ιΐ4ΧθΓΔ8ΧθΜρΗϋΕύΒΡΓΑΆ®¬ΖΓ±Ϋχ––¥ΪΥΆ(ΆΦ2)ΓΘ‘ΎΕύ¬Ζ¥°––ΉήœΏ…œ÷¥––―ι÷ΛΜρΒς ‘ΙΛΉςΒΡ…ηΦΤ»Υ‘±–η“Σ≤β ‘ΫβΨωΖΫΑΗΘ§Ά§ ±‘Ύ4ΧθΜρ4Χθ“‘…œΒΡΆ®¬Ζ÷–≤ΕΜώ Β ± ΐΨίΘ§≤ΔΧαΙ©±Ί“ΣΒΡ–‘ΡήΘ§¬ζΉψΉν–¬“Μ¥ζ¥°––ΉήœΏΦΦ θΓΘ‘Ύ―ι÷Λ÷–Θ§±Ί–η‘ΎΥυ”––≈Κ≈Ά®¬Ζ÷–Ά§ ±≤ΕΜώ ΐΨίΘ§≤Δ Βœ÷ ±ΦδœύΙΊΓΘ –≥Γ…œœ÷‘ΎΧαΙ©ΝΥ Β ±≤…―υ¬ ΗΏ¥ο50 GS/sΒΡ“«ΤςΘ§Ω…“‘‘ΎΥυ”– δ»κΆ®Βά÷– Βœ÷Ϋή≥ωΒΡ ±ΦδΖ÷±φ¬ Θ§Ά§ ±‘Ύ»Ϊ≤Ω4ΧθΆ®Βά…œ≤ΕΜώ≥Λ¥ο4 msΒΡ ±ΦδœύΙΊΒΡ¥°–– ΐΨί“ΒΈώΓΘ’β÷÷ Β ±≤ΕΜώΡήΝΠ”κ…ν¥φ¥ΔΤςœύΫαΚœΘ§ ΙΒΟ…ηΦΤ»Υ‘±ΡήΙΜ‘ΎΟΩΧθΆ®¬Ζ÷–Ζ÷Έω”–Έ ΧβΒΡ ¬ΦΰΜρ÷°«ΑΜρ÷°Κσ”κΉήœΏ“ΒΈώœύΙΊΒΡ¥μΈσΓΘ  ΕΕΕ·≤β ‘ ΕΕΕ· «¥°––ΉήœΏΩΣΖΔ»Υ‘±ΙΊΉΔΒΡΝμ“ΜΗωΈ ΧβΓΘ‘ΎΡ≥–©«ιΩωœ¬Θ§±Ί–κΝΩΜ·ΤδΕ‘ΗςΗω–≈Κ≈±Ώ―ΊΒΡ”ΑœλΘ§ΒΪΗϋ÷Ί“ΣΒΡ «Θ§ΕΕΕ·‘Ύ―έΆΦ≤βΝΩ÷–ΖΔΜ”Ή≈“ΜΕ®ΒΡΉς”ΟΓΘΥϋΩ…“‘ΫΒΒΆ…œ…ΐ―ΊΚΆœ¬ΫΒ―ΊœύΙΊΒΡ―έΆΦΩμΕ»Θ§Ω…ΡήΜαΒΦ÷¬ΡΘΑεΈΞΙφΓΘ »γΙϊΙέ≤λΒΫΕΕΕ·Θ§Ρ«Ο¥ΕΕΕ· «ά¥Ή‘±Μ≤β…η±ΗΜΙ «”…”Ύ“«ΤςΒΦ÷¬ΒΡ≤βΝΩΗΫ τ≤ζΈο Ψ≤®ΤςΒΡ¥ΞΖΔΕΕΕ·ΚΆΕΕΕ·‘κΒΉ(JNF)Ω…ΡήΜα”Αœλ≤βΒΟΒΡΕΕΕ·Θ§ΥϋΟ«Ω…ΡήΜα Ι―έΆΦ±δ’≠Θ§≤ζ…ζΈσΒΦ–‘ΒΡΡΘΑε ßΑήΓΘ “ΒΡΎ“―Ψ≠ΩΣΖΔ≥ωΨΪ–Ρ…ηΦΤΒΡ»μΦΰ–Θ’ΐΖΫΑΗΘ§“‘ Ι Ψ≤®ΤςΒΡ¥ΞΖΔΕΕΕ·¥οΒΫΉν–ΓΘ§’β÷÷ΖΫΖ®Ω…ΆϊΗΡ…ΤΒ»–ß ±Φδ≤…Φ·ΡΘ Ϋœ¬ΒΡ–‘ΡήΘ§Τδ÷–±Ί–κΕ‘ΟΩΗω―υΒψ÷Ί–¬¥ΞΖΔ≤…Φ·ΓΘΒΪ «Θ§¥ΞΖΔΕΕΕ·Ε‘Μυ”ΎΒΞ¥Έ Β ±≤…Φ·ΒΡΕΕΕ·≤βΝΩΟΜ”–”ΑœλΓΘ‘Ύ’β÷÷«ιΩωœ¬Θ§JNFœΒ ΐΜα”ΑœλΒ»–ß ±Φδ≤ΕΜώΚΆ Β ±≤ΕΜώΓΘ ΗϋΚΟΒΡΖΫΖ® « Ι”Ο‘Ύ¥Ι÷±ΡΘ ΐΉΣΜΜΤς÷–”Β”–≥δΉψΕ·Χ§ΖΕΈß(»γ¥Ι÷±Ηώ)ΒΡ“«ΤςΘ§“‘ Βœ÷ΗΏ–≈‘κ±»ΦΑΦΪΒΆΒΡJNF (Βδ–Ά÷ΒΈΣ400 fs RMS)ΓΘ’β÷÷ Ψ≤®ΤςΩ…“‘ Βœ÷ΕΕΕ·≤βΝΩΘ§“«Τς±Ψ…μΕ‘ΕΕΕ·ΒΡ”Αœλ≤Μ¥σ(ΆΦ3)ΓΘ  ≤βΝΩΒΆΤΒΕΕΕ· «“ΜΗωΧτ’ΫΓΘΥϋΕ‘ Ψ≤®ΤςΧα≥ωΝΥΝΫΗωœύΜΞΟ§ΕήΒΡ–η«σΘΚ Ψ≤®Τς“Σ≤ΕΜώœΗΈΔΒΡΕ® ±œΗΫΎΘ§Ά§ ±“Σ‘ΎΚή≥ΛΒΡ ±ΦδΩγΕ»ΡΎ Βœ÷’β“ΜΒψΓΘΈΣ“‘ΉψΙΜΒΡΖ÷±φ¬ ≤ΕΜώΕΕΕ·œΗΫΎΘ§Ά®≥Θ±Ί–ηΫχ»κΉν¥σ≤…―υ¬ (»γ50 GS/sΘ§œύΒ±”Ύ20 psΒΡ≤…―υΦδΗτ)ΓΘ≤…―υ ΐΨί“‘ΗΟΥΌ¬ ―ΗΥΌάέΜΐ‘Ύ≤®–Έ¥φ¥ΔΤς÷–ΓΘΒΪ «Θ§ΒΆΤΒΕΕΕ·«ς ΤΜα‘ΎΦΗΚΝΟκΡΎ–Έ≥…ΓΘ“ρ¥ΥΘ§»γΙϊ“«Τς“Σ≤ΕΜώΉψΙΜΒΡ‘Υ––÷ήΤΎΘ§»ΖΕ®ΒΆΤΒΕΕΕ·Ε‘≤βΝΩΒΡ”ΑœλΘ§Ρ«Ο¥–η“ΣΖ«≥Θ…νΒΡ¥φ¥ΔΤςΓΘ Ε‘¥φ¥Δ»ίΝΩΟΩΧθΆ®ΒάΗΏ¥ο200 M―υΒψΒΡ“«ΤςΘ§‘Ύ»Ϊ≤Ω≤…―υ¬ œ¬Ω…“‘¥φ¥ΔΉν≥Λ4 msΒΡ≤…―υ ΐΨίΓΘΙΛ≥Χ ΠΩ…“‘≤ιΩ¥ΗςΗω±Ώ―Ί…œΦΑΦΗΑΌΆρΗω÷ήΤΎΚσΖΔ…ζΒΡΆ§“Μ≤®–ΈΦ«¬ΦΕΕΕ·±δΜ·÷–ΒΡ…ν»κΕΕΕ·œΗΫΎΓΘ  »ΞΒτ≤βΝΩ”Αœλ ¥°––ΉήœΏΜΖΨ≥÷–ΒΡ–¬–Υ±ξΉΦ“Σ«σ¥”≤βΝΩΫαΙϊ÷–»ΞΒτ≤βΝΩΆ®ΒάΒΡ¥Ϊ δ”ΑœλΘ§Τδ÷–ΖΫ Ϋ÷°“Μ «”Π”Ο ΐΉ÷¬Υ≤®Θ§‘Ύ Ψ≤®ΤςΡΎ≤Ω÷¥––“‘«Α“Σ«σΒΞΕά≤Ϋ÷ηΚΆΒΞΕά”Π”Ο»μΦΰΒΡΦΤΥψ≤ΌΉςΓΘ –≈Κ≈¬Υ≤®ΙΛ“’Ω…“‘ΉΖΥίΒΫΡΘΡβΒγΉ”ΤςΦΰΒΡ‘γΤΎ ±¥ζΘ§Β± ±¬Υ≤®Τς «”…άκ…ΔΒΡΒγΉηΤςΓΔΒγ»ίΤςΚΆΒγΗ–ΤςΉι≥…ΒΡ“ΜΗωΒγ¬ΖΓΘ‘ΎΒ±«ΑΒΡDSPΝλ”ρ÷–Θ§¬Υ≤®Τς «“Μ÷÷–όΗΡ≤®–Έ–ΈΉ¥ΓΔ“ύΦ¥ΤΒ¬ ≥…Ζ÷ΒΡ ΐ―ß≥Χ–ρΘ§’β‘ΎΚή¥σ≥ΧΕ»…œ”κ‘≠ά¥ΒΡΡΘΡβ¬Υ≤®ΤςœύΆ§ΓΘΒΪ «Θ§Υϋ“‘ ΐΉ÷ΖΫ Ϋ¥Πάμ–≈Κ≈Θ§¥”ΦρΒΞΒΡ≥ΥΖ®ΒΫΦθΖ®ΙΪ ΫΘ§÷¥––Ης÷÷Κ· ΐ‘ΥΥψΓΘ ’β“ΜΙΐ≥ΧΑϋά®Α―FIR (”–œό¬ω≥εœλ”Π)¬Υ≤®≤Έ ΐ δ»κ“«ΤςΒΡ―ίΥψœΒΆ≥÷–ΓΘ ΐΉ÷¬Υ≤®Τς¥”≤βΝΩ÷–»ΞΒτΦΤΥψΒΟ≥ωΒΡΥπΚΡΧΊΒψΘ§ Ψ≤®Τςœ‘ ΨΓΑ«ε≥ΐΓ±ΚσΒΡ≤®–Έ«ζœΏΓΘΤδΫαΙϊ «“ΜΗω≤Μ ή≤βΝΩΝ§Ϋ””ΑœλΒΡ―έΆΦΘ§“‘ΦΑΡήΙΜΗϋΉΦ»ΖΒΊΖ¥”≥Ήν÷’”ΟΜß”Π”Ο÷–…η±Η‘Υ––ΧΊΒψΒΡ―έΆΦΓΘ Ά®ΙΐΉςΈΣ–≈Κ≈¬ΖΨΕ≤ΜΩ…Ζ÷ΗνΒΡ“Μ≤ΩΖ÷ Ι”ΟFIR¬Υ≤®ΤςΘ§Ω…“‘ Βœ÷ΙψΖΚΒΡ»Έ“β¬Υ≤®ΧΊΒψΦΑΗΏΦΕΗΏΥΌ¥°––≤βΝΩΦΦ θΘ§ΑϋΡήΙΜΖ÷Έω≤ΜΡήΜώΒΟΒΡ–≈Κ≈ΒΡΓΑ–ιΡβ≤β ‘ΒψΓ±ΓΘ ”κ“‘«ΑΒΡΡΘΡβΦΦ θœύ±»Θ§DSP¬Υ≤®Τς¥σ¥σΧαΗΏΝΥΨΪΕ»ΓΔœΏ–‘Ε»ΚΆΈ»Ε®–‘ΓΘFIR¬Υ≤®ΤςΈ»Ε®Θ§≤ΜΡή’ώΒ¥Θ§±μœ÷≥ωœΏ–‘œύΈΜœλ”ΠΘ§Φ¥Υυ”–ΤΒ¬ Μα“‘œύΆ§ΒΡ―”≥Ό ΐΝΩΆ®Ιΐ¬Υ≤®ΤςΘ§¥”Εχ Ι ß’φ¥οΒΫΉν–ΓΓΘ¥ΥΆβΘ§FIR¬Υ≤®ΤςΒΡ¬ω≥εœλ”Π”Β”–”–œόΒΡΩ…“‘ΝΩΜ·ΒΡ ±Φδ÷ήΤΎΘ§“ρ¥ΥΩ…“‘‘Λ≤βΚΆΩΊ÷ΤΤδ”ΑœλΓΘ ¬Υ≤®Ω…“‘”Ο”Ύ–μΕύ Ψ≤®Τς≤βΝΩ”Π”ΟΘ§Ω…“‘ Ι”Ο¬Υ≤®ΫβΨω»’“φ≥ΘΦϊΒΡΕύΗωΗΏΥΌ≤βΝΩΈ ΧβΓΘάΐ»γΘ§Ά®Ιΐ¬Υ≤®Θ§ΙΛ≥Χ ΠΩ…“‘œό÷Τ¥χΩμΘ§ΫΒΒΆ‘κ…υΘ§Ά§ ±±Θ≥÷ΗΏΕ® ±Ζ÷±φ¬ ΓΘΜΙΩ…“‘ Ι”Ο¬Υ≤®Θ§ΩΊ÷Τ Ψ≤®Τςœλ”Π‘ΎΤΒ¬ ΖΕΈßΗΏΕΥ÷°…œΓΑΙωΫΒΓ±ΒΡΖΫ ΫΓΘ ”ΟΜß÷ΗΕ®ΒΡΧΊΒψ Ήν–¬“Μ¥ζΗΏ–‘Ρή≤β ‘“«Τς Ι”Ο»Έ“βFIR¬Υ≤®ΤςΘ§Ά®ΙΐΦ”‘Ί‘ΎMatlabΜράύΥΤ≥Χ–ρ÷–ΩΣΖΔΒΡ”ΟΜß÷ΗΕ®œΒ ΐΘ§Ω…“‘Φρ±ψΒΊΗΡ±δ¬Υ≤®ΤςΒΡΧΊΒψ(ΆΦ4)ΓΘ  ’β÷÷”ΟΜßΩ…“‘Ε®“εΒΡ¬Υ≤®ΦΦ θΈΣ÷ß≥÷ΗΏΥΌ≤βΝΩΧαΙ©ΝΥ«Ω¥σΒΡΙΛΨΏΓΘάΐ»γΘ§Φύ≤β–≈Κ≈“―Ψ≠≥…ΈΣ≤βΝΩ¥°–– ΐΨί…η±Η–‘ΡήΒΡ…ηΦΤ»Υ‘±ΙΊΉΔΒΡ“ΜΗωΙΊΦϋΈ ΧβΘ§ΧΊ±π «‘Ύ≤βΝΩΫ” ’ΒΞ‘Σ ±ΓΘ”–“Μ–©–≈Κ≈ «Ά®Ιΐ»ΈΚΈΧΫΆΖΜρ≤β ‘ΒψΕΦΒΟ≤ΜΒΫΒΡΓΘ ¬ Β÷ΛΟςΘ§Μυ”Ύ’β“Μ‘≠“ρΘ§Ϋ” ’Μζ δ»κ»ίœό≤βΝΩΦΪΨΏΧτ’Ϋ–‘ΓΘ‘Ύ’ΐ≥Θ«ιΩωœ¬Θ§¥°––…η±Η÷–ΒΡΫ” ’Μζ δ»κΕ‘≤ιΩ¥–≈Κ≈ά¥ΥΒ «ΦΗΚθΟΜ”–»ΈΚΈ“β“εΒΡΫ”»κΒψΘ§“ρΈΣΗ––Υ»ΛΒΡ–≈Κ≈”……η±ΗΡΎ≤ΩΒΡ¬Υ≤®Τς¥ΠάμΘ§“‘ΤΪ÷ΟΆ®ΙΐΒγά¬ΓΔPCBΙλΦΘΚΆΝ§Ϋ”Τς¥ΪΥΆ ±ΖΔ…ζΒΡΝ”Μ·ΓΘΫχ»κΫ” ’Μζ”–‘¥≤ΩΖ÷ΒΡ–≈Κ≈ΖβΉΑ‘Ύ…η±ΗΡΎ≤ΩΘ§“ρ¥Υ Ι”Ο¥ΪΆ≥ΦΦ θ «≤ΜΡήΜώΒΟ’β–©–≈Κ≈ΒΡΘ§ΒΪ «Θ§±Ί–κΤάΙάΤδ―έΆΦΚΆΤδΥϋΧΊΒψΓΘ ΫβΨωΖΫΑΗ « Ι”ΟDSP¬Υ≤®ΤςΘ§ΡΘΡβΫ” ’ΜζΡΎ≤Ω¬Υ≤®ΤςΒΡ–ß”ΠΓΘ”ΟΜßΩ…“‘Α―‘Ύ…ηΦΤ±Μ≤β…η±Η¬Υ≤®Τς ± Ι”ΟΒΡœύΆ§ΒΡœΒ ΐΦ”‘ΊΒΫ Ψ≤®Τς÷–ΓΘ‘Ύ”Π”Ο¬Υ≤®ΚσΘ§ Ψ≤®Τς”ΟΜßΩ…“‘ΧΫ≤β δ»κ’κΫ≈Θ§Ά§ ±≤ιΩ¥–≈Κ≈Θ§ΨΆœσ‘ΎΡΎ≤ΩΧΫ≤β…η±Η“Μ―υΓΘ’β÷÷ΓΑ–ιΡβ≤β ‘ΒψΓ±Ϋ“ ΨΝΥΫ” ’Μζ¬Υ≤®ΚσΒΡ–≈Κ≈Θ§Φ¥ ΙΈοάμ≤β ‘Βψ «…η±ΗΖβΉΑ…œΒΡ“ΜΗω’κΫ≈ΓΘ’βΗωΙΐ≥Χ≥ΤΈΣΓΑΖ¥«ΕΓ±ΓΘ Ω…“‘ Ι”ΟΜυ”ΎDSPΒΡ¬Υ≤®ΤςΘ§ Βœ÷Β±«Α Ή―ΓΒΡ–≈Κ≈¬Υ≤®ΦΦ θΘ§Αϋά®≈–Ε®Ζ¥άΓΤΫΚβ(DFE)ΓΘΉ®”–ΒΡDFE¬Υ≤®Τς «Β±«Α–μΕύΗΏΦΕ¥°–– ’ΖΔΜζ÷– Ι”ΟΒΡΦΦ θΓΘ Ψ≤®ΤςΡΎ≤ΩΒΡ ΐΉ÷¬Υ≤®ΤςΩ…“‘Ϋ” ή»Έ“βFIR¬Υ≤®œΒ ΐΘ§Ω…“‘Α―DFEœΒ ΐΩλ’’Φ”‘ΊΒΫ Ψ≤®Τς÷–Θ§Ε‘DFE–≈Κ≈Ϋχ––ΚσΤΎ¥ΠάμΓΘ ΜΙΩ…“‘ Ι”ΟDSP¬Υ≤®Θ§ ΙΝ§Ϋ”ΒΫ±Μ≤β…η±ΗΒΡΦ–ΨΏΚΆΒγά¬ΒΡ”Αœλ¥οΒΫΉν–ΓΓΘΆ®ΙΐΦλΕ®ΜρΫ®ΡΘΦ–ΨΏΘ§Α―–≈œΔΉΣΜΜ≥…œύ”ΠΒΡ¬Υ≤®œΒ ΐΘ§ Ψ≤®Τς”ΟΜßΩ…“‘ΩΣΖΔΓΑΒς≥ωΓ±Άβ≤ΩΒΞ‘ΣΒΦ÷¬ΒΡœύ“ΤΚΆ–≈Κ≈Ν”Μ·ΒΡ¬Υ≤®ΤςΓΘ Ι”ΟDSP‘ω«Ω≤…Φ·–‘Ρή ΐΉ÷–≈Κ≈¥ΠάμΦΦ θΩ…“‘‘Ύ’ϊΗω Ψ ≤®Τς≤…Φ·œΒΆ≥÷–ΧαΙ©–μΕύΚΟ¥ΠΘ§Αϋά®‘ω«ΩΤΒ¬ ΚΆœύΈΜœλ”ΠΓΔΆ®ΒάΤΞ≈δΓΔΧΫΆΖœΒΆ≥–‘ΡήΓΔ–≈‘κ±»––ΈΣΦΑΤδΥϋΙΊΦϋΧΊΒψΓΘ Ω…“‘ Ι”ΟΜυ”ΎDSPΒΡΆ®Βά–‘Ρή‘ω«ΩΙΠΡήΘ§ Βœ÷“λ≥ΘΤΫΧΙΒΡΖυΕ»œλ”ΠΚΆœύΈΜœΏ–‘Ε»ΓΘ‘Ύάμœκ«ιΩωœ¬Θ§ Ψ≤®ΤςΒΡΖυΕ»œλ”Π‘ΎΤδ¥χΩμΗ≤Η«ΒΡ’ϊΗωΤΒ¬ ΖΕΈßΡΎΜα±Θ≥÷≤Μ±δΘ§ΟΜ”–Ζε÷ΒΜρ‘ίΫΒΓΘ‘Ύ¥ΪΆ≥ Ψ≤®Τς≤…Φ·œΒΆ≥÷–Θ§’β÷÷άμœκΉ¥Χ§ «≤ΜΡή Βœ÷ΒΡΘ§ΒΪΆ®Ιΐ Ι”ΟDSPΘ§Ω…“‘ Ι≤ΜΙφ‘ρΉ¥Χ§ΤΫΜ§Μ·Θ§‘Ύ’ϊΗω¥χΩμ÷–ΤΫΚβœλ”ΠΓΘ’β÷÷ΖΫΖ®ΒΡΚΟ¥Π «Ω…“‘÷±ΒΫ÷ΗΕ®¥χΩμΦΪœόΘ§ Βœ÷Ϋή≥ωΒΡ≤βΝΩΨΪΕ»ΓΘάΐ»γΘ§‘Ύ12 GHz Ψ≤®Τς÷–Θ§Ω…“‘≤ΕΜώΤΒ¬ ΈΣ10 GHzΒΡ–≈Κ≈Θ§ΤδΨΪΕ»Μυ±Ψ…œ”κ100 MHzΤΒ¬ ΒΡ–≈Κ≈œύΆ§ΓΘ‘Ύ’ϊΗωΖΕΈßΡΎΘ§–≈Κ≈±Θ’φΕ»Μα±Θ≥÷“Μ÷¬ΓΘ DSP¥ΠάμΜΙ”–÷ζ”ΎΗΡ…Τ“«ΤςΒΡΤΒ¬ ΙωΫΒΧΊΒψΓΘ’βάοΒΡΡΩ±ξ «ΩΊ÷Τœλ”Πœ¬ΫΒΒΡΥΌΕ»Θ§“‘‘Ύ±Θ¥φΥ≤Χ§œλ”ΠΦΑΫΒΒΆ¥χΆβ‘κ…υ÷°Φδ Βœ÷ΉνΦ―ΤΫΚβΓΘΙωΫΒΧΪΜΚΜαΒΦ÷¬ΗϋΕύΒΡΗΏΤΒ‘κ…υ≥…Ζ÷Ϋχ»κ≤βΝΩΤΒΕΈΓΘΙωΫΒΧΪΦ±Ω…ΡήΜα Ι÷ß≥÷ΉΦ»ΖΤΫΜ§Υ≤Χ§œλ”ΠΥυ–ηΒΡΗΏΤΒ¬ ΖΔ…ζΥΞΦθΓΘDSPΩ…“‘Ζ«≥ΘΉΦ»ΖΒΊΩΊ÷ΤΙωΫΒΒΡΧχ±δ―ΊΘ§‘Ύ‘κ…υ“÷÷ΤΚΆΥ≤Χ§œλ”Π÷°Φδ Βœ÷Ήν”≈ΤΫΚβΘ§ Βœ÷Ζ«≥ΘΗΏΒΡ–≈Κ≈±Θ’φΕ»ΓΘ ΜΙΩ…“‘ Ι”ΟDSPΘ§ΧαΙ©Ζ«≥ΘΉΦ»ΖΒΡΆ®ΒάΤΞ≈δΘ§Τδ÷–Α―ΟΩΧθΆ®Βά–ΘΉΦΒΫΆ§―υΒΡάμœκœλ”ΠΧΊΒψΓΘ‘ΎΕύ¬Ζ¥°––ΦΦ θ…œ÷¥––Έ±≤νΖ÷≤βΝΩΜρΆ®ΒάΒΫΆ®Βά≤βΝΩ ±Θ§‘ΎΕύΧθΆ®Βά÷–ΜώΒΟΦΗΚθΆξ»ΪœύΆ§ΒΡΫΉ‘ΨΫχœλ”ΠΨΏ”–ΦΪΤδ÷Ί“ΣΒΡ“β“εΓΘ“≤Ω…“‘ Ι”Ο’β–©ΦΦ θΘ§±Θ÷ΛΕύΧ®“«Τς÷°Φδ Βœ÷ΉΦ»ΖΒΡΆ®ΒάΤΞ≈δΓΘ ΜΙΩ…“‘‘ΎΧΫ≤β–≈Κ≈¬ΖΨΕ÷– Ι”ΟDSPΘ§Νν Ψ≤®ΤςΩΦ¬«œύ”Π≤νΖ÷ΧΫΆΖΦΑΤδΗΏ¥χΩμΩ…≤π–ΕΦβΕΥΒΡΧΊΒψΓΘ ’βάοΘ§DSPΕΈΉςΈΣ±ξ≥ΤΤΫΚβ¬Υ≤®Τς Ι”ΟΘ§ΤδΉ®”Ο”ΎΧΫΆΖ¬ΖΨΕΘ§”κ“‘«Αœύ±»Θ§ΗϋΫτΟήΒΊΑ―ΧΫΆΖ”––ßΦ·≥…ΒΫ Ψ≤®ΤςœΒΆ≥÷–Θ§±Θ÷ΛΧΫΆΖΚΆ Ψ≤®ΤςœύΫαΚœΘ§ Βœ÷ΉνΤΫΧΙΒΡΤΒ¬ œλ”ΠΓΘ ΉήΫα ΥφΉ≈ΟΩΟκΦΗ«ß’ΉΈΜΒΡ¥°––ΉήœΏ±ξΉΦΒΡ≥ωœ÷Θ§–≈Κ≈Άξ’ϊ–‘‘Ύ’ϊΧεœΒΆ≥–‘Ρή÷–ΒΡ÷Ί“Σ–‘’ΐ‘Ύ≤ΜΕœΧαΗΏΓΘ–¬“Μ¥ζΗΏ–‘Ρή≤β ‘“«ΤςΧαΙ©ΝΥΉψΙΜΗΏΒΡ¥χΩμΚΆ≤…―υ¬ Θ§÷ß≥÷Η…ΨΜΓΔΉΦ»ΖΒΊ≤ΕΜώΗΏΥΌ¥°––≤®–ΈΧΊΒψΚΆ―έΆΦΘ§¬ζΉψΝΥ¥°––ΉήœΏΩΣΖΔ»Υ‘±ΒΡ–η«σΓΘ”…”Ύ≥§ΒΆΡΎ≤ΩΕΕΕ·Θ§’β–©ΙΛΨΏΩ…“‘‘ΎΕ‘≤βΝΩ”ΑœλΉν–ΓΒΡ«ιΩωœ¬Θ§≤βΝΩ–≈Κ≈ΕΕΕ·ΓΘ¥ΥΆβΘ§”…”Ύ–¬ΒΡΡΎ÷Ο¬Υ≤®ΙΛΨΏΘ§ Ψ≤®ΤςΩ…“‘¥”ΫαΙϊ÷–œϊ≥ΐ≤βΝΩ¬ΖΨΕΒΡ”ΑœλΘ§’β’ΐ≥…ΈΣ¥°––ΉήœΏ±ξΉΦ÷–ΗϋΦ”≥ΘΦϊΒΡ“Σ«σΓΘ’β–©DSP¬Υ≤®Τς“―Ψ≠≥…ΈΣ≤βΝΩΗΏΥΌ ΐΉ÷…η±Η÷–≤ΜΩ…»±…ΌΒΡ…η±ΗΘ§ΧΊ±π «≤βΝΩΒ±«ΑΦΤΥψΤΫΧ®ΚΆΆχ¬γΤΫΧ®÷– Ι”ΟΒΡ¥°––‘ΣΦΰ ±ΓΘ’ΐ»γ±ΨΈΡΥυ≤ϊ ωΒΡΡ«―υΘ§Ω…“‘ Ι”ΟDSPΙΛΨΏΘ§œϊ≥ΐΧΫΆΖΚΆΦ–ΨΏΒΡ”ΑœλΘ§‘ –μ…ηΦΤ»Υ‘± Ι”ΟΓΑ–ιΡβ≤β ‘ΒψΓ±Θ§≤ιΩ¥…ηΦΤ÷–≤ΜΡήΫ”»κΒΡΫΎΒψ÷–≥ωœ÷ΒΡ–≈Κ≈ΓΘ |

Άχ”―Τά¬έ