例说FPGA连载41:DDR控制器集成与读写测试之DDR2 IP核接口描述

发布时间:2016-10-27 16:13

发布者:rousong1989

|

例说FPGA连载41:DDR控制器集成与读写测试之DDR2 IP核接口描述 特权同学,版权所有 配套例程和更多资料下载链接: http://pan.baidu.com/s/1c0nf6Qc

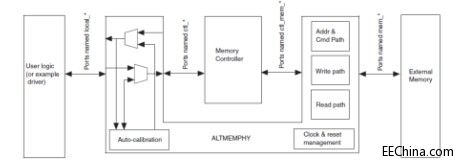

如图4.13所示,这是DDR2 IP核与外部接口的功能框图。

图4.13 DDR IP核功能框图 ● 图左侧为用户逻辑(User logic),它与DDR2 IP核的接口通常命名为“local_*”;图右侧为FPGA外部的DDR2芯片,它与DDR2 IP核的接口通常命名为“mem_*”。 ● DDR2 IP核内部分两个部分,即图示的“ALTMEMPHY”和“存储控制器(Memory Controller)”,正如图中所示,它们各有分工。存储控制器产生DDR2芯片实际读写操作需要的时序;ALTMEMPHY有两部分功能,一个功能是对DDR2做自动校正(Aoto-Calibration),另一个功能是实现DDR2所需的物理接口。 ● DDR2的自动校正是在初始化阶段进行的,此时ALTMEMPHY断开用户逻辑和存储控制器之间的接口,ALTMEMPHY产生存储控制器所需的DDR2读写控制,直到校正完成。在初始化过后,ALTMEMPHY将不再需要控制存储控制器,而是一直保持用户逻辑和存储控制器的连通。 ● 另外,图中未明确示意,实际上这个DDR2 IP核还包括了一个PLL,用于时钟的管理。 现在我们来看ddr2_controller模块例化的接口。这里可以分为三大类,第一类为系统类接口,主要是一些系统或PLL的复位、时钟等接口;第二类为带“local_*”的接口,是DDR2 IP核与用户逻辑间的接口;第三类为带“mem_*”的接口,是DDR2 IP核与FPGA外部DDR2芯片的接口。 对于第一类接口,功能描述如表4.1所示。 表4.1 DDR2 IP核系统接口列表

注:方向是相对DDR2 IP核而言的。 对于第二类带“local_*”的用户逻辑接口,功能描述如表4.2所示。 表4.2 DDR2 IP核本地接口列表

注:方向是相对DDR2 IP核而言的。 第三类是带“mem_*”的DDR2芯片接口,前面已经给出基本的功能描述,这里不再赘述。DDR2的在我们设计中例化的接口映射代码如下所示。 //////////////////////////////////////////////////// //DDR2 controller and phy IP core ddr2_controller ddr2_controller_inst ( .local_address(local_address), .local_write_req(local_write_req), .local_read_req(local_read_req), .local_burstbegin(local_read_req | local_write_req), .local_wdata(local_wdata), .local_be(8'hff), .local_size(3'd1), .global_reset_n(sys_rst_n), .pll_ref_clk(clk_100m), .soft_reset_n(1'b1), .local_ready(local_ready), .local_rdata(local_rdata), .local_rdata_valid(local_rdata_valid), .local_refresh_ack( ), .local_init_done(local_init_done), .reset_phy_clk_n(reset_phy_clk_n), .mem_odt(mem_odt), .mem_cs_n(mem_cs_n), .mem_cke(mem_cke), .mem_addr(mem_addr), .mem_ba(mem_ba), .mem_ras_n(mem_ras_n), .mem_cas_n(mem_cas_n), .mem_we_n(mem_we_n), .mem_dm(mem_dm), .phy_clk(phy_clk), .aux_full_rate_clk( ), .aux_half_rate_clk( ), .reset_request_n( ), .mem_clk(mem_clk), .mem_clk_n(mem_clk_n), .mem_dq(mem_dq), .mem_dqs(mem_dqs) ); |

网友评论