Xilinx FPGA入门连载39:SRAM读写测试之功能仿真

发布时间:2015-12-23 14:40

发布者:rousong1989

|

Xilinx FPGA入门连载39:SRAM读写测试之功能仿真 特权同学,版权所有 配套例程和更多资料下载链接: http://pan.baidu.com/s/1jGjAhEm

打开文件夹sp6ex15下的ISE工程。 如图所示,切换到“Design à Simulation”界面。鼠标选中“vtf_sp6.v”文件。

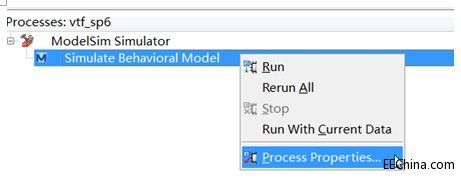

此时,在“Processer:vtf_sp6”下,选择“SimulateBehavioral Model”,然后点击鼠标右键,弹出菜单中选择“ProcessProperties…”。

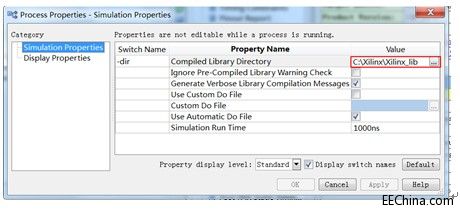

如图所示,确认设置好在安装Modelsim过程中编译好的ISELibrary路径。设定完成后点击“OK”回到ISE主界面。

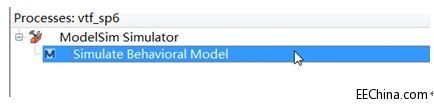

如图所示,双击“Simulate Behavioral Model”开始仿真。

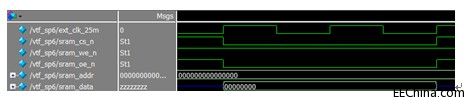

接着,在Modelsim大家就要充分发挥自学能力了,打开Wave,自己豆鼓捣鼓,不久我们就可以看到,写SRAM的时序如下所示。

读SRAM的波形如下所示。

|

网友评论