运放平衡电阻的理解

发布时间:2015-11-30 11:41

发布者:designapp

关键词:

运放平衡电阻

|

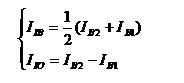

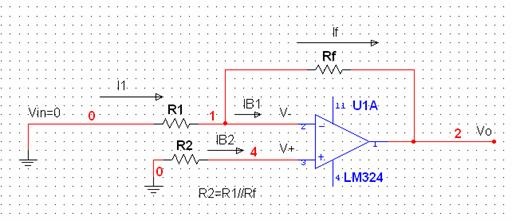

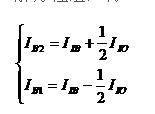

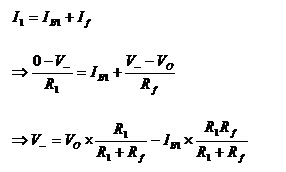

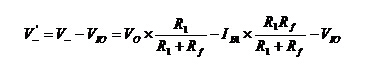

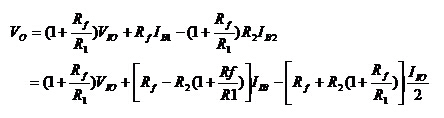

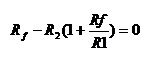

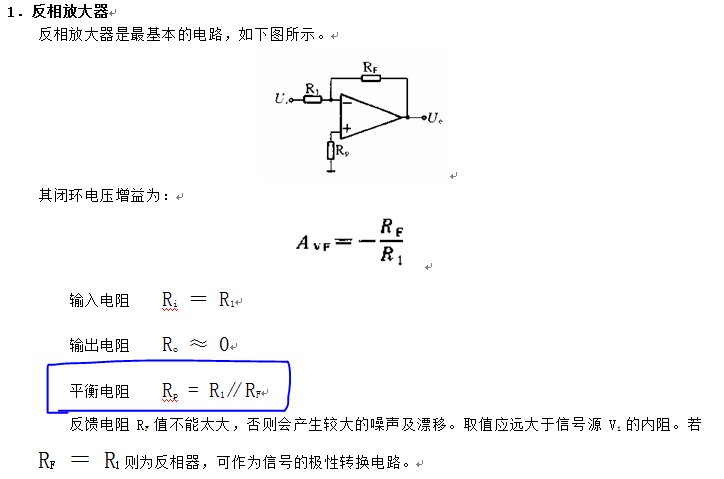

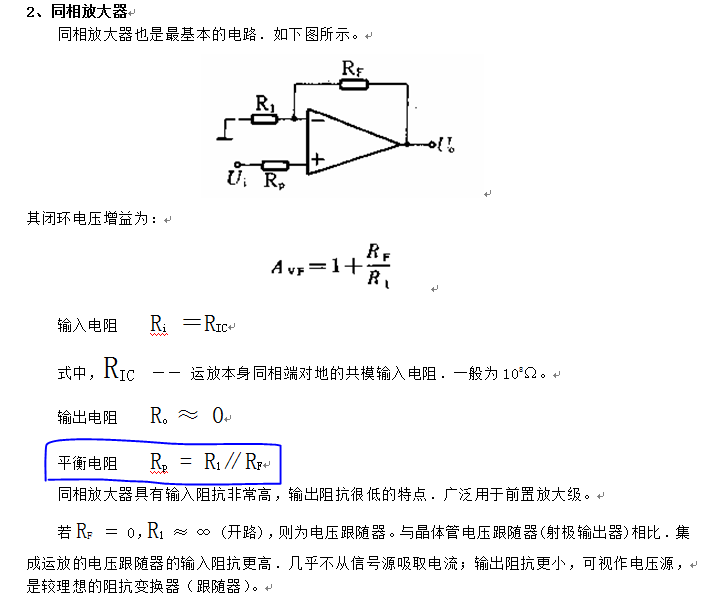

简介:平衡电阻的目的是为了减小运放输入偏置电流在电阻上形成的静态输入电压而带来误差详细看书。(减少失调电压) 当运放的输入偏置电流较小,或信号较大,其影响可以忽略时,可以不用平衡电阻。 R2=R1//Rf--------------------平衡电阻的计算式,反相臂上的电阻的并联=同相臂的电阻 R2=R1//Rf 若运放为理想运放,输入为0时,则:  但实际运放有失调电压(VIO),失调电流(IIO),输入偏置电流(IIB)。依据失调电流,输入偏置电流的定义,有:   解方程组,得:  在反相端用KCL,有:  考虑到失调电压,实际反相端电压为:  而:  将所有参数代入,解得:  当R2=R1//Rf时,  此时由输入偏置电流IIB产生的失调电压为0。 运放输入端所接电阻要平衡,目的是使运放的偏置电流不会产生附加的失调电压。但有些电路对失调电压要求并不高。例如交流音频放大器,有些运放偏置电流很小,即使输入端电阻不平衡也不会对失调电压产生什么影响,这些电路就可以不要求输入端电阻平衡。尤其是现在基于CMOS工艺的运放,输入偏置电流都是几个pA,加不加平衡电阻的影响就微乎其微了   |

网友评论