Xilinx FPGA入门连载29:基于Chipscope的超声波测距调试之板级调试

发布时间:2015-11-29 18:07

发布者:rousong1989

|

Xilinx FPGA入门连载29:基于Chipscope的超声波测距调试之板级调试 特权同学,版权所有 配套例程和更多资料下载链接: http://pan.baidu.com/s/1jGjAhEm

接下来我们将进行板级调试,看看用Chipscope中采集到的ECHO波形到底如何。 如图所示,首先在“Design à Implementation”下选中工程顶层代码文件sp6.v,然后双击“Processes”下的“Analyze Design Using Chipscope”。

随后弹出“ChipScope Pro Analyzer”的界面如图所示。

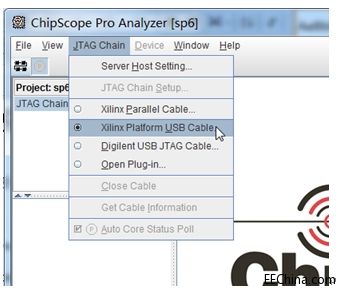

此时,需要连接好SF-SP6开发板的下载线,并给它供电。当然了,超声波测距模块也一定要连接到板子上。 如图所示,点击菜单“JTAG Chain”,选中下载线为“XilinxPlatform USB Cable”。

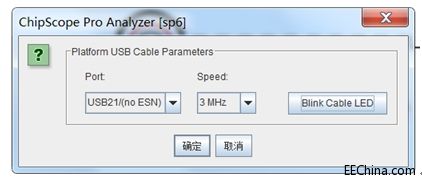

随后弹出如图所示的对话框,点击“确定”。

紧接着又弹出如图所示的菜单,点击“OK”。

如图所示,此时“Project:sp6 à JTAG Chain”下面出现了两个设备,我们找到“DE:0 MyDevice0 (XC6SLX9)”这一行,右键单击后弹出菜单中选择“Configure…”。

如图所示,在弹出的配置页面中,我们点击“Select New File”按钮,打开当前工程所在路径下的sp6.bit文件。加载完成后,我们直接点击“OK”。此时将会把sp6.bit文件烧录到当前的FPGA在线运行。

如图所示,此时的“Project:sp6 à JTAG Chain à DE:0 MyDevice0 (XC6SLX9)”下出现了更多的菜单项。

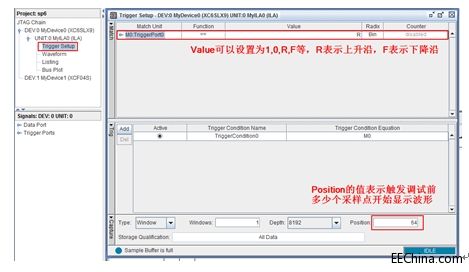

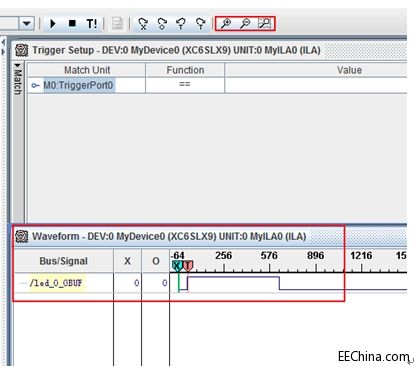

如图所示,双击“Trigger Setup”,然后在右侧中可以设定触发条件。我们这里设定M0:TriggerPort0 == R,即上升沿触发。为了标语观察,我们也设置“Position”为64。

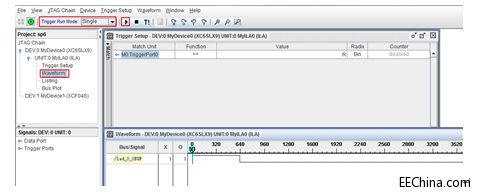

如图所示,双击“Project:sp6 à JTAG Chain à DE:0 MyDevice0 (XC6SLX9)”下的“Waveform”项,然后设置“TriggerRun Mode”为“Single”,接着点击开始按钮就可以开始采集了。

如图所示,我们采集到的波形可以通过菜单上的放大或缩小按钮进行缩放。

如图所示,大家可以通过在超声波测距模块的不同距离放置障碍物(比如一本比较平整的图书),采集到的波形会存在不同的高脉冲宽度。

|

网友评论