使用 PlanAhead Design 工具提高设计性能

发布时间:2010-7-19 14:32

发布者:conniede

|

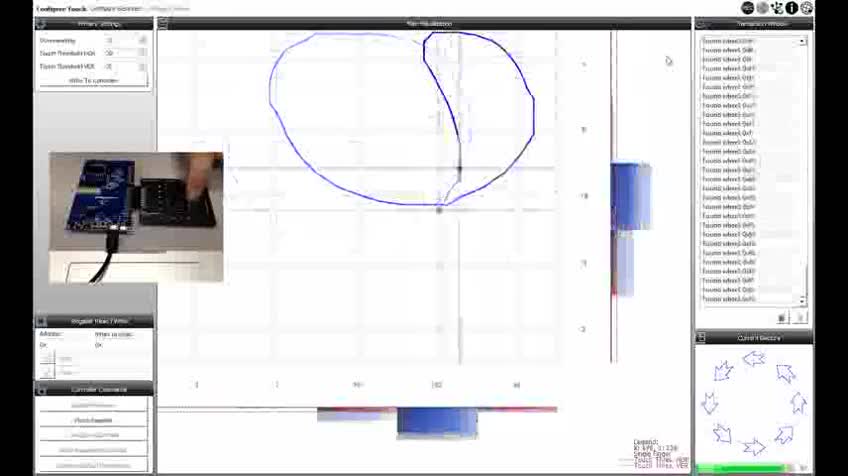

PlanAhead 软件提供了一种解决方案 越来越多的客户在赛灵思® PlanAhead™ 设计分析工具提供的层次化设计方法学中找到解决方案。PlanAhead 软件为 FPGA 设计流程增加了可视性和控制。通过解决物理方面(介于逻辑综合和实现工艺之间)的问题,您可在您的设计结果中实现性能的提高。 虽然先进的 FPGA 综合产品为几百万门设计提供极高的自动优化水平,许多设计者仍需要具有更多启发性的技术,以达到最佳性能目标。通过提供早期分析和布局规划 (floorplanning)功能,PlanAhead 设计工具可以施加物理约束,以帮助控制设计的初始实现。实现后,PlanAhead 软件可以分析布局和时序结果,以改进用于完成设计的布局规划。您可以使用来自导入结果的物理约束,在后续实现尝试期间锁定布局。这些约束可用于创建可重用 IP,连同锁定布局,一同用于其它设计。 PlanAhead 设计方法提供了性能、生产力以及结果的可重复性。凭借其层次化设计流程,PlanAhead 软件可让您减少运行 PAR 然后返回 RTL 与综合的反复次数。相反,您可以分析设计并在实现之前解决物理方面的问题。 更少的时间,更快的结果 PlanAhead 用户通常可以实现 10-15% 的性能提升,有些用户甚至可以实现更高。此外,设计者还发现他们可以在一个紧凑的器件中额外加入 10% 的逻辑。更快的性能与更高的利用率的结合意味着可以使用更小更便宜的器件,或者以更低的速度等级实现设计目标。 PlanAhead 设计工具可在缩短总设计时间的同时,还在结果中增加一定的一致性水平。通过利用以前的布局规划或增量设计技术,您可以以更少的时间执行设计反复,实现可重复的结果。您还可以利用成功结果,将它们锁定下来或在其它设计中重用。 解决真正棘手的性能问题所需要的绝不仅仅是增加新的菜单项或脚本能力。PlanAhead 软件通过使用各种视图(见图 1)展示设计数据,提供了一个完整的环境,使该层次化方法实现交互并易于使用。这些独立的视图可以相互结合使用,从而允许您快速识别和浏览关键设计对象和信息。  图 1:PlanAhead 软件提供了设计的不同视图,以显示物理层次、属性、网表与约束、器件封闭引脚、原理图及更多。 可视化确定性能瓶颈 PlanAhead 环境通过显示 I/O 互连和物理块(或 “Pblock”)网束 (net bundle),提供了洞察设计数据流的能力。您可以根据信号数量控制网束的颜色和线厚。这使您能容易地在贯穿设计的整个数据流中确定具有大量连接的 Pblock。然后您可以采取校正措施,避开布线拥塞故障点,并将具有大量连接的 Pblock 相近放置或将它们合并。 您还可显示时钟区,并在布局规划时使用它来优化各个时钟或最大程度地降低器件中的功耗。通过将时钟隔离到专门的时钟区,它们可以运行得更快,并消除了为其它时钟区供电的需要。 您可以在设计过程中的各个阶段使用 PlanAhead 设计工具的分析和探测环境。最初,您可以在实现之前分析设计。PlanAhead 软件提供了一个静态时序引擎 TimeAhead,用于研究设计在时序方面的可行性。您还可以通过调整纯逻辑延迟,在不进行互连的情况下,使用估计的布线延迟执行分析。这可以让您看清楚设计中存在多大的时序容差。 然后您可以在 PlanAhead 环境中编辑和精调时序约束。这些相同的分析结果可以帮助确定哪些逻辑应组合在一起并进行布局规划。针对布局规划,您可对路径进行逻辑排序、组合和选择,还可以使用同一 TimeAhead 环境处理从 TRCE 导入的时序结果,TRCE 是赛灵思 ISE™ 软件中的时序评估工具。 您可以查看和修改为设计指定的时序约束。您可以在编辑器中将所有 ISE 时序约束定义为新约束。这可以使约束指定变得更容易,因为您不必再记住专门的约束格式了。您可以在运行任何 ISE 实现工具之前,将其与 TimeAhead 一起使用以验证和优化约束集。 PlanAhead 设计工具提供了可视辅助,以帮助您理解物理实现结果。设计规则检查 (DRC) 功能可帮助您及早捕获错误。它还会对未正确利用某些器件资源(如 Virtex™-4 FPGA 中的 XtremeDSP™ 切片或 RAM)的设计进行标记。 通过将问题区域可视化,您可以在 RTL 侧或物理实现侧快速解决问题,而不必继续重复进行 RTL 与综合。您可以对各个逻辑模块进行选择性地高亮显示,以更好地了解它们放置的位置,以及创建在逻辑最集中区域的Pblock。您可以高亮显示故障时序路径,以可视化和了解您的设计中发生了什么物理问题。 PlanAhead 软件包含了量度图 (metric map),以快速确定设计的故障区域(图 2)。这些可能与时序或利用率有关。这对您在试图确定设计中要关注的区域以实现逻辑压缩或时序连接性时会很有用。  图 2:量度图提供了设计中各种潜在问题区域的热量度显示。当前量度包括 Pblock 和布局后设计级的利用率和时序检查。 PlanAhead 设计工具允许您研究设计中的连接性。您在设计中选择一个特定的网络、Pblock 或实例后,可以通过单击鼠标高亮显示所有连接到选定元素的网络。 在选择一个实例或 Pblock 后,所有连接到该元素的网络都将被高亮显示。这一过程可以继续,以选择和扩展逻辑锥形。运行“显示连接性”将高亮显示连接到选定实例的下一级网络。这是一种选择从某个特定实例或 I/O 端口开始的逻辑锥区的简易方法,从而可真正实现对设计层次优势的利用。 ... 然后解决性能问题 整个想法是要提供一个综合环境,以分析时序问题并轻松约束该逻辑以避免或纠正该问题。您可以使用来自 TimeAhead 或 TRCE 的时序结 果进行布局规划,通过帮助确定哪些逻辑应组合在一起并进行布局规划来进行更好的性能设计。 关键路径通常穿越逻辑层次。PlanAhead 软件支持独立于逻辑层次的物理层次,从而使您可将设计中任意位置的逻辑组合在一起并有效地进行布局规划。 PlanAhead 软件还提供了资源利用估算功能,以帮助确定 Pblock 的尺寸和形状。同样这些统计资料还可报告时钟信息、供应链和 PRM 适应尺寸以及各种其它有用信息。 PlanAhead 设计工具提供了自动布局能力,如基于逻辑层次的自动分区和自动 Pblock 尺寸确定与放置。由于使用单个 Pblock 矩形来包含所需的器件资源通常很困难,因此可以使用多个矩形创建非矩形-线性形状。PlanAhead 软件还允许您在 Pblock 内创建 Pblock,或创建“子”Pblock,以帮助更好地维护设计层次。 器件容量可通过压缩 Pblock 的逻辑进行提高。您可以使用以下两种方法中的一种来实现。一种方法是使用称为 COMPRESSION 的赛灵思 AREA_GROUP 属性。AREA_GROUP 是一种设计实现约束,支持将设计分成用于映射、打包、布局和布线的物理区域。使用 COMPRESSION 属性将导致 ISE Mapper 将无关的逻辑打包成未使用的 CLB 站。使用它时请小心,因为它会对时序产生副作用。 改善性能的最佳策略是压缩非时序关键型逻辑,从而在器件中腾出更多空间用于时序关键型逻辑。第二种选项是使用 PlanAhead 功能对在 Pblock 上独立运行 PAR。 您可以持续缩减 Pblock 尺寸,直到 PAR 失败。这将尽可能紧地压缩和打包块内逻辑,以腾出器件空间。 一个 Virtex-4 布局规划示例 PlanAhead 设计工具可允许您轻松地导入布局和时序结果。通过该信息,您可以查看和排序时序报告中的关键路径,并使用原理图或器件视图对路径进行可视化显示。一旦确定故障路径,您可以高亮显示布局规划中的所有路径实例,以确定原理图视图中的所有路径实例。 图 3 显示了一个针对 Virtex-4 FX140 器件的设计的布局规划。在显示中,我们高亮显示了一条特定路径上未能满足时序要求的触发器。由于它们在器件中分布太广,设计实现产生了无法接受的长延迟。由于在 Virtex-4 FPGA 中存在大量的时序域,因此这是一种普遍情况。  图 3:初始 Virtex-4 FPGA 布局规划,高亮显示开始未满足时序的路径 通过选择这些触发器中的每个触发器,并将它们限制到单个 Pblock 中,您可以调节和优化该 Pblock的尺寸和位置,从而缩短关键路径的延迟,如图 4 所示。必要时,您甚至可以创建嵌套 Pblock,从而创建一种子/主层次来进一步约束子模块,以获得额外的性能提升。根据捕获逻辑的资源需求,您可以将关键逻辑锁定位置,以实现对必要资源的最佳访问。  图 4:在对与该路径相关的所有基元进行约束后,您可以对 Pblock 进行优化,以使该路径达到所需的时序要求。 结论 您可访问 www.xilinx.com/planahead来下载 PlanAhead 软件的免费评估版本。该 30 天评估版使您可完全获得所有 PlanAhead 特性和功能性。该站点还允许您查看产品演示,下载白皮书,或只是了解更多信息。赛灵思还提供 PlanAhead QuickStart!,可在项目的最关键阶段提供特别的服务支持。通过该服务,赛灵思将派遣一名 QuickStart! 工程师到您的现场进行为期一周的辅助,他将培训和帮助您的团队按时完成项目和如何充分利用您所选择的赛灵思器件。 这一高度个性化服务使您能制定最能满足您的设计团队需要的培训计划。通过确保团队拥有所需的技能,它将有助于避免项目拖延。它还有助于您保持一个更有效率且热情高涨的团队。 |

网友评论