FPGA实战演练逻辑篇62:CMOS摄像头接口时序设计2实际分析

发布时间:2015-8-14 11:05

发布者:rousong1989

|

CMOS摄像头接口时序设计2实际分析(特权同学版权所有) 本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有) 配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 好,分析完理想的pin2reg模型,下面我们看看要复杂得多的实际情况。(特权同学,版权所有) 先看看CMOS Sensor的datasheet中提供的时序波形和相应的建立、保持时间要求。如图8.46所示。(特权同学,版权所有)

图8.46 CMOS Sensor时序波形 波形中出现的时间参数定义如表8.2所示。(特权同学,版权所有) 表8.2 CMOS Sensor时序参数定义

我们可以简单分析下这个datasheet中提供的时序波形和参数提供了一些什么样的有用信息。我们重点关注PCLK和D[7:0]的关系,HREF其实也可以归类到D[7:0]中一起分析,他们的时序关系基本是一致的(如果存在偏差,也可以忽略不计)。这个波形实际上表达的是从Sensor的芯片封装引脚上输出的PCLK和D[7:0]的关系,如图8.47所示。而在理想状况下,经过PCB走线将这组信号连接到其他的芯片上(如CPU或FPGA),若尽可能保持走线长度,在其他芯片的引脚上,PCLK和D[7:0]的关系基本还是不变的。那么,对于采集端来说,用PCLK的上升沿去锁存D[7:0]就变得理所当然了。而对于FPGA而言,从它的引脚到寄存器传输路径上总归是有延时存在的,那么PCLK和D[7:0]之间肯定不会是理想的对齐关系。而我们现在关心的是,相对于理想的对齐关系,PCLK和D[7:0]之间可以存在多大的相位偏差(最终可能会以一个延时时间范围来表示)。在时序图中,Tsu和Th虽然是PCLK和D[7:0]在Sensor内部必须保证的建立时间和保持时间关系,但它同样是在Sensor的输出引脚上,必须得到保证的基本时序关系。因此,我们可以认为:理想相位关系情况下,PCLK上升沿之前的Tsu时间(即15ns)到上升沿后的Th时间(即8ns)内,D[7:0]是稳定不变的。同样的,理想情况下,PCLK的上升沿处于D[7:0]两次数据变化的中央。换句话说,在D[7:0]保持当前状态的情况下,PCLK上升沿实际上在理想位置的Tsu时间和Th时间内都是允许的。请大家记住这一点,下面我们需要利用这个信息对在FPGA内部的PCLK和D[7:0]信号进行时序约束。(特权同学,版权所有)

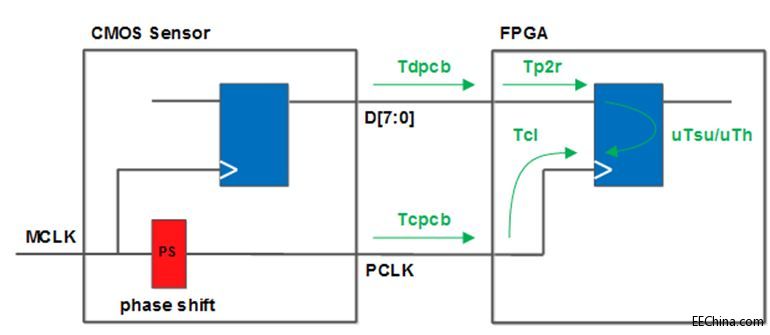

图8.47 CMOS Sensor输出信号模型 明确了PCLK和D[7:0]之间应该保持的关系后,我们再来看看他们从CMOS Sensor的引脚输出后,到最终在FPGA内部的寄存器被采样锁存,这整个路径上的各种“艰难险阻”(延时)。如图8.48所示,这是外部CMOS Sensor和FPGA接口的寄存器路径模型。在这个路径分析中,我们不去考虑CMOS Sensor内部的时序关系,我们只关心它的输出引脚上的信号。先看时钟PCLK的路径延时,在PCB上的走线延时为Tcpcb,在FPGA内部,从进入FPGA的引脚到寄存器的时钟输入端口的延时为Tcl。再看数据D[7:0]的延时,在PCB上的走线延时为Tdpcb,在FPGA内部的引脚到寄存器输入端口延时为Tp2r。而FPGA的寄存器同样有建立时间Tsu和保持时间Th要求,也必须在整个路径的传输时序中予以考虑。(特权同学,版权所有)

图8.48 CMOS Sensor和FPGA连接的寄存器模型 另外,从前面的分析,我们得到了PCLK和D[7:0]之间应该满足的关系。那么,为了保证PCLK和D[7:0]稳定的进行传输,我们可以得到这样一个基本的关系必须满足: 对于建立时间,有: Launch edge + Tdpcb + Tp2r + Tsu 对于保持时间,有: (Launch edge + Tdpcb + Tr2p) -(latch edge + Tcpcb + Tcl) > Th 关于launch edge和latch edge,对于我们当前的设计,如图8.49所示。(特权同学,版权所有)

图8.49 pin2reg的launch edge和latch edge关系 |

网友评论