FPGAКөХҪСЭБ·ВЯјӯЖӘ33ЈәКөКұКұЦУРҫЖ¬өзВ·ЙијЖ

·ўІјКұјдЈә2015-6-5 11:52

·ўІјХЯЈәrousong1989

|

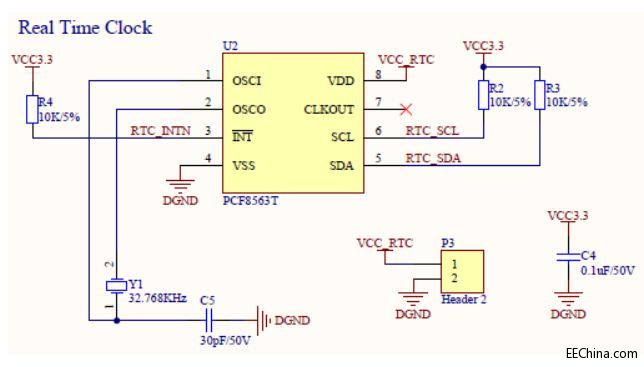

КөКұКұЦУРҫЖ¬өзВ·ЙијЖ ұҫОДҪЪСЎЧФМШИЁН¬С§өДНјКйЎ¶FPGAЙијЖКөХҪСЭБ·ЈЁВЯјӯЖӘЈ©Ў· ЕдМЧАэіМПВФШБҙҪУЈәhttp://pan.baidu.com/s/1pJ5bCtt ИзНј3.76ЛщКҫЈ¬U2КЗТ»ҝЕКөКұКұЦУЈЁRTCЈ©РҫЖ¬Ј¬ёГРҫЖ¬РиТӘНвІҝ№©32.768KHzөДКұЦУҫ§МеЈ¬Хвёцҫ§МеөДХсөҙРиТӘҪиЦъТ»ҝЕ30Pf(8pF)өДөзИЭЎЈёГРҫЖ¬әНFPGAЦ®јдНЁ№эI2CЧЬПЯҪУҝЪҪшРРКэҫЭҙ«КдЎЈёГРҫЖ¬өД№©өзТӘҪиЦъНвІҝБ¬ҪУөДТ»ҝЕЕҰҝЫөзіШЎЈЈЁМШИЁН¬С§Ј¬°жИЁЛщУРЈ©

Нј3.76 КөКұКұЦУҪУҝЪөзВ· U2өДёчёцТэҪЕ¶ЁТеИзұн3.13ЛщКҫЎЈЈЁМШИЁН¬С§Ј¬°жИЁЛщУРЈ© ұн3.13 КөКұКұЦУРҫЖ¬өДТэҪЕ¶ЁТе

|

НшУСЖАВЫ