FPGA的单片机多机串行通信网络

发布时间:2010-4-6 11:06

发布者:李宽

|

引言 随着测控技术的发展,由多单片机构成的测量控制网络在测控领域的应用越来越广泛。单片机之间的数据交换通常采用串行通信方式,连接方式多采用总线拓扑结构。该结构中单片机通过一组数据线相连接,所有单片机共用一组数据线;通信时要对从单片机进行编址,主单片机通过不同的地址来访问从单片机。由于只有一组数据线,那么在同一时间内,主单片机只能和一个单片机进行通信。如果要访问一遍从单片机,那么主单片机要首先发送某一个从单片机的访问命令,等其应答后才能访问下一个从单片机。这样就浪费了大量的时间,降低了测控系统的工作效率。在某些监督计算机控制系统(SCC)和集散型控制系统(DCS)中,主单片机经常需要同时访问从单片机,要求从单片机能同时响应主单片机的访问命令,此时拓扑型总线结构就不能满足要求。 随着电子技术和EDA技术的发展,FPGA技术以其独有的优势,在电子设计领域得到越来越广泛的应用。FPGA具有集成度高、体积小和功耗低等优点,而且还具有用户可编程能力。采用FPGA器件可以大大缩短开发周期,减少资金投入,实现片上可编程系统(SOPC)的设计。同时,测控系统中使用串行扩展通信的趋势越来越突出,但是传统总线拓扑结构较低的响应效率已经不能满足复杂系统的要求。本文的主要目的是基于FPGA设计一个集成16个简单UART(通用异步接收发送设备)的模块,该模块采用VHDL语言描述。主单片机通过并口与FPGA相连,FPGA通过16个UART分别与16个从单片机相连,实现单片机串行通信网络系统。 1 系统硬件总体设计 系统设计要求主单片机能同时控制从单片机,并且能同时采集从单片机上传的信息,进行判断并传送给上位机。主单片机功能主要有: ①与上位机通信,接收上位机命令并解析; ②根据上位机命令,向下控制从单片机; ③监测从单片机中上传的各种指标是否符合要求; ④提供告警显示。 FPGA完成主单片机命令的解复接和从单片机上传信息的复接。从单片机主要功能为接收主单片机通过FPGA下发的命令,完成对设备的控制并上传设备状态,如图1所示。

本设计中使用的单片机为Cygnal公司的C8051F系列单片机,FPGA为Xilinx公司的XC3S100E。C805lF系列单片机是Cygnal公司开发的高端单片机,指令与8051兼容,最高具有25 MIPS的处理能力,同时集成了ADC、DAC、可编程放大器、电压比较器、传感器等丰富的外设, 非常适合应用于测控领域。C8051F系列单片机还具有JTAG接口,方便用户在线调试,极大节省了用户的开发时间。 2 系统实现 2.1主单片机单元设计 主单片机采用C8051F020单片机,该单片机提供2个串口、1个12C接口(SMBus),提供PO~P3或P4~P7的并口。本设计中,设置特殊功能寄存器EMIOCF一0x27,使外部存储器接口工作在地址/数据复用方式,选择高端口P4~P7。设置特殊功能寄存器XBR0=0x15,将串 口UARTO和SMBus映射到PO端口。 C8051F020将FPGA视为外部存储器,通过并口P4~P7进行访问。C8051F020通过SMBus接口连接串行EEPROM,将系统信息实时写入EEPROM,在系统突然掉电后上电时读取EEPR()M内的数据,完成系统掉电保护功能。主单片机连续不停地分析从单片机上传的指令, 判断设备的状态并给出告警显示,同时存入内部缓冲区等待上位机查询。 C8051F020提供串口和网口2种方式与上位机通信,两个接口不能同时使用。网络通信采用网口串u转换模块实现,网口和串U通过组合逻辑电路连接到C8051F020的UART0,如图2所示,实现系统的本地监控和远程监控功能。

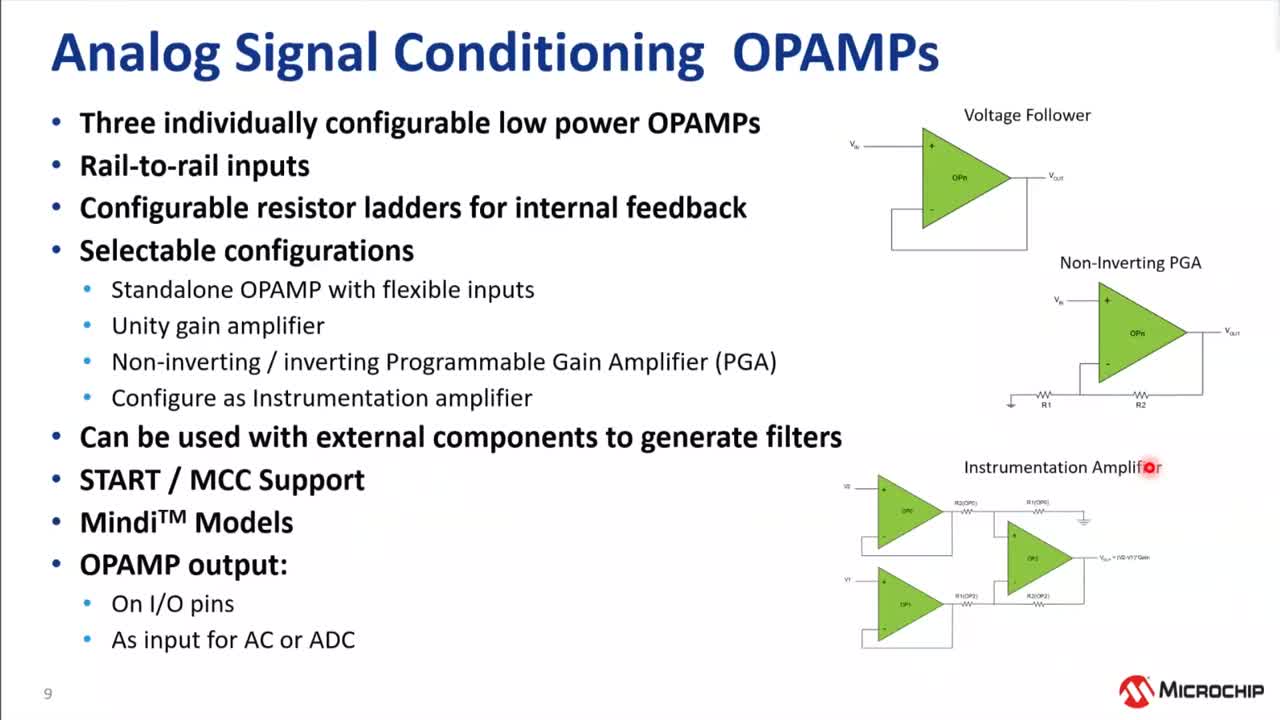

2.2 FPGA单元设计 FPGA的没计是通信网络的核心部分。依据功能要求,FPGA内部划分成四大功能模块:SRAM控制器、发送数据缓冲模块、16个UART模块、接收数据缓冲模块。 发送数据缓冲模块划分成16个RAM区,每个RAM区分别连接1个UART,当发送缓冲模块接收到主单片机下发的控制数据后,启动UART将数据发送至从单片机。接收缓冲区同样分为16个RAM区,发送控制数据后,UART周期性地向从单片机发送状态查询命令,从单片机将最新状态发送至UART模块,UART模块将数据存入接收缓冲模块相应的RAM区。如图3所示。

FPGA内部共有16对读/写和数据总线,分别连接UART和相应的发送缓冲区RAM及接收缓冲区RAM。 FPGA内部模块采用图3 FPGA内部功能模块示意图自顶向下的设计方法,将复杂系统划分为简单系统,然后通过逻辑和接口设计实现各个模块功能。SRAM控制器用于FPGA和C8051F020的接口,负责内部RAM的读写控制。UART负责接收从单片机上传的串行信号,将其并行化后存入接收数据缓冲RAM;另外也负责将发送缓冲RAM中的数据转换成符合RS232协议规范的串行信号发送给从单片机。SRAM控制器和UART模块同样采用自顶向下的方式实现,关于SRAM控制器及UART的FPGA实现方案在参考文献中有详细的论述,本文不再介绍。 FPGA内部系统采用同步有限状态机(FSM)的设计方法实现,FSM负责调配各功能模块之间的协作。状态机采用独热(one—hot)编码,使电路的可靠性和速度有显著的提高。系统状态转移图如图4所示。

2.3通信协议设计 主单片机和上位机的通信速率及FPGA和从单片机的通信速率均设置为38.4 Kbps,可以更精确的控制主单片机与各个从单片机之间的通信时间。通信指令由报头、设备类型、设备号、命令号、命令数据、校验等字段组成。 报头用于通知单片机开始串行通信。设备类型和设备号用于将指令正确传达到相应的设备,命令号用于通知单片机指令,命令数据用于通知单片机具体的功能,校验则采用CRC校验以保证通信的准确性。写入控制命令号为OOH,读取命令号为01H,读取指令命令数据为0字节。通信指令的帧格式如下:

单片机接收到控制命令后,如果接收正确,返回00H,若错误则返回01H。返回帧格式为:

读取指令没有命令数据,帧格式为:

接收后单片机返同帧格式为:

结语 本文介绍了在FPGA上集成多个UART的方法,以此为基础搭建了一个多单片机通信网络。设计中采用FPGA作为串行接口扩展器件与传统器件相比具有功能灵活、扩展性好的特点。通过实验证明,该通信网络相对于传统的总线拓扑网络具有速度快、实时性好的特点,同时该网络可以根据外设需要随意扩展,非常适合应用于监督计算机控制系统和集散控制网络。 参考文献 1. 董加强 提高单片机多机串行通信的一种新方法 [期刊论文] -电工技术2008(6) 2. 陈晓英.任国臣 单片机多机通信系统稳定性的研究 [期刊论文] -单片机与嵌入式系统应用2001(7) 3. 陈寿元 单片机多机通信网络改进及数据通信容错技术 [期刊论文] -山东师范大学学报(自然科学版)2006(2) 4. 汪吉鹏 工业控制技术的应用现状和发展方向 [期刊论文] -潍坊学院学报2002(2) 5. 刘耀.梅大成.于珍珠 QDR SRAM控制器的设计与FPGA实现 [期刊论文] -现代电子技术2007(2) 6. 贾子申.李淑清.王冠雅 基于 FPGA的UART控制器设计 [期刊论文] -电子测量技术2008(3) 作者:天津光电通信技术有限公司 张志利 张晓峰 朱力 来源:单片机与嵌入式系统应用 2009 (3) |

网友评论