串行SPI NOR闪存VS并行NOR闪存

发布时间:2021-2-1 17:18

发布者:宇芯电子

关键词:

串行SPI NOR闪存 , NOR闪存

|

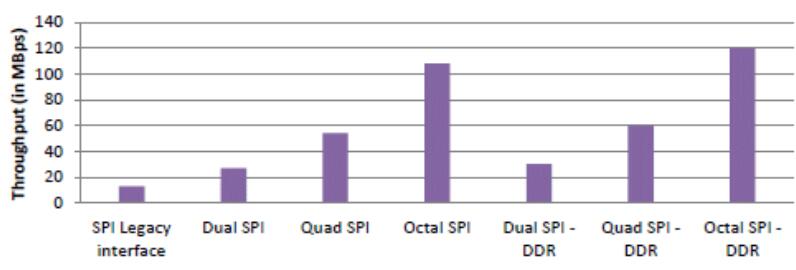

NOR闪存由于其可靠的数据存储而已在嵌入式设备中广泛使用了很长时间。对于某些低功耗应用,串行SPI NOR闪存变得比并行NOR闪存设备更受欢迎。与串行SPI NOR闪存相比,并行NOR闪存具有并行性,因此吞吐量更高。但是随着串行SPI NOR闪存设备中多通道(2-8条并行数据线)支持的出现,它现在在低功耗设备中变得越来越流行。这些闪存设备主要用于嵌入式系统中以存储引导代码,有时还用作存储元素。这些引导设备使用就地执行(在此称为XIP)方法来执行本机存储设备中的代码。XIP方法与代码在执行之前首先从其起始位置移动的方法形成对比。由于无需在执行之前移动代码,XIP方法通常会减少所需的内存组件数量并缩短启动时间。SPI器件的新创新,例如八进制传输格式和DDR操作,使它们能够以极高的速度使用并改善系统性能。本文介绍了可用于利用存储设备提供的XIP功能的系统级别和存储设备策略。 串行VS并行NOR器件 NOR设备有两种主要类型:串行和并行。串行SPI NOR闪存提供通过小引脚数串行接口(例如SPI)的访问。这些器件由于引脚数少且封装尺寸小,因此是针对成本和尺寸受限的应用的。尽管并行NOR设备具有更宽的接口,因此具有更高的性能,但与串行设备相比,它需要更大的封装和更高的成本。这就是为什么串行SPI NOR闪存设备通常出现在空间和功耗受限的设计中的原因,例如手持设备,仪表和传感器,机顶盒(STB)和打印机,本地路由器和硬盘驱动器。并行NOR设备的XIP性能比串行SPI NOR闪存好得多,但是由于其低成本和低功耗,串行SPI NOR闪存设备已在嵌入式系统中变得越来越流行。对于并行NOR,典型带宽在133 MHz时钟上可获得250 MBps,而对于串行SPI NOR闪存,典型速度为108 MHz时钟为54 MBps。 串行或非串行设备 串行SPI NOR闪存设备使用I2C,Microwire和SPI等协议与存储器接口。所有这些协议都使用一条/两条数据线来与设备接口。SPI协议的最新增强功能,例如引入了双模式,四模式和八进制模式以及执行DDR操作的能力,使SPI成为更高吞吐量的首选。SPI最初是由两根数据线和一条时钟线组成的三线协议,但是由于嵌入式设备对吞吐量的更高要求,各种供应商已经引入了新的多通道协议来改善设备的性能。  通过改进的SPI设备中还引入了双重数据速率协议,这进一步推动了吞吐量的界限。图1显示了SDR工作频率为108 MHz,DDR频率为133 MHz的各种SPI设备的吞吐量。新的SPI器件即将面市,它在SDR中提供高达133 MHz的频率支持,在DDR模式下提供80 MHz的支持,分别导致133MBps和160MBps的吞吐量。这些创新已大大缩小了并行和NOR闪存设备之间的差距,为高吞吐量要求的系统提供了一种低成本解决方案。 |

网友评论