ЭцзЊZynqСЌди20ЁЊЁЊЛљгкFPGAЕФФЃПщЛЏЩшМЦ

ЗЂВМЪБМфЃК2019-8-31 09:42

ЗЂВМепЃКrousong1989

|

ЭцзЊZynqСЌди20ЁЊЁЊЛљгкFPGAЕФФЃПщЛЏЩшМЦ ИќЖрзЪСЯЙВЯэ ЬкбЖЮЂдЦСДНгЃКhttps://share.weiyun.com/5s6bA0s АйЖШЭјХЬСДНгЃКhttps://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw ЬсШЁТыЃКld9c

ЬкбЖЮЂдЦСДНгЃКhttps://share.weiyun.com/5s6bA0s АйЖШЭјХЬСДНгЃКhttps://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw ЬсШЁТыЃКld9c ФЃПщЛЏЩшМЦЪЧFPGAЩшМЦжавЛИіКмживЊЕФММЧЩЃЌЫќФмЙЛЪЙвЛИіДѓаЭЩшМЦЕФЗжЙЄазїЁЂЗТецВтЪдИќМгШнвзЃЌДњТыЮЌЛЄЛђЩ§МЖИќМгБуРћЁЃ ШчЭМЫљЪОЃЌвЛАуећИіЩшМЦЙЄГЬЕФЖЅВуЮФМўРяжЛзіР§ЛЏЃЌВЛзіТпМДІРэЁЃШЛКѓвЛИіЖЅВуЯТУцЛсгаФЃПщAЁЂФЃПщBЁЂФЃПщCЕШЕШЃЌФЃПщA/B/CЯТгжПЩвдЗжЖрИізгФЃПщЪЕЯжЁЃ

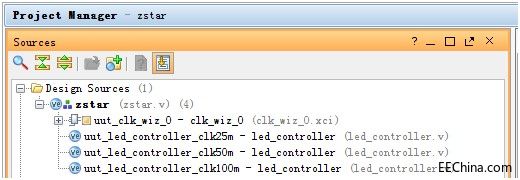

ЭМФЃПщЩшМЦЪОвтЭМ ШчДЫвЛРДЃЌОЭПЩвдНЋДѓЙцФЃИДдгЯЕЭГАДеевЛЖЈЙцдђЛЎЗжГЩШєИЩФЃПщЃЌШЛКѓЖдУПИіФЃПщНјааЩшМЦЪфШыЁЂзлКЯгыЪЕЯжЃЌВЂНЋЪЕЯжНсЙћдМЪјдкдЄЯШЩшжУКУЕФЧјгђФкЃЌзюКѓНЋЫљгаФЃПщЕФЪЕЯжНсЙћНјааећКЯМЏГЩЃЌОЭФмЭъГЩећИіЯЕЭГЕФЩшМЦЁЃ ФЃПщЛЏЩшМЦЕФЪЕЯжВНжшЪЧећИіФЃПщЛЏЩшМЦСїГЬжазюживЊЁЂзюЬиЪтЕФЃЌЫќАќКЌЃК ЁёГѕЪМдЄЫуЃЌБОНзЖЮЪЧЪЕЯжВНжшЕФЕквЛВНЃЌЖдећИіФЃПщЛЏЩшМЦЦ№зХжИЕМадЕФзїгУЁЃдкГѕЪМдЄЫуНзЖЮЃЌЯюФПЙмРэепашвЊЮЊЩшМЦЕФећЬхНјааЮЛжУВМОжЃЌжЛгаВМОжКЯРэЃЌВХФмЙЛдкзюДѓГЬЖШЩЯЬхЯжФЃПщЛЏЩшМЦЕФгХЪЦЃЛЗДжЎЃЌШчЙћвђВМОжВЛКЯРэЖјдкНЯКѓЕФНзЖЮашвЊдйДЮНјааГѕЪМдЄЫуЃЌдђашвЊЖдећИіЪЕЯжВНжшШЋУцЗЕЙЄЁЃ ЁёзгФЃПщЕФЩшМЦЪЕЯжЃЌдкИУНзЖЮЃЌУПИіЯюФПГЩдБВЂааЭъГЩИїздзгФЃПщЕФЪЕЯжЁЃ ЁёФЃПщЕФзюжеМЏГЩЃЌдкИУНзЖЮЯюФПЙмРэепНЋЖЅВуЕФЪЕЯжНсЙћКЭЫљгазгФЃПщЕФЪЕЯжНсЙћНјааећКЯМЏГЩЃЌЭъГЩећИіЩшМЦЕФЪЕЯжЁЃ ФЃПщЛЎЗжЕФЛљБОддђЪЧЃЌзгФЃПщЙІФмЯрЖдЖРСЂЃЌФЃПщФкВПСЊЯЕОЁСПНєУмЃЌЖјФЃПщМфЕФСЌНгОЁСПМђЕЅЁЃЖдгкФЧаЉФбвдТњзуФЃПщЛЎЗжзМдђЕФОпгаЧПФкВПЙиСЊЕФИДдгЩшМЦЃЌВЂВЛЪЪКЯВЩгУФЃПщЛЏЩшМЦЗНЗЈЁЃ ЯТУцвдzstar_ex03ЙЄГЬЕФЖЅВудДТыzstar.vЮЊР§ЃЌНВНтдкVerilogДњТыжаШчКЮЪЕЯжФЃПщЛЏЩшМЦЁЃдкzstar.vФЃПщЯТУцга4ИіФЃПщЃЌАќРЈ1ИіPLLЪБжгВњЩњФЃПщЃЌвдМА3ИіПижЦLEDЩСЫИЕФФЃПщЁЃ module zstar( input ext_clk_25m, //ЭтВПЪфШы25MHzЪБжгаХКХ output[2:0] led //LEDжИЪОЕЦНгПк ); //------------------------------------- wire clk_25m; //PLLЪфГі25MHzЪБжг wire clk_50m; //PLLЪфГі50MHzЪБжг wire clk_100m; //PLLЪфГі100MHzЪБжг wire sys_rst_n; //PLLЪфГіЕФlockedаХКХЃЌзїЮЊFPGAФкВПЕФИДЮЛаХКХЃЌЕЭЕчЦНИДЮЛЃЌИпЕчЦНе§ГЃЙЄзї clk_wiz_0 uut_clk_wiz_0 ( // Clock in ports .clk_in1(ext_clk_25m), // input clk_in1 // Clock out ports .clk_out1(clk_25m), // output clk_out1 .clk_out2(clk_50m), // output clk_out2 .clk_out3(clk_100m), // output clk_out3 // Status and control signals .reset(1'b0), // input reset .locked(sys_rst_n)); // output locked //------------------------------------- //25MHzЪБжгНјааЗжЦЕЩСЫИЃЌМЦЪ§ЦїЮЊ24ЮЛ led_controller #(24) uut_led_controller_clk25m( .clk(clk_25m), //ЪБжгаХКХ .rst_n(sys_rst_n), //ИДЮЛаХКХЃЌЕЭЕчЦНгааЇ .sled(led[2]) //LEDжИЪОЕЦНгПк ); //------------------------------------- //25MHzЪБжгНјааЗжЦЕЩСЫИЃЌМЦЪ§ЦїЮЊ25ЮЛ led_controller #(25) uut_led_controller_clk50m( .clk(clk_50m), //ЪБжгаХКХ .rst_n(sys_rst_n), //ИДЮЛаХКХЃЌЕЭЕчЦНгааЇ .sled(led[1]) //LEDжИЪОЕЦНгПк ); //------------------------------------- //25MHzЪБжгНјааЗжЦЕЩСЫИЃЌМЦЪ§ЦїЮЊ26ЮЛ led_controller #(26) uut_led_controller_clk100m( .clk(clk_100m), //ЪБжгаХКХ .rst_n(sys_rst_n), //ИДЮЛаХКХЃЌЕЭЕчЦНгааЇ .sled(led[0]) //LEDжИЪОЕЦНгПк ); endmodule Ёя гяЗЈвЊЕу зЂвтzstar.vФЃПщЕФДњТыжаР§ЛЏСЫ4ИізгФЃПщЃЌетЪЧвЛИіВЛелВЛПлЕФФЃПщЛЏЩшМЦЙЄГЬЁЃЯТУцЪЧЖдled_controller.vФЃПщЕФвЛИіР§ЛЏДњТыЁЃ led_controller #(24) uut_led_controller_clk25m( .clk(clk_25m), //ЪБжгаХКХ .rst_n(sys_rst_n), //ИДЮЛаХКХЃЌЕЭЕчЦНгааЇ .sled(led[2]) //LEDжИЪОЕЦНгПк ); вдЩЯУцетЖЮДњТыЮЊР§ЃЌФЃПщР§ЛЏДѓЬхгаЯТУцМИИівЊЕуЃК Ёё led_controllerЪЧдЪМЙЄГЬдДТыБОЩэЕФФЃПщУћГЦЁЃ Ёё uut_led_controller_clk25mЕФУћГЦЪЧПЩвдЫцвтЦ№ЕФЃЌжЛвЊВЛКЭвбгаЕФУћГЦжиУћМДПЩЃЌЫќБэЪОЮвУЧЖдЕБЧАР§ЛЏЙЄГЬled_controller.vЕФЮЈвЛЪЖБ№УћЁЃдкетИіЙЄГЬжаЃЌЮвУЧПДЕНled_controller.vФЃПщБЛР§ЛЏСЫЖрДЮЃЌЕЋЫќКЭuut_led_controller_clk25mЖдгІЮЛжУЕФУќУћЪЧВЛвЛбљЕФЃЌЖјЧвБиаыЪЧВЛвЛбљЕФЃЌБэЪОЙЄГЬжагаЖрИіЭъШЋвЛбљЕФЙІФмФЃПщЁЃетКЭШэМўГЬађРяУцЕФЕїгУВЛвЛбљЃЌШэМўГЬађгЩгкдЫааЦ№РДзмЪЧДЎааЕФЃЌЫљвдЖрДЮЕїгУЭЌвЛИіКЏЪ§ЪБЃЌетИіКЏЪ§ПЩвджЛеМвЛИіКЏЪ§ЫљашЕФЮяРэДцДЂПеМфМДПЩЃЛЕЋЪЧFPGAЪЧВЂааДІРэЕФЃЌЫќЕФФЃПщР§ЛЏЃЌФФХТЪЧЭъШЋвЛбљЕФФЃПщЃЌЭљЭљвВЪЧашвЊЖрИіЭъШЋвЛбљЕФЮяРэзЪдДгыгрЖдгІЕФЁЃ Ёё ЁА.clk(clk_25m),ЁБЪЧНгПкЕФгГЩфЃЌЁА.(),ЁБЪЧЙЬЖЈИёЪНЁЃclkЪЧled_controller.vФЃПщФкВПЕФНгПкЃЌclk_25mЪЧzstar.vФЃПщЕФНгПкЁЃ ШчЭМЫљЪОЃЌЕБЙЄГЬБрвыКѓЃЌЮвУЧБуПЩвддкЙЄГЬЙмРэДАПкжаПДЕНећИіЙЄГЬЕФФЃПщНсЙЙЁЃдкzstar.vФЃПщЯТУцЖдгІСЫ4ИізгФЃПщЁЃ

ЭМ at7_ex03ФЃПщНсЙЙ led_controller.vФЃПщДњТыШчЯТЁЃ module led_controller( input clk, //ЪБжгаХКХ input rst_n, //ИДЮЛаХКХЃЌЕЭЕчЦНгааЇ output sled //LEDжИЪОЕЦНгПк ); parameter CNT_HIGH = 24; //МЦЪ§ЦїзюИпЮЛ //------------------------------------- reg[(CNT_HIGH-1):0] cnt; //24ЮЛМЦЪ§Цї //cntМЦЪ§ЦїНјаабЛЗМЦЪ§ always @ (posedgeclk or negedgerst_n) if(!rst_n) cnt<= 0; else cnt<= cnt+1'b1; assign sled = cnt[CNT_HIGH-1]; endmodule |

ЭјгбЦРТл