勇敢的芯伴你玩转Altera FPGA连载74:基于SignalTap II的超声波测距调试之功能简介

发布时间:2018-6-6 16:23

发布者:rousong1989

|

勇敢的芯伴你玩转Altera FPGA连载74:基于SignalTap II的超声波测距调试之功能简介 特权同学,版权所有 配套例程和更多资料下载链接: http://pan.baidu.com/s/1i5LMUUD

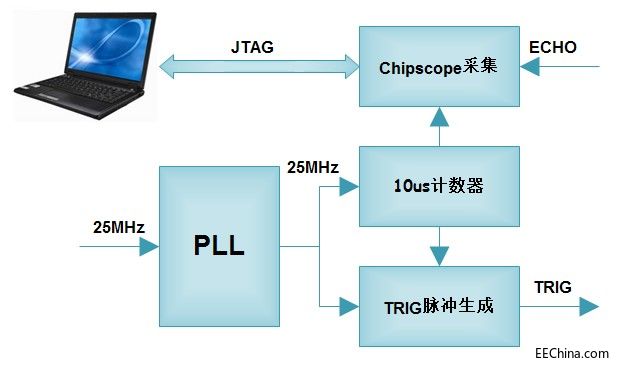

本实例的功能框图如图9.2所示。25MHz时钟来自PLL,它作为内部产生10us分频计数逻辑的基频时钟。10us脉冲直接输出到超声波测距模块的TRIG端口;用10us的时钟频率取采集超声波测距模块的回响信号ECHO,它通过SignalTap II内嵌逻辑分析仪来观察脉冲变化。SignalTap II内嵌逻辑分析仪则是通过JTAG线缆连接到PC的ISE软件中查看信号波形。

图9.2 超声波测距实例功能框图 在顶层模块cy4.v代码中,可以查看其RTL Schematic如图9.3所示。cy4.v模块主要定义接口信号以及对各个子模块进行互联。pll_controller.v模块例化PLL IP核,产生FPGA内部其它逻辑工作所需的时钟信号clk_25m和复位信号sys_rst_n;clkdiv_generation.v模块产生100KHz频率的一个时钟使能信号,即每10us产生一个保持单个时钟周期的高脉冲;ultrasound_controller.v模块每秒定时产生超声波测距模块脉冲的激励信号,即10us的高脉冲;此外,图中未示意,该工程实例还包括了一个名为sld_signaltap.v的IP核模块,该模块则引出工程代码中的某些接口信号,通过内嵌逻辑分析仪在线查看波形变化。

图9.3 超声波测距实例模块互联接口 该实例工程的代码模块层次如图9.4所示。

图9.4 超声波测距实例模块层次 本实例的超声波测距模块需要和我们的板子进行装配连接。如图9.5所示,在SF-CY4开发板的右上角插座P7用于连接超声波模块。

图9.5 超声波测距模块装配连接示意图 |

网友评论