高效率F类射频功率放大器的研究与设计

发布时间:2015-11-19 09:40

发布者:designapp

|

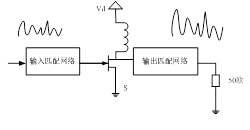

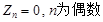

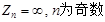

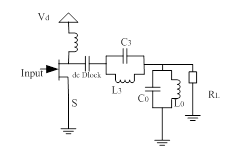

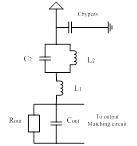

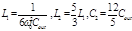

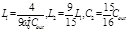

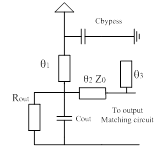

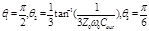

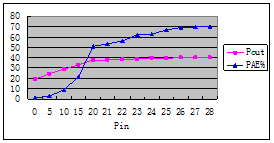

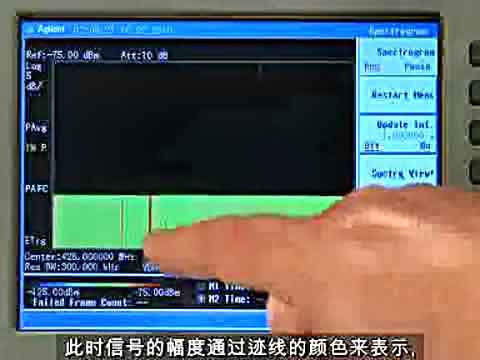

1 引言 射频功率放大器广泛应用于各种无线通信发射设备中,随着移动通讯服务的快速增长,对低耗、高效、体积小的要求也迅速增加。众所周知,RF功放(PA)是射频传输中功率损耗最大的众多设计模块之一。当前发展的第三代通信推动了对功放的更新,PA作为通信基站的核心部分,它的效率直接影响了整个基站的效率,因此研究解决功率放大器的效率问题成为当前研究的的热点。F类放大器理论效率可以达到100%,所以F类功率放大器具有很好的研究前景。 2 理想F类放大器原理研究 图1给出了功率放大器的基本结构,包含一个晶体管,直流源,输出匹配网络,输入匹配网络。直流偏置作为直流源,晶体管可以是FET或者是BJT,本文以FET为例来说明。晶体管漏极通过RF扼流圈接直流偏置电压Vd,通过输出网络匹配到50 Ohms最佳负载。  图1 功率放大器基本结构 F类放大器通过在输出匹配网络用谐波振荡电路,从而在漏极负载出现对偶次谐波短路和奇次谐波开路来实现效率和输出功率的共同推进。漏极电压由奇次谐波构成,接近方形波形。而漏极电流包含基波和偶次谐波,近似一个半正弦波。因为在漏极电压和电流之间没有交叠,理想效率可以达到100%。 器件漏极100%理想漏极效率的阻抗条件是:   实现F类放大器的工作电压和电流波形信号,可使用奇次谐波来近似方波,偶次谐波来近似半正弦电流波形,表达式如下:  其中,  电压波形达到最大值和最小值的中间点的位置分别在  和  。最小电压时的最大平坦度要求在  偶阶导数为0。由于  ,  为奇数时,奇阶导数等于0必须定义上式给出的电压波形的偶阶导数。 3 理论分析和设计方法 理想F类功放表现为包含无限的协波,但是在设计中是不切实际的。例如:漏级源电容Cds 将产生大量的高次谐波在微波频率短路。同样,漏级输出的寄生电容和电感使得几乎不可能生成偶次谐波短路和奇次谐波开路。通常,许多谐波进入输出网路需要实现在每个谐波频率的阻抗,这将产生一个很复杂的电路和更多的输出损耗,因此会使效率降低。由此,在很多设计中只考虑少量的谐波,如2,3次谐波。他们对输出能量和效率有很大的作用。 Raab 研究了输出功率性能和效率在有限谐波情况下的效果。这有助于设计师在设计时综合考虑输出网路的复杂程度和效率。表1 给出了不同谐波的最大效率,如我们看到的那样,A类功放的最大效率为50%,当只有基波频率时电流和电压m、n均为1,最大效率从50%向上增加到70.7,81.7,86.6,90.5依次为 2,3,4,5次谐波。mn 表示漏极电流和电压的最大谐波次数. 表1. F类功率放大器的最大效率 在只考虑2次和3次谐波的情况下,(3次谐波峰化),最大效率可以达到81.7%,包含3次谐波峰化输出网络电路如图2a所示,在3f0用并联的谐振器加在漏极输出,提供2f0 短路和3f0开路,另外一个并联谐振器与负载阻抗并联,用来保证在f0 有最佳的负载,RL是最佳的漏级负载。  (2a) 3次谐波输出网络       (2b) 图2 谐波输出网络 图2b中给出了另外两个可能的并联谐振器电路和连接谐振器电路构造元件的初始值。另外还给了一个等效的微带阻抗-峰化电路和他的初始原理值。能提供对于所有的偶次谐波短路和对3次谐波开路。然而,实际的F类PA的设计要复杂的多,因为有寄生电抗,非线性漏级电流Ids和非线性的Cgs,Cds图3 中给的方程可以提供一个很好的F类放大器设计的出发点。 4 设计实例 本文在设计F类放大器时,对输出谐波调谐,当输入网络在栅极输入提供共轭匹配时输出网络提供了偶次谐波短路和奇次谐波开路,输出匹配网络使在漏级输出端获得基波的最佳负载。图2b中的等效的微带阻抗—峰化电路,三段电长度中只有第二段需要根据晶体管的寄生参数来额外修正,其余都可根据基板参数和频率计算出实际微带线的尺寸。 设计采用Cree公司的GaN HEMT,基频1.25GHz,带宽为100MHz,输入功率28dBm, 基板材料Er=3.38,板厚0.4mm,输入网络是同频率B类工作模式下设计的,栅极电压VGS =-2.5V,漏极电压VDS=28V。ADS仿真结果最大PAE为84%,实现电路及测试架如图3所示。  图3 测试电路实物及测试架图 初步试验测量结果最大功率附加效率65.5%,通过进一步调节电路以及输入输出端电容得到PAE为70.32%。略低于仿真结果,但已经获得了较高的效率,效率偏低的原因有很多种,测量器件的改进以及对电路的再次调整可能会进一步有效的提高电路的效率。 本设计最终在中心频率1.25GHz实际测量所得结果如图4所示。与目前国内外高效率放大器相比,在保证输出功率的基础上实现了较高的效率,在F类放大器实现电路上取得了较好的成功。  图4 相对输入功率的输出功率和PAE 6 结束语 本文对F类功率放大器的理论进行了研究,分析了其电路工作原理和试验设计方法。并通过一种新型F类放大器的设计和试验证实了实现高效率,高功率工作的可能。实际测试中在没有进行调节的情况下已经达到65.5%的功率附加效率,由于在调节的过程中影响效率的因素没有准确的依据,故而调节过程难度较大,最终实现了PAE大于70%,输出功率达到10W。 |

网友评论